# **TECHNISCHE UNIVERSITÄT MÜNCHEN**

### Lehrstuhl für Realzeit-Computersysteme

# **Resource-Aware Automotive Control Systems Design**

# Wanli Chang

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

| Vorsitzender:            | Prof. DrIng. Gerhard Rigoll        |

|--------------------------|------------------------------------|

| Prüfer der Dissertation: | 1. Prof. Dr. Samarjit Chakraborty  |

|                          | 2. Prof. Anuradha Annaswamy, Ph.D. |

Die Dissertation wurde am 03.06.2016 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 17.08.2017 angenommen.

ii

# Abstract

As the automotive industry is entering the smart era through advances in sensing, computation, storage, communication, and actuation technologies, a larger number of more complex control applications with better performances are expected to be on board. This requires an implementation platform with abundant resources, which is undesired in the cost-sensitive automotive domain. The implementation platform, often embedded in an Electronic Control Unit (ECU) and shared by multiple applications to save the cost, is mainly comprised of a processor for computation, memory for storing instructions and data, and bus for internal and external communication. Conventionally, automotive control systems are designed using model-based approaches, where the details of the implementation platform are ignored. Techniques that integrate the characteristics of implementation resources into control algorithms design are largely missing. Such a separate design paradigm is too conservative in resources dimensioning and utilization for modern vehicles.

This thesis presents novel approaches in automotive control systems design that take implementation resources into consideration, aiming to improve the control performances for a given amount of resources, or equivalently, realize the required control performances with fewer resources. While communication resources have started to get explored in the literature of networked embedded control systems, the focus of this thesis is on memory and computation resources. As Electric Vehicles (EVs) have become a new trend in the automotive industry, energy resources of EVs, i.e., the batteries, are also investigated.

In the typical two-level memory hierarchy of an onboard embedded implementation platform, on-chip cache is the most costly component. A memory-aware sampling order, which is proposed to run each application consecutively multiple times instead of all applications in a conventional round-robin fashion, increases the cache reuse and improves control performances. In particular, two techniques are presented. First, a memory analysis technique is used to compute the guaranteed Worst-Case Execution Time (WCET) reduction due to the cache reuse between two consecutive runs of one application. Second, a controller design technique is tailored for non-uniform sampling with sensor-to-actuator delays shorter than or equal to the sampling periods, which results from the WCETs of the memory-aware sampling order. The approach to find the optimal sampling order that maximizes the overall control performance is reported.

On the embedded implementation platform often runs a Time-Triggered (TT) Operating System (OS) due to the safety-critical nature of automotive systems. Typically, a TT OS only supports a limited set of predefined periods, from which the sampling period of a feedback control application has to be chosen. For a given performance requirement, the optimal sampling period usually does not fall in this set, which forces the controller to be designed with a shorter sampling period than the optimal one — leading to an unnecessarily higher utilization of the computation resources. In this thesis, a novel multirate controller that switches between the available sampling periods offered by the TT OS is proposed, towards achieving an average sampling period closer to the optimal one. The benefit is a lower processor utilization, while the control performance requirement and the system constraints are still satisfied. The challenge lies in the performance-oriented controller design under the non-uniform sampling scheme with negligible sensor-to-actuator delays.

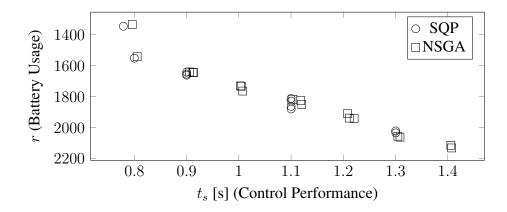

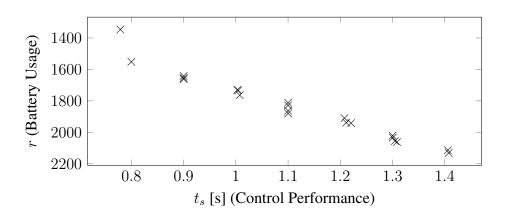

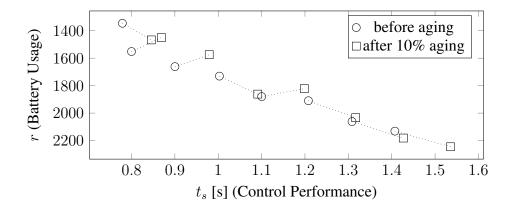

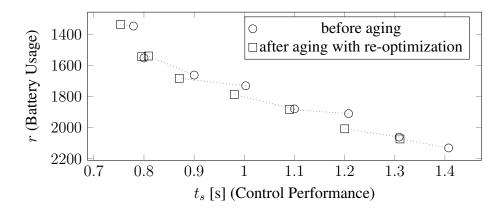

Battery is a key component of EVs. The effective battery capacity depends on the discharging current profile, which varies with different control strategies. For a given battery, it is desired to increase the battery usage while satisfying the control performance requirement. A novel optimization framework is proposed in this thesis to explore the Pareto front between battery usage and the control performance. Designers can then select the Pareto point according to the specific requirement and preference. As the processor in the embedded implementation platform ages, the sampling period of the feedback control application is prolonged. This leads to control performance deterioration, which is highly undesirable for safety-critical control applications in EVs. Using the same framework with slight modification, the controller is re-optimized to ensure that the control performance is kept with a modest compromise in the battery usage.

Throughout this thesis, state-feedback control applications with both linear and non-linear control law are considered and naturally robust to uncertainties. Several well-established optimization approaches are taken and novel optimization techniques are developed on top of them. The iterative interior-point method is deployed for convex problems. Particle Swarm Optimization (PSO) and gradient-based Sequential Quadratic Programming (SQP) are typically used to solve non-convex single-objective problems. The non-dominated sorting genetic algorithm (NSGA) is taken for non-convex multi-objective problems. A number of real-world applications that are detailed in the appendix validate the resource-aware automotive systems design techniques proposed in this thesis.

# Acknowledgements

I would like to express my gratitude to my supervisor, Prof. Samarjit Chakraborty, for offering me the opportunity to work with him on a number of exciting problems that eventually constitute this thesis. I am constantly surprised by his intelligence, creativity and sense of responsibility. I always feel fortunate to have his support and advice along the way.

I also thank Dr. Anuradha Annaswamy for hosting me at MIT. We had many interesting and insightful discussions that broadened my view of research.

Dr. Dip Goswami has been very helpful, especially in giving me technical suggestions in a number of occasions.

It was a great pleasure working with Dr. Jason Xue in Hong Kong, where I benefited from him and his group in knowledge building and skill development.

I appreciate that Prof. Gerhard Rigoll chaired my defense.

vi

# Contents

| Ał | ostract                                           |                            |                                             |    |  |  |

|----|---------------------------------------------------|----------------------------|---------------------------------------------|----|--|--|

| Ac | cknow                                             | ledgem                     | ents                                        | v  |  |  |

| 1  | Intr                                              | ntroduction                |                                             |    |  |  |

|    | 1.1                                               | Motiva                     | ation                                       | 3  |  |  |

|    | 1.2                                               | Resour                     | rces                                        | 5  |  |  |

|    |                                                   | 1.2.1                      | Communication Resources                     | 5  |  |  |

|    |                                                   | 1.2.2                      | Memory Resources                            | 6  |  |  |

|    |                                                   | 1.2.3                      | Computation Resources                       | 7  |  |  |

|    |                                                   | 1.2.4                      | Energy Resources                            | 9  |  |  |

|    | 1.3                                               | Organi                     | zation                                      | 10 |  |  |

|    | 1.4                                               | U                          | Publications                                | 11 |  |  |

| 2  | Mat                                               | Mathematical Background 13 |                                             |    |  |  |

|    | 2.1                                               |                            | l Theory                                    | 13 |  |  |

|    |                                                   | 2.1.1                      | Feedback Control Applications               | 13 |  |  |

|    |                                                   | 2.1.2                      | State-Feedback Control Law                  | 16 |  |  |

|    |                                                   | 2.1.3                      | Control Performance and Sampling Period     | 20 |  |  |

|    | 2.2                                               |                            |                                             |    |  |  |

|    |                                                   | 2.2.1                      | Interior-Point Method                       | 20 |  |  |

|    |                                                   | 2.2.2                      | Particle Swarm Optimization                 | 21 |  |  |

|    |                                                   | 2.2.3                      | Sequential Quadratic Programming            | 23 |  |  |

|    |                                                   | 2.2.4                      | Non-Dominated Sorting Genetic Algorithm     | 24 |  |  |

| 3  | Memory-Aware Automotive Control Systems Design 27 |                            |                                             |    |  |  |

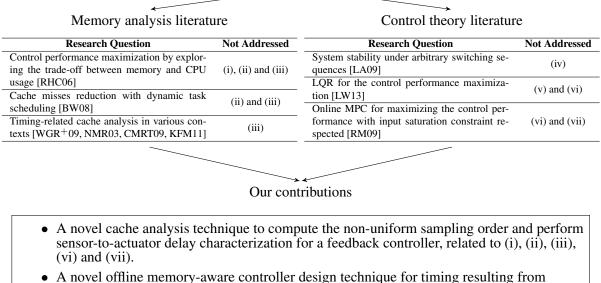

|    | 3.1                                               | Related                    | d Work                                      | 28 |  |  |

|    | 3.2                                               | Memor                      | ry Analysis                                 | 29 |  |  |

|    |                                                   | 3.2.1                      | Basic Definitions                           | 30 |  |  |

|    |                                                   | 3.2.2                      | Computation of Cache States                 | 31 |  |  |

|    |                                                   | 3.2.3                      | Guaranteed WCET Reduction                   | 33 |  |  |

|    | 3.3                                               | Control Timing Parameters  |                                             |    |  |  |

|    | 3.4                                               |                            | ller Design                                 | 37 |  |  |

|    |                                                   | 3.4.1                      | Controller Design with Uniform Sampling     | 37 |  |  |

|    |                                                   | 3.4.2                      | Controller Design with Non-Uniform Sampling | 38 |  |  |

#### CONTENTS

|    |                 | 3.4.3                                              | Pole-Placement with Hybrid PSO                  | 41  |  |  |

|----|-----------------|----------------------------------------------------|-------------------------------------------------|-----|--|--|

|    |                 | 3.4.4                                              | Comparison of Controller Design Methods         | 43  |  |  |

|    | 3.5             | -                                                  | al Sampling Order Computation                   | 44  |  |  |

|    | 3.6             | -                                                  | mental Results                                  | 47  |  |  |

|    | 3.7             | Remar                                              | ks                                              | 52  |  |  |

| 4  | Con             | omputation-Aware Automotive Control Systems Design |                                                 |     |  |  |

|    | 4.1             | Related                                            | d Work                                          | 56  |  |  |

|    | 4.2             |                                                    | VDX Operating System                            | 57  |  |  |

|    | 4.3             | Multira                                            | ate Controller Design                           | 58  |  |  |

|    |                 | 4.3.1                                              | Linear State-feedback Controller                | 59  |  |  |

|    |                 | 4.3.2                                              | Optimal Pole-Placement                          | 60  |  |  |

|    |                 | 4.3.3                                              | Alternative Controller Design for Scalability   | 62  |  |  |

|    |                 | 4.3.4                                              | Non-Uniform MPC                                 | 63  |  |  |

|    | 4.4             | Experi                                             | mental Results                                  | 64  |  |  |

|    | 4.5             | Remar                                              | ks                                              | 67  |  |  |

| 5  | Batt            | ery- and                                           | d Aging-Aware Automotive Control Systems Design | 69  |  |  |

|    | 5.1             | Related                                            | d Work                                          | 70  |  |  |

|    | 5.2             | Design                                             | Aspects of Electric Vehicles                    | 71  |  |  |

|    |                 | 5.2.1                                              | Battery Rate Capacity Effect                    | 71  |  |  |

|    |                 | 5.2.2                                              | Processor Aging in Embedded Control Systems     | 73  |  |  |

|    | 5.3             | Optimi                                             | zation Framework                                | 74  |  |  |

|    |                 | 5.3.1                                              | Battery-Aware Controller Design                 | 74  |  |  |

|    |                 | 5.3.2                                              | Optimization Techniques                         | 75  |  |  |

|    |                 | 5.3.3                                              | Battery- and Aging-Aware Controller Design      | 78  |  |  |

|    | 5.4             | Experi                                             | mental Results                                  | 78  |  |  |

|    | 5.5             | Remar                                              | ks                                              | 82  |  |  |

| 6  | Con             | clusion                                            |                                                 | 85  |  |  |

| Aŗ | opend           | lix                                                |                                                 | 89  |  |  |

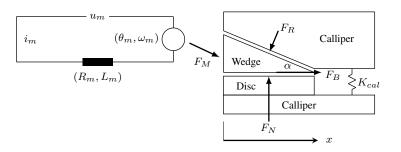

|    | A               | Electro                                            | onic Wedge Brake                                | 89  |  |  |

|    | В               | Servo l                                            | Motor Position Control                          | 91  |  |  |

|    | С               | Electri                                            | c Motor Control                                 | 91  |  |  |

|    | D               | Electro                                            | -Mechanical Braking System                      | 93  |  |  |

| Bi | bliogi          | raphy                                              |                                                 | 101 |  |  |

| Li | st of '         | Fables                                             |                                                 | 103 |  |  |

|    |                 |                                                    |                                                 | 105 |  |  |

| Li | List of Figures |                                                    |                                                 |     |  |  |

| Ał | Abbreviations   |                                                    |                                                 | 107 |  |  |

#### CONTENTS

#### Nomenclature

109

#### CONTENTS

# Introduction

Performance and reliability of automobiles are influenced by feedback control applications implemented on board. At the inception of the first horseless carriage, some form of control was already applied to motor vehicles. Engine idle speed control, which can be found in every modern vehicle powered by an Internal Combustion Engine (ICE), traces back to the Watt's governor in 1769. This device marking the origin of both feedback control and the industrial revolution can be viewed as a mechanical idle speed feedback controller for a steam engine [BBC<sup>+</sup>07].

Over the last century, control has been applied to almost every aspect of vehicle operation, from engine to drivetrain, from steering to braking. For instance, electronic powertrain control was introduced in automobiles in the 1970s, aiming to substantially reduce emissions. As a result, cars on the street today are 99% cleaner than they were when emission regulations were first introduced in the 1960s. Applications including Anti-Lock Braking System (ABS), traction control, Electronic Stability Control (ESC), and active safety systems have decreased the number and severity of accidents.

With advances in sensing, computation, storage, communication, and actuation technologies, more complex automotive control applications targeting better performances have emerged. In the combustion engine control, homogeneous charge compression ignition has been developed to reduce  $NO_x$  emission. These engines have a higher level of Exhaust Gas Recirculation (EGR), yet the involved control technique is more sophisticated due to the fragile combustion stability in load transients [CSJ07]. The level of EGR of conventional turbocharged diesel engines can be increased as well. The operating range of the engine is partitioned in [OdR07]. Linear models are identified for each partition and Model Predictive Control (MPC) is applied to take account of actuator saturation.

In the powertrain control, a Design for Six Sigma (DFSS) analysis approach is used to determine automatic transmission gear content, aiming at fuel consumption minimization for various powertrain systems [Rob14]. Conventional powertrain Active Noise Control (ANC) systems have difficulty in tracking the fast engine speed variations. A number of modified

Filtered-x Least Mean Squares (FxLMS) algorithms are reported in [SFX<sup>+</sup>15] to achieve a balanced noise reduction performance over a broad frequency range.

A unified chassis control strategy integrating Active Front Steering (AFS) and ESC is proposed in [CCK<sup>+</sup>12] to improve agility, maneuverability, and vehicle lateral stability. Integrated chassis control is also reported in [HJYK15] and [CLP<sup>+</sup>14] to enhance high speed cornering performance and on-center handling behavior, respectively. In [HJYK15], individual chassis control systems, such as ESC, Four Wheel Drive (4WD), Active Roll Control System (ARS), and Electronic Control Suspension (ECS), are involved. Various chassis modules are analyzed to verify the proposed integrated control strategy. In [CLP<sup>+</sup>14], MPC is used for optimal allocation of sub-chassis control systems.

Along the direction of autonomous driving, which can be classified into five levels depending on the extent of automation as follows [NHTSA13], new control applications have debuted in the modern premium cars.

- Level 0 (no automation): The driver is in complete and sole control of the primary vehicle controls (brake, steering, throttle, and motive power) at all times, and is solely responsible for monitoring the roadway and for safe operation of all vehicle controls. Vehicles that have certain driver support/convenience systems but do not have control authority over steering, braking, or throttle would still be considered "level 0" vehicles. Examples include systems that provide only warnings (e.g., forward collision warning, lane departure warning, blind spot monitoring) as well as systems providing automated secondary controls such as wipers, headlights, turn signals, hazard lights, etc.

- Level 1 (function-specific automation): Automation at this level involves one or more specific control functions; if multiple functions are automated, they operate independently from each other. The driver has overall control, and is solely responsible for safe operation, but can choose to cede limited authority over a primary control, the vehicle can automatically assume limited authority over a primary control, or the automated system can provide added control to aid the driver in certain normal driving or crash-imminent situations.

- Level 2 (combined-function automation): This level involves automation of at least two primary control functions designed to work in unison to relieve the driver of control of those functions. Vehicles at this level of automation can utilize shared authority when the driver cedes active primary control in certain limited driving situations. The driver is still responsible for monitoring the roadway and safe operation and is expected to be available for control at all times and on short notice. The system can relinquish control with no advance warning and the driver must be ready to control the vehicle safely.

- Level 3 (limited self-driving automation): Vehicles at this level of automation enable the driver to cede full control of all safety-critical functions under certain traffic or environmental conditions and in those conditions to rely heavily on the vehicle to monitor for changes in those conditions requiring transition back to driver control. The driver is expected to be available for occasional control, but with sufficiently comfortable transition time.

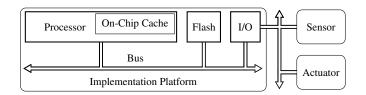

Figure 1.1: A typical embedded implementation platform for automotive control applications. The processor executes control programs. Instructions and data are stored in the flash memory. On-chip cache accelerates the memory access. Programmable I/O peripherals are used for communication with sensors and actuators.

• Level 4 (full self-driving automation): The vehicle is designed to perform all safetycritical driving functions and monitor roadway conditions for an entire trip. Such a design anticipates that the driver will provide destination or navigation input, but is not expected to be available for control at any time during the trip. This includes both occupied and unoccupied vehicles. By design, safe operation rests solely on the automated vehicle system.

Nowadays, most vehicles with autonomous features in the market fall into Level 1 or 2. For instance, Adaptive Cruise Control (ACC) enables the driver to cede limited authority over a primary control. Lane keeping automatically assumes limited authority over a primary control. Dynamic brake support provides added control to aid the driver in emergencies. Other emerging control applications include automated parking [MDG07], path tracking [Sni09], obstacle avoidance [VdNMP07], and vehicle control at friction limits [Kri12].

# 1.1 Motivation

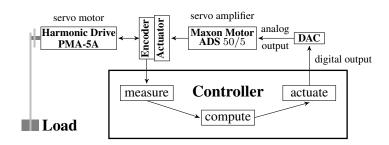

Automotive control applications are implemented on a platform embedded in an Electronic Control Unit (ECU). A feedback control loop has three operations:

- Measurement: Sensors measure the states of the physical plants. This is also called sampling.

- **Computation:** Taking the data from sensors, control programs are executed and compute the control input.

- Actuation: The control input is sent to actuators, aiming to achieve certain desired behavior of the plants.

A typical embedded implementation platform for automotive control applications is shown in Figure 1.1. There are often programs of multiple control applications executed on one processor, which necessitates an Operating System (OS) for coordination. The flash memory stores all instructions and data. The on-chip cache accelerates the memory access. Programmable Input/Output (I/O) peripherals are used for communication with sensors and actuators.

#### 1.1. MOTIVATION

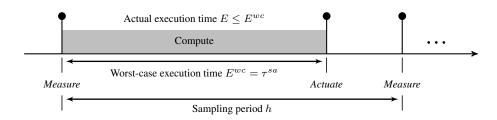

The implementation platform considerably impacts the control performances via, e.g., sampling periods and sensor-to-actuator delays. The sampling period is defined as the time duration between two consecutive measurements (or samplings) of the plant states under control. The sensor-to-actuator delay is defined as the time duration between the measurement and the actuation of one feedback control loop. If the processor or the memory access is not fast enough, the execution time of the control program might be too long to meet the desired sampling periods and sensor-to-actuator delays. Therefore, a larger number of more complex control applications calls for an implementation platform with abundant resources, which contradicts the cost-sensitive nature of the automotive industry.

The algorithms development for control applications from a control-theoretical perspective is well-established. The controller design methods can be drawn from a large pool of research and practical experience that have been accumulated in the control community. However, little attention has been paid to the embedded implementation platform. Control theorists and embedded system engineers make model-based assumptions of the other side. Since most control applications are safety-critical, such assumptions in this separate design paradigm are inevitably conservative to guarantee the required control performances. As a result, the resources on the embedded implementation platform, such as communication, computation and memory, are inefficiently utilized. This thesis presents new techniques in automotive control systems design that take implementation resources into consideration, aiming to improve the control performances for a given amount of resources, or equivalently, realize the required control performances with fewer resources.

Motivated by the increasing worldwide efforts to reduce Greenhouse Gas (GHG) emissions<sup>1</sup>, automotive manufacturers have been struggling in upgrading their ICEs. It is challenging to reduce emissions while keeping the engine performance. An alternative solution is an Electric Vehicle (EV). Another major advantage of an EV is its independence of fossil fuels<sup>2</sup>. Although the petrol price is quite low as this thesis is written, it might be hard to predict its future trend. Besides, the torque and noise performances of an electric motor are generally better than an ICE of the similar size at low speeds. Most major car manufacturers have presented their mass-produced EVs, including Nissan Leaf, BMWi3, Volkswagen e-Golf, Chevy Volt, and Tesla Model S.

One major issue that impedes the market acceptance of EVs is the range anxiety. The energy resource is the major factor determining the driving range of an EV. Given a fixed battery pack, it is desired to maximize the battery usage (i.e., maximize the effective battery capacity and minimize the energy consumption of a control task instance), which is directly related to the driving range. Different control strategies result in different discharging current profiles and the battery usage depends on the discharging current profile. This thesis investigates the control systems design in an EV taking the energy resource into consideration. The influence of

<sup>&</sup>lt;sup>1</sup>For instance, the U.S. Environmental Protection Agency (EPA) and the Department of Transportation's National Highway Traffic Safety Administration (NHTSA) have set standards to reduce GHG emissions and improve fuel economy that model years 2017-2025 cars and light trucks must reach 4.3 liters per 100 kilometers [Age12].

<sup>&</sup>lt;sup>2</sup>It is noted that both GHG emissions reduction and fossil fuels independence also depend on the way of electricity generation.

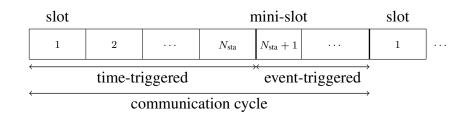

Figure 1.2: FlexRay bus with both time-triggered static and event-triggered dynamic segments

processor aging in the implementation platform on both the control performance and the battery usage is explored, and countermeasures are proposed.

## **1.2 Resources**

In this section, communication, memory, computation, and energy resources are described, where there have been a number of works on communication-aware embedded control systems design in the literature and the focus of this thesis is on the latter three types of resources.

#### **1.2.1** Communication Resources

The number of bits that can be transmitted per unit of time over a communication network is limited by the bandwidth. Precise characterization of the communication resources for automotive control systems is protocol-specific. The communication protocols are broadly classified into two groups — Event-Triggered (ET) and Time-Triggered (TT) networks. For instance, Controller Area Network (CAN) is ET and has been widely used since its first official release in 1986 [Bos91]. FlexRay, which was designed about a decade ago to be faster and more reliable than CAN, can be found in most premium cars [Fle05]. Media access control in FlexRay is based on communication cycles of equal and predefined length in time. Each communication cycle is divided into a TT static and an ET dynamic segment as shown in Figure 1.2. Messages can be sent with FlexRay over either the TT or ET segment using a bandwidth of 10 Mbit/s.

The TT static segment follows a Timing Division Multiple Access (TDMA) policy for media access control, where the entire segment is divided into multiple slots with the same predefined length in time. In every segment, slots are statically indexed starting from 1 to  $N_{\text{sta}}$ , which is the total number of TT slots in the static segment. Each application involved in the TT communication is assigned a dedicated index number and only uses the TT slot of this index to transmit messages. This allows a predictable temporal behavior, since in every communication cycle, an application is able to access the TT segment once, and the interval between two consecutive allowed transmissions is fixed. If no messages from an application need to be sent on its given slot, then the network is idle for this period of time, resulting in an inefficient utilization of bandwidth.

In the ET dynamic segment, media access control is priority-based and the entire segment is divided into mini-slots. Every application involved in the ET communication is associated with an index and in effect, a priority. In a segment, each mini-slot is dynamically assigned an

#### 1.2. RESOURCES

index. The starting index is  $N_{\text{sta}} + 1$ . The application matching the mini-slot index is allowed to transmit a message. A message can be transmitted over multiple mini-slots and the mini-slots transmitting the same message have the same index. After the transmission ends, the mini-slot index is incremented. If the message is not ready when its mini-slot starts, the mini-slot goes idle and the index is incremented. Since a mini-slot is typically much shorter than a TT slot, the ET segment offers more efficient utilization of bandwidth compared to the TT segment. The ET segment generally does not provide temporal guarantee due to its priority-based nature of arbitration. The timing of a message over ET communication depends on the presence of messages with higher priorities.

The research on networked control systems dates back to [HR88, Nil98, WYB99, ZBP01]. A number of recent efforts have been made to address the communication-aware embedded control systems design. An aperiodic strategy for dynamic allocation of bandwidth according to the current state of the plants and available resources is proposed in [AT09]. Control loops closed over CAN are discussed and illustrated on a train car. In [AGL15], an event-based control-scheduling co-design strategy involving a set of continuous-time linear time-invariant plants is proposed to address the challenges of variable communication delays, access constraints and resource constraints. In [SCEP09], communication delay and jitter resulting from complex timing behavior are considered. A method integrating controller design and message scheduling is developed to optimize the overall control performance. In [LWH<sup>+</sup>14], the network management problem is addressed to reduce communication jitter and improve control performance. A predictive compensator co-located with the actuator is proposed in [HSJ08] to deal with communication outages. When a new control command is not received, a replacement one based on the history of past control commands is suggested.

There are mainly two challenges in the communication-control co-design. First, the design space can be too large to be tractable. There are many parameters to determine in the design of the controller and the communication network. A combined design space can be difficult to handle. This is aggravated by the increase of system size. Second, the trade-off between the control performance and the communication resource utilization, which enables more design freedom, has not been explored. Some first efforts have been made in [RZC<sup>+</sup>16] to address these challenges.

#### **1.2.2 Memory Resources**

In the two-level memory architecture shown in Figure 1.1 (such as the XC23xxB Series microcontroller [Inf09] from Infineon that is popular in automotive systems), the flash memory has a large size and can thus store all the application programs and data, but experiences high read/write latencies (hundreds of processor cycles). The cache is faster with low read/write latencies (several processor cycles), but usually limited in size due to its high cost. It is assumed that the access times of cache and flash memory are  $t_c$  and  $t_m$ , respectively, where  $t_c \ll t_m$ . In this thesis, the focus is on instruction memory, since control applications are typically not data-intensive.

When a processor executes an instruction, it checks the cache first. If this instruction is located in the cache, it is a cache hit and the access time is  $t_c$ . If this instruction is not in the cache, the memory block containing it is fetched from the flash memory and then written into

cache. This is a cache miss and the access time is  $t_m$ . Afterwards, when the same instruction is called again by the processor, the access time is  $t_c$  if it is still in the cache without being replaced. This is a cache reuse.

A program usually has different execution paths resulting in different execution times. The Worst-Case Execution Time (WCET) is defined to be the maximum length of time a program takes to be executed. The WCET constrains the sampling period of a control application. There are two general methods to reduce the WCET of a program — increasing the cache size and/or cache reuse. In resource-aware automotive control systems design, it is desirable to minimize the cache size while satisfying the performance requirement, or equivalently, improve the performance for the given memory resources. Therefore, the cache reuse should be maximized.

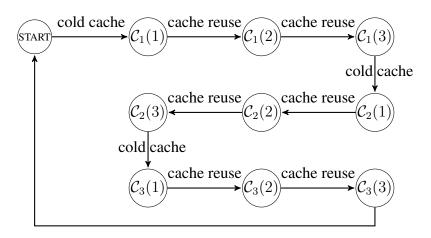

Given a collection of control applications (e.g.,  $C_1$ ,  $C_2$ ,  $C_3$ ), it is conventional to run the control loops of them in a round-robin fashion ( $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_1$ ,  $C_2$ ,  $C_3$ , ...). Since the codes for different control applications are different, the on-chip cache is frequently refreshed in this process. This results in poor cache reuse and long WCET. In order to address this issue, a new sampling order for the control applications is proposed, using which cache reuse is improved and the WCET of each application is reduced. In particular, a non-uniform sampling scheme is studied, where the control loop of each application is consecutively run multiple times — in order to increase cache reuse, before moving on to the next application.

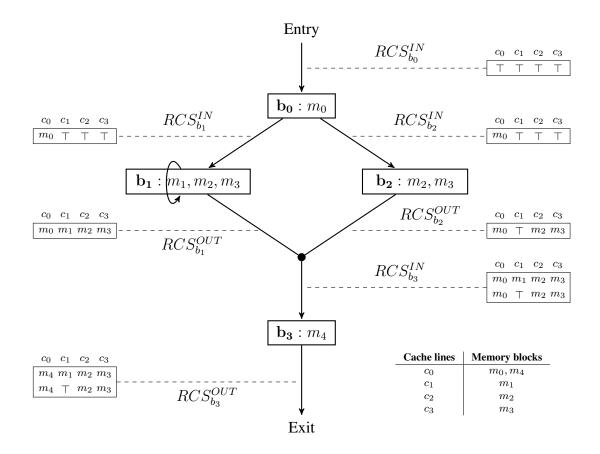

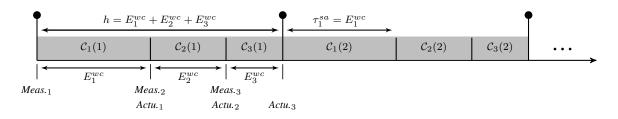

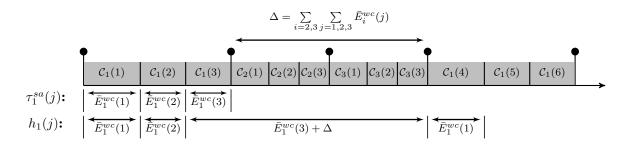

An example memory-aware sampling order  $(C_1(1), C_1(2), C_1(3), C_2(1), C_2(2), C_2(3), C_3(1), C_3(2), C_3(3), \cdots)$  is illustrated in Figure 1.3, where  $C_i(j)$  denotes the *j*th execution of the control application  $C_i$ . Before the first execution  $C_i(1)$ , the cache is either empty (i.e., cold cache) or filled with instructions from other applications, that are not used by  $C_i$  (equivalent to cold cache). The WCET of  $C_i(1)$  can be computed by a number of existing standard techniques [Wea08, AGS<sup>+</sup>13, WGR<sup>+</sup>09]. Before the second execution  $C_i(2)$ , the instructions in the cache are from the same application  $C_i$  and thus can be reused. This results in more cache hits and hence shorter WCET. Depending on which execution path the program takes, the amount of WCET reduction varies. Therefore, a technique is required to compute the guaranteed WCET reduction of  $C_i(2)$  and  $C_i(3)$  relative to  $C_i(1)$ , independent of the path taken.

Control parameters of the applications, such as sampling periods and sensor-to-actuator delays, can be derived from the WCET results. A controller must be tailored for the memory-aware non-uniform sampling orders, so that the control performance can be improved. In summary, two main techniques are required — (i) cache analysis to compute the guaranteed WCET reduction between two consecutive executions of one program; (ii) controller design for the non-uniform sampling with sensor-to-actuator delays shorter than or equal to the sampling periods. On top of showing that an example sampling order under memory-aware automotive control systems design results in better control performance, the approach to find the optimal sampling order that maximizes the overall control performance is reported.

#### **1.2.3** Computation Resources

For a given processor with a certain operating frequency, computation resources usually mean the available execution time. When multiple applications share one processor, in general, the performance of an application can be improved if it is allowed to access the processor for a longer period of time. Computation-aware automotive control systems design aims to reduce

Figure 1.3: An example memory-aware sampling order with three control applications. Each application is consecutively executed three times. After the first execution  $C_i(1)$ , some instructions in the cache can be reused and thus the WCETs of the following two executions are shortened.

the execution time of a control application, while still satisfying its performance requirement. In this way, more applications can be mapped to the processor, thereby saving the cost. This is the recent trend of ECU consolidation in the automotive industry.

Generally, a shorter sampling period allows the controller to respond to its plant more frequently, and is thus potentially able to achieve better control performance with an appropriately designed controller. The obvious downside is a higher processor utilization, which is defined to be the WCET of an application divided by its sampling period. This prevents more functions and applications from being integrated onto the processor. Therefore, the controller should use the largest possible sampling period that is able to fulfill the control performance requirement and satisfy the system constraints.

Due to the safety-critical nature of the automotive domain, TT OS usually runs on the processor. For instance, OSEK/VDX (Open Systems and Their Corresponding Interfaces for Automotive Electronics/Vehicle Distributed Executive) OS [Con05, Fei03] is widely used in automobiles and considered in this thesis. OSEK/VDX OS only offers a limited set of predefined periods, which implies that the sampling periods of control applications have to be taken from this set. In most cases, the optimal sampling period is not directly realizable on the OS. The conventional way to handle it is to use the largest sampling period offered by the OS that is smaller than the optimal one. This is a straightforward method, yet leads to a waste of computational resources. It is desirable to minimize the processor utilization of an application, while still satisfying the performance requirement.

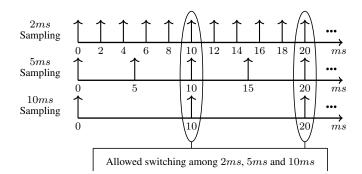

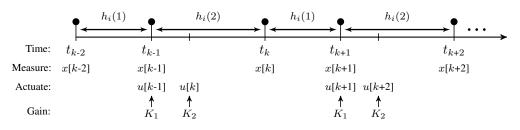

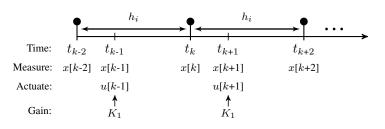

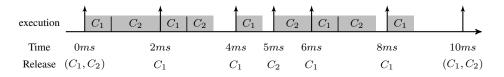

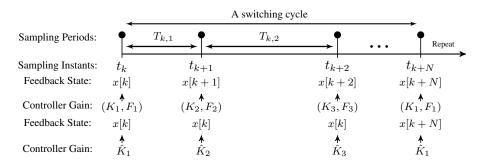

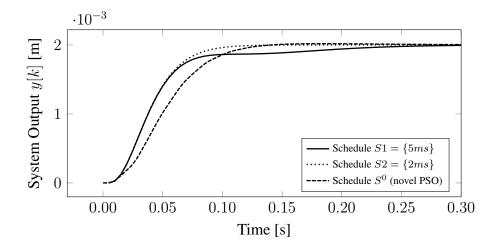

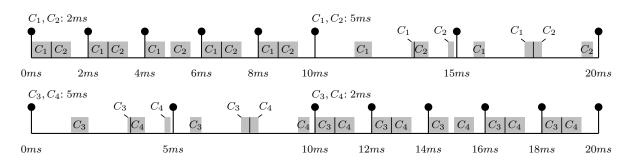

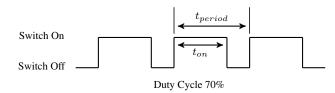

Towards this goal, a multirate controller that switches between available sampling periods offered by OSEK/VDX OS is proposed. A typical example with sampling periods of 2ms, 5ms and 10ms on OSEK/VDX OS is illustrated in Figure 1.4. Switching between two sampling periods can only occur at the common multiplier of them. For instance, switching between 2ms and 5ms is possible at the time instant of 10ms, 20ms, and so on. Therefore, possible sequences of sampling periods are  $\{2ms, 2ms, 2ms, 2ms, 5ms, 5ms, repeat\}$ ,

Figure 1.4: Allowed switching instants among multiple sampling periods

$\{5ms, 5ms, 10ms, repeat\}$ , and so on. The main challenge lies in the performance-oriented multirate controller design under the non-uniform sampling scheme with negligible sensor-to-actuator delays, aiming to reduce the processor utilization.

#### **1.2.4 Energy Resources**

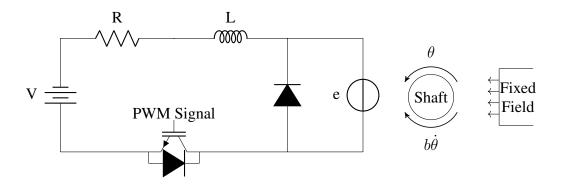

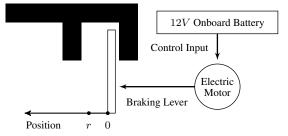

For all practical purposes, a longer driving range is desired in EVs to increase their usability. A battery pack with large capacity is needed to offer a long driving range. However, with larger capacity, the battery weight also increases leading to higher energy consumption. Moreover, the capacity is restricted by the space that can be allocated to the battery pack in EVs. One potential solution to the above problem is to design the controller in such a way that the energy consumption of a control task instance can be minimized.

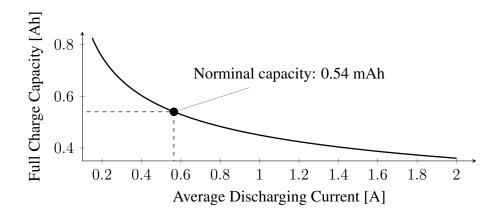

All off-the-shelf battery packs are labeled with a nominal capacity. However, due to the rate capacity effect, the effective capacity or Full Charge Capacity (FCC) of a battery pack, which is defined to be the amount of electric charges that can be delivered from the battery after it is fully charged, actually varies with different discharging current profiles [DS06, KQ11]. Generally speaking, larger discharging current tends to reduce the effective capacity. For most common lithium-ion batteries in the market, the capacity could potentially get significantly compromised if the rate capacity effect is not properly considered in the control systems design.

In this thesis, an optimization framework considering the control performance as one design objective and battery usage as the other is presented. The trade-off between these two design objectives is explored by generating a Pareto front. The battery usage is quantified by the number of times the control system can reach a steady state after a disturbance occurs powered up by a fully charged battery pack. In order to maximize the battery usage, the energy consumption of a control task instance, i.e., the disturbance rejection, should be small and the battery effective capacity should be increased by generating a battery-friendly discharging current profile.

In this context, the other important design aspect is processor aging. As a processor ages, the switching time of its transistors increases, resulting in longer path delays. On-chip monitors could be used to measure the delay of the critical path. It always has to be guaranteed that the signal transmission can be complete along any path within one clock cycle [LBS10]. Therefore, the processor operating frequency is reduced based on the new critical path delay.

#### 1.3. ORGANIZATION

As discussed above, a shorter sampling period can potentially provide a better control performance. Therefore, with a smaller processor operating frequency, the sampling period increases and the control performance gets deteriorated, which is dangerous and thus highly unwanted for safety-critical applications in EVs, such as electric motor control. To deal with the above situation, the same optimization framework can be slightly modified to re-optimize the controller with the longer sampling period, which results from processor aging, aiming to ensure that the control performance is kept with an inconsiderable compromise on battery usage.

## 1.3 Organization

This thesis comprises six chapters. Chapter 1 is the introduction. The mathematical background, including the necessary basics of control theory and optimization techniques, is presented in Chapter 2. Feedback control applications are first described, following which are the linear state-feedback control law and the non-linear MPC. The relationship between the control performance and the sampling period is shown based on an Electronic Wedge Brake (EWB) developed by Siemens [FRBW<sup>+</sup>07]. The presented optimization techniques include the iterative interior-point method, which can be deployed to solve convex problems, and Particle Swarm Optimization (PSO), gradient-based Sequential Quadratic Programming (SQP), and genetic algorithms for non-convex single- and multi-objective problems.

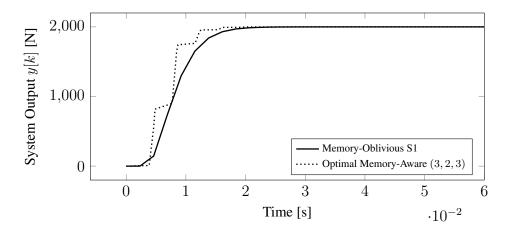

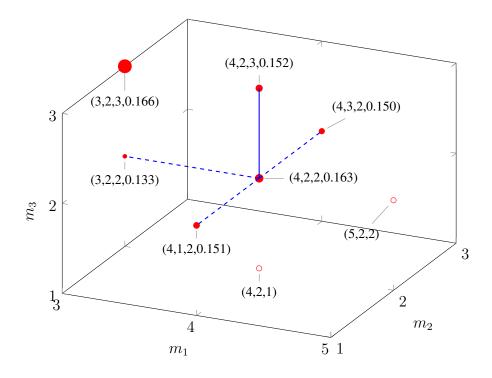

Chapter 3 discusses memory-aware automotive control systems design. The memory analysis technique that computes the guaranteed WCET reduction due to consecutive executions of one control program is first given. A motivational example is used for the illustration purpose. The control parameters, such as sampling periods and sensor-to-actuator delays, are then derived based on the WCET results. The controller design techniques for both the conventional memory-oblivious uniform sampling scheme and the proposed memory-aware nonuniform sampling scheme are elaborated. The approach to compute the optimal sampling order is explained. Experimental results are reported at the end of the chapter. Partial contents of this chapter are included in  $[CGC^+17]$ .

Chapter 4 discusses computation-aware automotive control systems design. The OS used in automobiles is described and the restriction on the choice of sampling periods is addressed. The multirate controller design technique is presented to reduce the processor load while satisfying the control performance requirement and system constraints. Contents of this chapter also appear in [CGCHng].

Chapter 5 discusses battery- and aging-aware automotive control systems design. The design objective of battery usage is introduced with battery characteristics. The processor aging and its influence on the control system is analyzed. Then the optimization framework and flow are shown. Experimental results can be found at the end of the chapter and have been published in [CPG<sup>+</sup>14].

The conclusion of this thesis is given in Chapter 6 and possible future work is discussed. All real-world applications used in this thesis are detailed in the appendix. Relevant information can also be found in  $[CFC^+16, CC16, CPG^+15]$ .

# **1.4 List of Publications**

Parts of the main contributions presented in this thesis appear in the following publications:

- Wanli Chang, Alma Pröbstl, Dip Goswami, Majid Zamani, Samarjit Chakraborty, *Battery-and Aging-Aware Embedded Control Systems for Electric Vehicles*, IEEE Real-Time Systems Symposium (RTSS), 2014.

- Wanli Chang, Dip Goswami, Samarjit Chakraborty, Jason Xue, Lei Ju, Sidharta Andalam, *Memory-Aware Embedded Control Systems Design*, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 36(4): 586-599, 2017.

- Wanli Chang, Dip Goswami, Samarjit Chakraborty, Arne Hamann, *OS-Aware Automotive Controller Design Using Non-Uniform Sampling*, ACM Transactions on Cyber-Physical Systems, forthcoming.

The following publications are generally related to the area of automotive control systems and implementation resources:

- Martin Lukasiewycz, Sebastian Steinhorst, Florian Sagstetter, **Wanli Chang**, Peter Waszecki, Matthias Kauer, Samarjit Chakraborty, *Cyber-Physical Systems Design for Electric Vehicles*, Euromicro Conference on Digital System Design (DSD), 2012.

- Martin Lukasiewycz, Sebastian Steinhorst, Sidharta Andalam, Florian Sagstetter, Peter Waszecki, **Wanli Chang**, Matthias Kauer, Philipp Mundhenk, Shreejith Shanker, Suhaib Fahmy, Samarjit Chakraborty, *System Architecture and Software Design for Electric Vehicles*, Design Automation Conference (DAC), 2013.

- Wanli Chang, Martin Lukasiewycz, Sebastian Steinhorst, Samarjit Chakraborty, *Dimensioning and Configuration of EES Systems for Electric Vehicles with Boundary-Conditioned Adaptive Scalarization*, IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), 2013. (Best Paper Nominee)

- Wanli Chang, Alma Pröbstl, Dip Goswami, Majid Zamani, Samarjit Chakraborty, *Reliable CPS Design for Mitigating Semi-Conductor and Battery Aging in Electric Vechicles,* IEEE International Conference on Cyber-Physical Systems, Networks, and Applications (CPSNA), 2015.

- Debayan Roy, Licong Zhang, **Wanli Chang**, Dip Goswami, Samarjit Chakraborty, *Multi-Objective Co-Optimization of FlexRay-based Distributed Control Systems*, IEEE Real-Time Embedded Technology & Applications Symposium (RTAS), 2016.

- Debayan Roy, Licong Zhang, **Wanli Chang**, Samarjit Chakraborty, *Automated Synthesis of Cyber-Physical Systems from Joint Controller/Architecture Specifications*, Forum on Specification & Design Languages (FDL), 2016.

#### 1.4. LIST OF PUBLICATIONS

- Wanli Chang, Debayan Roy, Licong Zhang, Samarjit Chakraborty, *Model-based Design* of *Resource-Efficient Automotive Control Software*, International Conference on Computer-Aided Design (ICCAD), 2016.

- Samarjit Chakraborty, Mohammad Abdullah Al Faruque, **Wanli Chang**, Dip Goswami, Marilyn Wolf, Qi Zhu, *Automotive Cyber-Physical Systems: A Tutorial Introduction*, IEEE Design & Test, 33(4): 92-108, 2016.

- Wanli Chang, Samarjit Chakraborty, *Resource-Aware Automotive Control Systems Design: A Cyber-Physical Systems Approach*, Foundations and Trends® in Electronic Design Automation, 10(4): 249-369, 2016.

- Wanli Chang, Licong Zhang, Debayan Roy, Samarjit Chakraborty, *Control/Archi-tecture Co-Design for Cyber-Physical Systems*, Handbook of Hardware/Software Codesign, Springer, 2017.

- S. Ramesh, Birgit Vogel-Heuser, **Wanli Chang**, Debayan Roy, Licong Zhang, Samarjit Chakraborty, *Specification, Verification and Design of Evolving Automotive Software*, Design Automation Conference (DAC), 2017.

- Michael Balszun, Debayan Roy, Licong Zhang, **Wanli Chang**, Samarjit Chakraborty, *Ef*fectively Utilizing Elastic Resources in Networked Control Systems, IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), 2017. (**Best Paper Award**)

- Debayan Roy, Licong Zhang, **Wanli Chang**, Sanjoy Mitter, Samarjit Chakraborty, *Ensuring Safety through Semantics-Preserving Co-Synthesis of Cyber-Physical Systems*, Proceedings of the IEEE, forthcoming.

Mathematical Background

The necessary mathematical background of this thesis includes the basics of the control theory and the optimization techniques. Feedback control applications are described from the state-space modelling, discretization and controllability, to control performance metrics and constraints. For the linear state-feedback control, the closed-loop system stability is analyzed. The feedback and feedforward gains are computed. The pole-placement technique is briefly discussed. For the non-linear MPC, both the unconstrained and constrained cases are considered. A small case study based on the EWB developed by Siemens is shown to illustrate the relationship between the control performance and the sampling period.

The novel optimization techniques proposed in this thesis are developed on top of four methods. The iterative interior-point method is used for convex problems. In particular, it solves the quadratic programming problem in the constrained MPC. PSO, gradient-based SQP and genetic algorithms are all deployed for the non-convex pole-placement problem. The general aim is to optimize the control performance, while respecting all constraints. In the context of battery-aware automotive control systems design, there is another objective — the battery usage — to optimize, which makes it a multi-objective optimization problem.

# 2.1 Control Theory

#### 2.1.1 Feedback Control Applications

**Plant dynamics:** A control application is responsible for controlling a plant or dynamic system. In particular, linear Single-Input Single-Output (SISO) control applications are considered, where the dynamic behavior is modelled by a set of differential equations,

$$\dot{x}(t) = Ax(t) + Bu(t),$$

$$y(t) = Cx(t),$$

(2.1)

where  $x(t) \in \mathbb{R}^l$  is the system state,  $\dot{x}(t)$  is the derivative of x(t) with respect to time, y(t) is the system output and u(t) is the control input. The number of system states is l. The system (or state) matrix is A. The input matrix is B. The output matrix is C. These matrices A, B and C are physical properties of the plant. System poles are eigenvalues of A. In a state-feedback control algorithm, u(t) is computed utilizing x(t) (feedback signals) and then applied to the plant, which is expected to achieve certain desired behavior.

**Discretized dynamics:** In most applications, the controller is implemented in a digital fashion on a computer. This implies that the system states must be sampled when measured by the sensors. Assuming the sampling period to be h, the sampled system state is denoted as

$$x[k] = x(t_k), \ t_k = kh, \ k = 0, 1, 2, 3, \cdots$$

(2.2)

Similarly, the sampled system output is

$$y[k] = y(t_k). \tag{2.3}$$

The control input taking discrete values is denoted as u[k], which is passed through a Zero-Order Hold (ZOH) and applied to the plant. The output of the ZOH is given by

$$u(t) = u[k], \ t_k \le t < t_{k+1}.$$

(2.4)

Now the discretized dynamics of (2.1) can be derived. First of all,

$$y[k] = y(t_k) = Cx(t_k) = Cx[k].$$

(2.5)

The solution to (2.1) is

$$x(t) = e^{A(t-t_0)}x(t_0) + \int_{t_0}^t e^{A(t-\tau)}Bu(\tau)d\tau.$$

(2.6)

Taking  $t_0 = t_k$  and  $t = t_{k+1}$ , since  $t_{k+1} - t_k = h$ ,

$$x[k+1] = e^{Ah}x[k] + \int_{t_k}^{t_{k+1}} e^{A(t_{k+1}-\tau)}Bu(\tau)d\tau$$

=  $e^{Ah}x[k] + \int_{t_k}^{t_{k+1}} e^{A(t_{k+1}-\tau)}d\tau Bu[k].$  (2.7)

Defining a new variable  $\tau' = t_{k+1} - \tau$ , there is  $d\tau' = -d\tau$ . As  $\tau$  ranges from  $t_k$  to  $t_{k+1}$ ,  $\tau'$  ranges from h to 0. Therefore,

$$\int_{t_k}^{t_{k+1}} e^{A(t_{k+1}-\tau)} d\tau B = \int_h^0 e^{A\tau'} (-d\tau') B = \int_0^h e^{A\tau'} d\tau' B.$$

(2.8)

Then, the discretized dynamics is

$$x[k+1] = A_d x[k] + B_d u[k],$$

$$y[k] = C x[k],$$

(2.9)

14

where

$$A_d = e^{Ah}, \ B_d = \int_0^h (e^{A\tau'} d\tau') B.$$

(2.10)

If A is invertible, the integral in  $B_d$  can be got rid of. Utilizing

$$\frac{d}{dt}e^{Ah} = e^{Ah}A,\tag{2.11}$$

$B_d$  can be derived to be

$$B_d = A^{-1} \int_0^h A e^{A\tau'} d\tau' B = A^{-1} e^{A\tau'} \Big|_{\tau'=0}^h B = A^{-1} (e^{Ah} - \mathbf{I}) B,$$

(2.12)

where **I** is the identity matrix.

System controllability: Controllability of a discrete system is defined as the ability to transfer the system from any initial state  $x[0] = x_0$  to any desired final state  $x[k_f] = x_f$ . Taking k = 1, 2, ..., n,

$$x[1] = A_d x[0] + B_d u[0]$$

$$x[2] = A_d x[1] + B_d u[1] = A_d^2 x[0] + A_d B_d u[0] + B_d u[1]$$

$$\vdots$$

$$x[n] = A_d^n x[0] + A_d^{n-1} B_d u[0] + \dots + B_d u[n-1].$$

(2.13)

x[n] can be written in a matrix form as

where  $CO = \begin{bmatrix} B_d & A_d B_d & \cdots & A_d^{n-1} B_d \end{bmatrix}$  is the square controllability matrix. If CO is non-singular, the unique solution for the control input sequence in (2.14) is given by

$$\begin{bmatrix} u[n-1] \\ u[n-2] \\ \dots \\ u[0] \end{bmatrix} = \mathcal{CO}^{-1}(x[n] - A_d^n x[0]).$$

(2.15)

In this case, for any  $x[n] = x_f$ , the solution in (2.15) determines the control input sequence that transfers the initial system state  $x_0$  to the desired system state  $x_f$  in n steps. It follows that the controllability condition is equivalent to the non-sigularity of the controllability matrix CO.

**Control performance:** Settling time is a widely used metric to quantify the control performance, especially for real-time control applications. The time it takes for the system output y[k] to reach and stay in a closed region around the reference value r (e.g., 0.98r to 1.02r) is

the settling time of a control loop and denoted as  $t_s$ . Shorter settling time implies better control performance.

Another popular performance metric in the control context is a quadratic cost function, which is given by

$$J = \sum_{k=0}^{N-1} [x^T[k]Qx[k] + u^T[k]Ru[k]], \qquad (2.16)$$

assuming that the system state x[k] is expected to stabilize at 0. Q is a positive semi-definite matrix and R is a positive definite matrix. Since SISO applications are considered in this thesis,  $u^{T}[k] = u[k]$ . In some cases, there is also a term  $x^{T}[N]Sx[N]$  added in the end, where S is a positive semi-definite matrix. Q, R and S are all weight matrices. To optimize the control performance, J is minimized. Among the three terms,

- $x^{T}[k]Qx[k]$  penalizes the transient state deviation;

- $u^{T}[k]Ru[k]$  penalizes the control effort;

- $x^T[N]Sx[N]$  penalizes the final state deviation.

System constraints: In almost every real-world system, due to the physical constraint of the actuator, there is some maximum available control input signal and the controller needs to be designed such that the maximum value of u[k] does not exceed this limit  $U_{max}$ , i.e.,  $u[k] \leq U_{max}$ . This is the constraint of the input saturation. Another constraint is on the peak overshoot, which is defined as

$$y_{max} - r \le \phi_0 r, \tag{2.17}$$

where  $y_{max}$  is the maximum system output and  $\phi_0$  is the overshoot threshold. The constraint on the steady-state error has been discussed when defining the settling time. The system output y[k] has to reach and stay in a closed region around r, i.e., the system has to settle. If the region is [0.98r, 1.02r], then the steady-state error tolerance  $\phi_e = 2\%$ . Besides, in many real-time control applications, there is a maximum allowed settling time  $t_s^0$  [LLB<sup>+</sup>12]. That is,  $t_s \leq t_s^0$ must be satisfied.

#### 2.1.2 State-Feedback Control Law

In the state-feedback control, the control input u[k] is computed based on the system state x[k]. There can be both linear and non-linear controllers, depending on the relationship between u[k] and x[k].

Linear controller: The general structure of a linear controller is as follows,

$$u[k] = Kx[k] + Fr, (2.18)$$

where K is the feedback gain and F is the feedforward gain. Clearly, the relationship between u[k] and x[k] is linear.

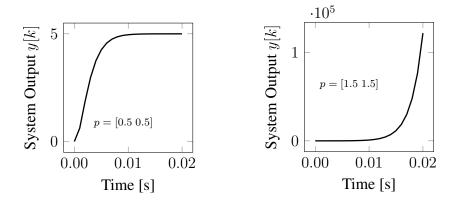

Figure 2.1: Different system ouput responses for stable and unstable poles

**Closed-loop system:** With the linear controller as shown in (2.18), the system dynamics in (2.9) becomes

$$x[k+1] = (A_d + B_d K)x[k] + B_d Fr, (2.19)$$

i.e., closed-loop dynamics.

**Pole-placement:** Different locations of closed-loop system poles, i.e., eigenvalues of  $(A_d + B_d K)$ , result in different system behaviors. In pole-placement, poles are placed in desired locations (eigenvalues are set) often to fulfill various high-level goals, such as control performance maximization and system constraints satisfaction. The desired poles p can be decided with empirical or optimization techniques. This method is feasible since there is the freedom to choose the feedback gain K.

Feedback and feedforward gain: Once pole locations are decided, the following characteristics equation of z can be constructed with these poles as roots:

$$z^{n} + \gamma_{1} z^{n-1} + \gamma_{2} z^{n-2} + \dots + \gamma_{n} = 0.$$

(2.20)

Then the following is defined,

$$\gamma_c(A_d) = A_d^n + \gamma_1 A_d^{n-1} + \gamma_2 A_d^{n-2} + \dots + \gamma_n \mathbf{I}.$$

(2.21)

According to Ackermann's formula [AU98], the feedback gain used to stabilize the closed-loop system is calculated as

$$K = \begin{bmatrix} 0 & \cdots & 0 & 1 \end{bmatrix} C O^{-1} \gamma_c(A_d).$$

(2.22)

The static feedforward gain F used to make the system output y[k] track the reference r is computed by

$$F = 1/(C_d(\mathbf{I} - A_d - B_d K)^{-1} B_d).$$

(2.23)

System stability: All eigenvalues of  $(A_d + B_d K)$  must have absolute values of less than unity in order to ensure system stability [AM09]. This is illustrated with a double integrator example as follows,

$$A = \begin{bmatrix} 0 & 1 \\ 0 & 0 \end{bmatrix}, B = \begin{bmatrix} 0 \\ 1 \end{bmatrix}, C = \begin{bmatrix} 1 & 0 \end{bmatrix}.$$

(2.24)

17

The initial state is  $\begin{bmatrix} 0 & 0 \end{bmatrix}$  and the reference value is 5. The sampling period is set as h = 0.001s. The system output responses for two sets of poles  $p = \begin{bmatrix} 0.5 & 0.5 \end{bmatrix}$  and  $p = \begin{bmatrix} 1.5 & 1.5 \end{bmatrix}$  are shown in Figure 2.1.

**Restricted pole-placement:** If the system is controllable, i.e., CO has full rank, there is no restriction on pole locations. The feedback gain K can be determined with (2.22). If CO does not have full rank, some of the poles cannot be modified with any choice of K and thus are uncontrollable. Since CO is not invertible, (2.22) does not work, either. In this case, if the uncontrollable poles are stable (with absolute values of less than unity), then the system is stabilizable. Restricted pole-placement can be used for stabilizable systems in the way that only controllable poles are placed in the desired locations and uncontrollable poles remain untouched. Therefore, for the automotive control systems design discussed in this thesis, the system is required to be at least stabilizable, if not controllable.

**Non-linear MPC:** In MPC, the relationship between the control input u[k] and the system state x[k] is non-linear. Considering the quadratic cost function in (2.16), the goal is to find a sequence of control inputs  $u[0], u[1], \ldots, u[N-1]$  that minimizes this cost function. Assuming that S = Q and expanding (2.16),

$$\begin{aligned} U &= x^{T}[0]Qx[0] + [x^{T}[1] \ x^{T}[2] \ \dots \ x^{T}[N]] \begin{bmatrix} Q & 0 & \cdots & 0 \\ 0 & Q & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & Q \end{bmatrix} \begin{bmatrix} x[1] \\ x[2] \\ \vdots \\ x[N] \end{bmatrix} \\ &+ [u^{T}[0] \ u^{T}[1] \ \dots \ u^{T}[N-1]] \begin{bmatrix} R & 0 & \cdots & 0 \\ 0 & R & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & R \end{bmatrix} \begin{bmatrix} u[0] \\ u[1] \\ \vdots \\ u[N-1] \end{bmatrix}. \end{aligned}$$

(2.25)

Computing the system states as

$$\begin{bmatrix} x[1] \\ x[2] \\ \vdots \\ x[N] \end{bmatrix} = \begin{bmatrix} B_d & 0 & \cdots & 0 \\ A_d B_d & B_d & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ A_d^{N-1} B_d & A_d^{N-2} B_d & \cdots & B_d \end{bmatrix} \begin{bmatrix} u[0] \\ u[1] \\ \vdots \\ u[N-1] \end{bmatrix} + \begin{bmatrix} A_d \\ A_d^2 \\ \vdots \\ A_d^N \end{bmatrix} x[0], \quad (2.26)$$

the quadratic cost function becomes

$$J = x^{T}[0]Qx[0] + (\bar{S}U + \bar{T}x[0])^{T}\bar{Q}(\bar{S}U + \bar{T}x[0]) + U^{T}\bar{R}U,$$

(2.27)

where

$$U = \begin{bmatrix} u[0] \\ u[1] \\ \vdots \\ u[N-1] \end{bmatrix}, \quad \bar{Q} = \begin{bmatrix} Q & 0 & \cdots & 0 \\ 0 & Q & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & Q \end{bmatrix}, \quad \bar{R} = \begin{bmatrix} R & 0 & \cdots & 0 \\ 0 & R & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & R \end{bmatrix},$$

$$\bar{T} = \begin{bmatrix} A_d \\ A_d^2 \\ \vdots \\ A_d^N \\ \vdots \\ A_d^N \end{bmatrix}, \quad \bar{S} = \begin{bmatrix} B_d & 0 & \cdots & 0 \\ A_d B_d & B_d & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ A_d^{N-1} B_d & A_d^{N-2} B_d & \cdots & B_d \end{bmatrix}.$$

(2.28)

Expanding (2.27),

$$J = x^{T}[0]Qx[0] + (U^{T}\bar{S}^{T} + x^{T}[0]\bar{T}^{T})\bar{Q}(\bar{S}U + \bar{T}x[0]) + U^{T}\bar{R}U$$

$$= \frac{1}{2}U^{T}2(\bar{S}^{T}\bar{Q}\bar{S} + \bar{R})U + 2x^{T}[0]\bar{T}^{T}\bar{Q}\bar{S}U + x^{T}[0](Q + \bar{T}^{T}\bar{Q}\bar{T})x[0].$$

(2.29)

Defining

$$H = 2(\bar{S}^T \bar{Q}\bar{S} + \bar{R}), \quad F = 2\bar{T}^T \bar{Q}\bar{S}, \quad Y = \bar{T}^T \bar{Q}\bar{T}, \tag{2.30}$$

there is

$$J = \frac{1}{2}U^{T}HU + x^{T}[0]FU + x^{T}[0]Yx[0].$$

(2.31)

It is clearly seen that this quadratic cost function J depends on the control input sequence U, for a given initial syste state x[0]. H, F and Y involve physical properties of the plant under control ( $A_d$  and  $B_d$ ) and the weights defined in the cost function (Q and R). It is important to note that H is semi-definite, since Q is positive semi-definite, R is positive definite, and S has full column rank.

**Solving unconstrained MPC:** If there are no constraints considered, computing the first derivative can be used to minimize the cost function (2.31). Solving

$$\frac{\partial J}{\partial U} = HU + F^T x[0] = 0, \qquad (2.32)$$

the optimal control input sequence is

$$U^* = -H^{-1}F^T x[0]. (2.33)$$

Since

$$\frac{\partial^2 J}{\partial U^2} = H,\tag{2.34}$$

is positive semi-definite, the obtained  $U^*$  in (2.33) is a minimum. If H is non-singular (i.e., positive definite), the optimal  $U^*$  is unique.

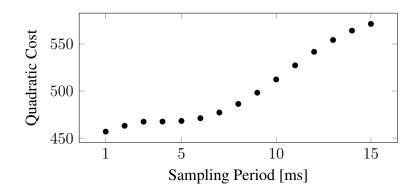

Figure 2.2: The relationship between the control performance and the sampling period for the EWB

**Solving constrained MPC:** In practice, there are often system constraints. For instance, the input saturation might require

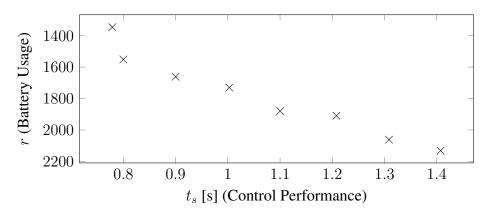

$$u_{min} \le u[k] \le u_{max}.\tag{2.35}$$

This is a constrained convex quadratic programming problem and can be solved by a number of optimization techniques. Both the active-set method and the interior-point method are widely used. In this thesis, the interior-point method is used and will be elaborated in the next section.

#### 2.1.3 Control Performance and Sampling Period

The relationship between the control performance and the sampling period is explored with the EWB described in Section A. The input saturation constraint is that the supplied voltage of the motor cannot exceed 12V. MPC is used in designing the control algorithm. The quadratic cost function as in (2.16) serves as the control performance metric. The term of the control input is excluded, since the input saturation is explicitly considered. The number of steps to look ahead N is set to be 4. The weight matrix Q is assumed to be an identity matrix. Varying the sampling period from 1ms to 15ms in integers, results are reported in Figure 2.2. It can be clearly seen that as the sampling period gets longer, the quadratic cost increases, which means that the control performance deteriorates. The underlying reason is that the controller is able to interact with the plant more frequently under a shorter sampling period.

# 2.2 Optimization Techniques

#### 2.2.1 Interior-Point Method

The interior-point method is widely used for convex optimization problems. In this thesis, it is taken to solve the quadratic programming problem in MPC with inequality constraints, which

is formulated as follows,

$$\min_{x} q(x) = \frac{1}{2} x^{T} G x + x^{T} d,$$

subject to

$Ax > b,$  (2.36)

where G is symmetric and positive semi-definite.

Specializing the general Karush-Kuhn-Tucker (KKT) conditions for constrained optimization [NW06], the necessary conditions for (2.36) can be obtained: If  $x^*$  is a solution of (2.36), there is a Lagrange multiplier vector  $\lambda^*$  such that the following conditions are satisfied for  $(x, \lambda) = (x^*, \lambda^*)$ ,

$$Gx - A^{T}\lambda + d = 0,$$

$$Ax - b \ge 0,$$

$$(Ax - b)_{i}\lambda_{i} = 0, \quad i = 1, 2, \dots, m,$$

$$\lambda \ge 0.$$

$$(2.37)$$

Introducing y = Ax - b, these conditions in (2.37) can be rewritten as

$$Gx - A^{T}\lambda + d = 0,$$

$$Ax - y - b = 0,$$

$$y_{i}\lambda_{i} = 0, \quad i = 1, 2, \dots, m,$$

$$(y, \lambda) \ge 0.$$

$$(2.38)$$

Since both the objective function and the feasible region are convex, these necessary conditions are also sufficient.

Defining

$$F(x, y, \lambda) = \begin{bmatrix} Gx - A^T \lambda + d \\ Ax - y - b \\ Y \Lambda e \end{bmatrix}, \quad (y, \lambda) \ge 0,$$

(2.39)

where

$$Y = \operatorname{diag}(y_1, y_2, \dots, y_m), \quad \Lambda = \operatorname{diag}(\lambda_1, \lambda_2, \dots, \lambda_m), \quad e = (1, 1, \dots, 1)^T,$$

(2.40)

Solving

$$F(x, y, \lambda) = 0, \quad (y, \lambda) \ge 0, \tag{2.41}$$

generates the optimal  $x^*$ . There are a number of iterative ways to solve (2.41), including Newton's method with slight modification [NW06] and Mehrotra's predictor-corrector algorithm [Meh92].

#### 2.2.2 Particle Swarm Optimization

PSO is a popular method to solve non-convex non-linear optimization problems and can be used to locate the poles that maximize the control performance. A group of particles are randomly

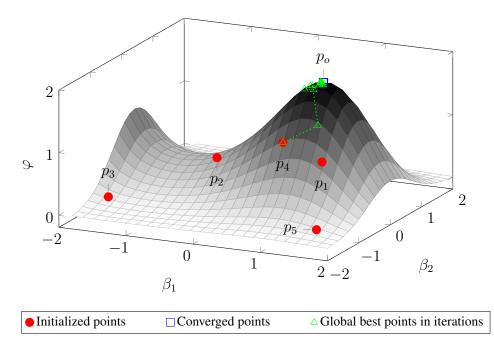

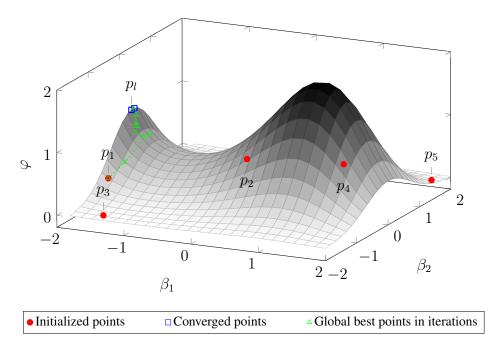

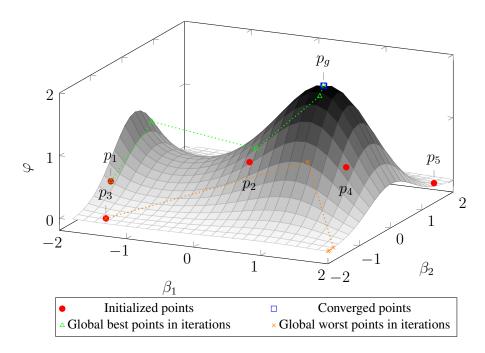

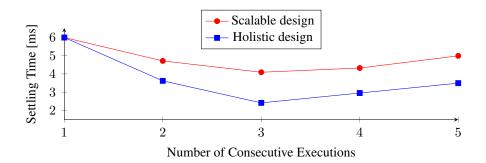

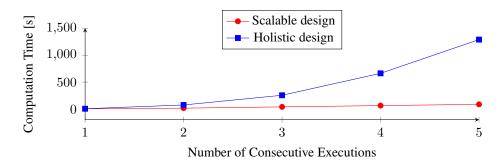

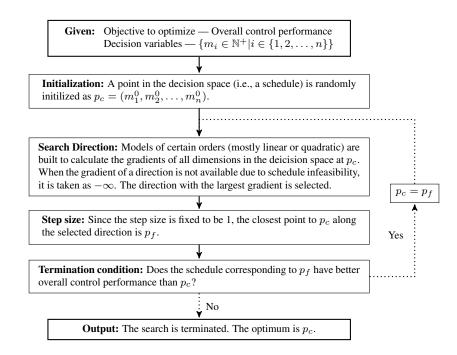

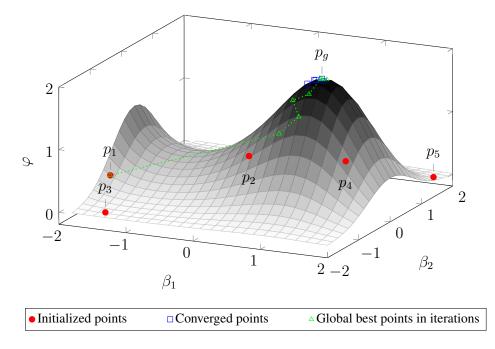

Figure 2.3: With the particle swarm optimization method, five particles are randomly initilized and converge to the optimum  $p_o$ .

initialized in the decision space with positions and velocities. They search for the optimum by iteratively updating their positions. The search is led by two points. The first is the local best point (in terms of the objective value) that has been reached by a particle. Every particle has its own local best point. The second is the global best point that has been reached by all particles.

The velocity of a particle is determined by the following equation,

$$V_{\text{new}} = \alpha_0 V_{\text{current}} + \alpha_1 \text{rand}(0, 1) (P_{\text{lbest}} - P_{\text{current}}) + \alpha_2 \text{rand}(0, 1) (P_{\text{gbest}} - P_{\text{current}}), \quad (2.42)$$

where  $V_{\text{new}}$  is the new velocity,  $V_{\text{current}}$  is the current velocity,  $P_{\text{current}}$  is the current position,  $P_{\text{lbest}}$  is the local best point of this particle and  $P_{\text{gbest}}$  is the global best point of all particles. rand(0, 1) is a random number with uniform distribution from the open interval (0, 1).  $\alpha_0$  is the weight inertia.  $\alpha_1$  and  $\alpha_2$  are cognitive and social scaling parameters. Widely used values for these parameters are

$$\alpha_0 = 0.4, \ \alpha_1 = \alpha_2 = 2, \tag{2.43}$$

which have been shown to have good performance in many optimization scenarios. The new position of this particle is

$$P_{\rm new} = P_{\rm current} + V_{\rm new}.$$

(2.44)

The algorithm is terminated once all particles have converged or the maximum number of iterations has been reached.

A numerical example is used to illustrate the PSO. The formulation is as follows,

$$\max_{\mathbb{D}} \varphi = e^{-\frac{1}{3}\beta_1^3 + \beta_1 - \beta_2^2}$$

subject to (2.45)

$$\mathbb{D} = \{ (\beta_1, \beta_2) | -1.8 \le \beta_1 \le 2, \ -2 \le \beta_2 \le 2 \}$$

22

where  $\beta_1$  and  $\beta_2$  are two continuous decision variables, constrained in the decision space  $\mathbb{D}$ . The objective to maximize is  $\varphi$ . As shown in Figure 2.3, five particles are randomly initialized at  $p_1$ ,  $p_2$ ,  $p_3$ ,  $p_4$  and  $p_5$ . After 22 iterations, all five particles converge to the points around the optimum  $p_o$  (1.0006, 0.0033, 1.9477). The path showing how the global best point evolves iteratively is drawn, with certain points that are too close to others omitted for better illustration.

#### 2.2.3 Sequential Quadratic Programming

SQP is a popular gradient-based optimization technique for single-objective non-convex problems. The entire process begins with a chosen starting point in the decision space, from which SQP searches for a sequence of points, hopefully closer and closer to the optimal point until either the optimal point is reached or termination criteria are satisfied. The question is then how to iteratively find the next point, which is supposed to be better than the current point in terms of the objective value. It needs to be known what is the search direction and how far to go along this direction. Neither of them is easy to compute for a non-convex problem with significant non-linearity. Therefore, an approximated local quadratic model is built around this current point as

$$f(x_p) = \frac{1}{2}x_p^T H x_p + c_q^T x_p,$$

(2.46)

where  $x_p$  is the current point.  $f(x_p)$  is the objective value, H is the symmetric Hessian matrix at  $x_p$ . Both  $c_q$  and  $x_p$  are column vectors with the same number of elements.

The search direction can be computed in various ways. For instance, the direction of steepest descent  $d_s$  with potentially the best local improvement in the objective value f can be used.  $d_s$  is the opposite of the gradient as,

$$d_{s} = -\frac{df}{dx_{p}} = -x_{p}^{T}H - c_{q}^{T}.$$

(2.47)

After computing the search direction, the next step is to determine how far to go in this direction. Assuming that  $\Delta$  is the radius of the region where the confidence in the accuracy of the approximated local quadratic model is high, a list of steps  $\{\frac{\Delta}{n_{ss}}, \frac{2\Delta}{n_{ss}}, \dots, \Delta\}$  are tried, where  $n_{ss}$ is the total number of steps and can be decided customarily. The step size with the best objective value f and all constraints fulfilled is chosen. Then a new quadratic model is established around this point and the search process is iterated. When no step size gives improvement in f, the optimization algorithm is terminated. The other termination criterion is that the set maximum number of iterations is exceeded. It is noted that solving the quadratic model in an exact manner as in Section 2.2.1 is not of much interest, since the model itself is only an approximation of the original problem in a restricted space. Instead, the aim is to compute the search direction and the step size that locally find a next point better than the current point.

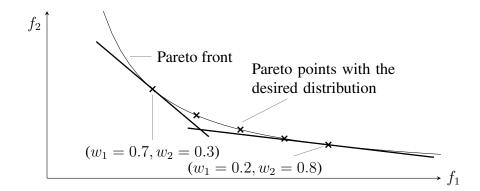

SQP is originally meant for single-objective optimization problems, yet can also be extended to multi-objective optimization problems, where all objectives are converted into one. One common way to do so is constructing a new objective  $f_0$  to be minimized with a weighted sum of all objectives. Taking two objectives  $f_1$  and  $f_2$  as as an example,

$$f_0 = w_1 \times f_1 + w_2 \times f_2, \tag{2.48}$$

23

where  $w_1$  and  $w_2$  are weights of the two objectives  $f_1$  and  $f_2$  and

$$w_1 + w_2 = 1. (2.49)$$

In multi-objective optimization, if a point is worse than another point in every objective, it is said to be dominated. If a point is not dominated by any other point in the feasible decision space, then this point is called a Pareto point. There can be multiple Pareto points, which form the Pareto front. If SQP is able to reach the global optimum, when  $f_0$  in (2.48) is minimized as the objective, the solution point must be on the Pareto front. This can be proven by contradiction. If there is another point x', which dominates the solution point  $x_0$ , then

$$f_1(x') < f_1(x_0), \quad f_2(x') < f_2(x_0).$$

(2.50)

From (2.48),

$$f_0(x') < f_0(x_0). \tag{2.51}$$

This contradicts that  $x_0$  is the global optimum for minimizing  $f_0$ .

#### 2.2.4 Non-Dominated Sorting Genetic Algorithm

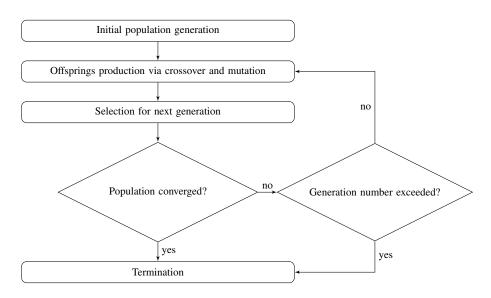

There is a variety of stochastic methods developed to solve non-convex optimization problems. Among them, the Non-Dominated Sorting Genetic Algorithm (NSGA) mimicking the process of natural selection is widely applied to deal with multiple objectives [SD94]. The second version of NSGA has three advantages over its predessor: (i) the computational complexity of non-dominated sorting is reduced; (ii) elitism speeds up the performance; (iii) the sharing parameter is no longer needed [DPAM02]. The entire flow of NSGA is illustrated in Figure 2.4, consisting of four major steps — initilization, genetic operation, environmental selection, and termination.

At first, an initial population is generated. This process is often random. Offsprings are then produced with genetic operators including mainly crossover and mutation. The crossover function tries to keep the good genes of parents, which generally means that the offsprings are close to parents in the decision space. The mutation function deviates from parents and produces offsprings in unexplored regions of the objective space. It is not necessary that an offspring only has two parents, as inspired in biology. The population is now composed of these offsprings.

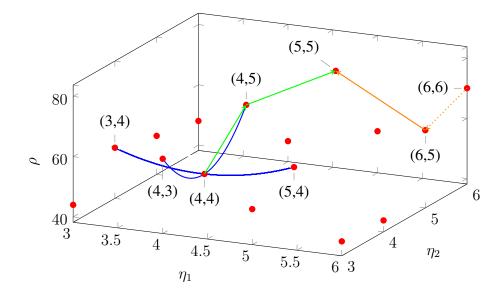

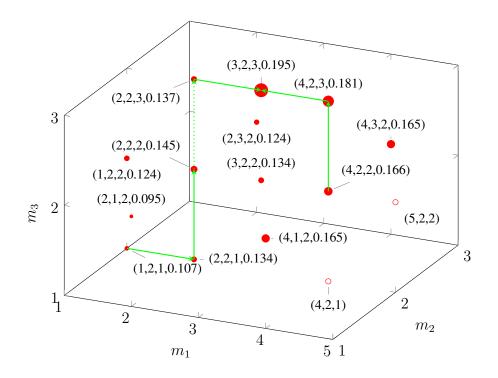

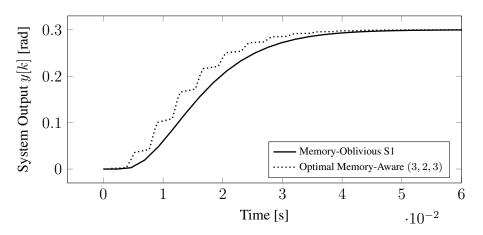

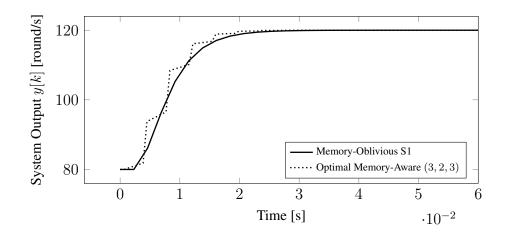

During each successive generation including this one, a proportion of the existing population is selected as parents to breed a new generation. Individual solutions are selected through a fitness-based process, where fitter solutions as measured by a fitness function are typically more likely to be selected. Certain selection methods rate the fitness of each solution and preferentially select the best solutions. Other methods rate only a random sample of the population, as the former process may be very time-consuming. The optimization objective function is often used for fitness evaluation. In some problems, it is hard or even impossible to explicitly define the fitness expression and a simulation may be used to determine the fitness function value.