# Technische Universität München Fakultät für Mathematik Lehrstuhl für Angewandte Geometrie und Diskrete Mathematik

# Circuit diameters

# and their application to transportation problems

## Elisabeth Finhold

Vollständiger Abdruck der von der Fakultät für Mathematik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. Jürgen Richter-Gebert

Prüfer der Dissertation: 1. Univ.-Prof. Dr. Raymond Hemmecke

2. Prof. Dr. Jesús A. De Loera University of California, Davis (USA)

3. Univ.-Prof. Dr. Rüdiger Schultz Universität Duisburg-Essen

Die Dissertation wurde am 20.11.2014 bei der Technischen Universität München eingereicht und durch die Fakultät für Mathematik am 19.02.2015 angenommen.

# **Circuit diameters**

and their application to transportation problems

ELISABETH FINHOLD

## Zusammenfassung

In dieser Arbeit führen wir den Zirkuit-Durchmesser (circuit diameter) ein, eine Verallgemeinerung des kombinatorischen Durchmessers von Polyedern. Wir untersuchen, wie viele Zirkuit-Schritte wir brauchen um je zwei Ecken eines Polyeders mit einem Zirkuit-Weg zu verbinden. Diese Wege verlaufen entlang von Zirkuit-Richtungen, das heißt, parallel zu potentiellen Kanten des Polyeders. Indem wir fordern, dass die Zirkuit-Wege zusätzliche Kriterien erfüllen, ergeben sich diverse Kategorien von Zirkuit-Durchmessern. Wir setzen all diese Klassen zueinander in Relation, wodurch eine Hierarchie von Durchmessern entsteht. Diese Vielzahl miteinander verwandter Konzepte ermöglicht es uns, neue Erkenntnisse über den kombinatorischen Durchmesser zu gewinnen. Beispielsweise bilden schwächere Zirkuit-Durchmesser untere Schranken an den kombinatorischen Durchmesser.

Wie man all diese Zirkuit-Durchmesser-Konzepte konkret ausnutzen kann, zeigen wir am Beispiel von Transportpolytopen und dualen Netzwerkfluss-Polyedern. Wir beweisen obere und untere Schranken an die verschiedenen Durchmesser, wobei wir besonderes Augenmerk auf die Schranke legen, die in Verbindung mit der berühmten Hirsch-Vermutung steht.

## **Abstract**

The present thesis introduces the circuit diameter of polyhedra as a generalization to the combinatorial diameter. It tells us how many circuit steps we need to connect any two vertices of a polyhedron with a circuit walk. Such a walk goes along circuit directions, that is, every step is parallel to a potential edge of the polyhedron. Several notions of circuit diameters arise from putting further restrictions on these walks. We relate all these categories in a comprehensive hierarchy. Therein, the generalized diameters reveal some interesting lower bounds for the combinatorial diameter and thus their study might help for a better understanding of the latter one.

By investigating the hierarchy for transportation polytopes and dual network flow polyhedra, we demonstrate on two concrete examples how one can exploit the availability of diameters of different strength. In this we focus on proving upper and lower bounds on the several circuit diameters, where the bound induced by the famous Hirsch conjecture is of special interest.

## **Acknowledgments**

First and foremost, my thanks go to my adviser Prof. Raymond Hemmecke for his guidance and advice in the past years, for putting trust in me, supporting and encouraging me, and for giving me the opportunity to work on the idea of the circuit diameter that turned out to be a great topic for my thesis.

I want to thank my co-authors Steffen Borgwardt, Jesús A. De Loera, Raymond Hemmecke, and Jake Miller for the enjoyable collaboration. Thank you for all the significant results we achieved and I may use in this thesis. Special thanks go to Prof. De Loera for inviting me to UC Davis this year. I experienced a great time and I took great benefit from it, as it gave rise to important parts of my thesis. Further, I would like to thank Steffen for all his valuable hints and comments.

I very much appreciate the pleasant environment at Technische Universität München at the department of Prof. Gritzmann and thanks to the TopMath program. I am certainly grateful that I got the chance to do research at this early point. The people involved in the TopMath always were a great help - Agnieszka Baumgärtel, Prof. Brokate, Carl-Friedrich Kreiner, and Denise Lichtig, only to name a few. I acknowledge the support from the graduate program TopMath of the Elite Network of Bavaria and the TopMath Graduate Center of TUM Graduate School at Technische Universität München.

But above all, my deepest thanks go to my family and close friends for their steady support and trust, for all the words of cheer and their never-ending patience and understanding — DANKE —

# **Contents**

| Int | trodu | ction    |                                                                      | 1  |

|-----|-------|----------|----------------------------------------------------------------------|----|

| 1   | Circ  | uits     |                                                                      | 7  |

|     | 1.1   | Defini   | tion and fundamental properties                                      | 8  |

|     | 1.2   | Circuit  | ts as optimality certificates                                        | 9  |

|     | 1.3   | Furthe   | r characterizations of circuits                                      | 11 |

|     | 1.4   | Examp    | ples                                                                 | 12 |

| 2   | A hi  | erarchy  | y of circuit distances                                               | 17 |

|     | 2.1   | Defini   | tions and preliminaries                                              | 18 |

|     |       | 2.1.1    | Circuit walks                                                        | 18 |

|     |       | 2.1.2    | Categories of circuit distances and circuit diameters                | 18 |

|     |       | 2.1.3    | Fundamental observations                                             | 21 |

|     | 2.2   | The ci   | rcuit distance hierarchy                                             | 24 |

|     | 2.3   | Upper    | bounds on circuit diameters                                          | 37 |

|     | 2.4   | The ci   | rcuit distance hierarchy in dimension two                            | 38 |

| 3   | Circ  | uit diar | meter bounds for transportation polytopes                            | 45 |

|     | 3.1   | Prelim   | inaries                                                              | 47 |

|     | 3.2   | Upper    | bounds on circuit diameters of $M \times N$ transportation polytopes | 51 |

|     | 3.3   | Upper    | bounds on the combinatorial diameter                                 | 51 |

|     |       | 3.3.1    | Basic concepts for the proofs                                        | 51 |

|     |       | 3.3.2    | $2\times N$ transportation polytopes                                 | 54 |

|     |       | 3.3.3    | $3\times N$ transportation polytopes                                 | 59 |

|     | 3.4   | Upper    | bounds on the circuit diameter                                       | 64 |

|     |       | 3.4.1    | $2\times N$ transportation polytopes                                 | 64 |

|     |       | 3.4.2    | $3\times N$ transportation polytopes                                 | 66 |

|     | 3 5   | Lower    | bounds on circuit diameters of $M \times N$ transportation polytones | 70 |

| 4   | Circuit diameter bounds for dual network flow polyhedra |                                                                               |     |  |

|-----|---------------------------------------------------------|-------------------------------------------------------------------------------|-----|--|

|     | 4.1                                                     | Preliminaries                                                                 | 74  |  |

|     | 4.2                                                     | The bipartite case: Circuit diameter bounds for dual transportation polyhedra | 78  |  |

|     |                                                         | 4.2.1 Preliminary results                                                     | 79  |  |

|     |                                                         | 4.2.2 Linear upper bounds on circuit distances                                | 80  |  |

|     | 4.3                                                     | Upper bounds on circuit diameters                                             | 85  |  |

|     | 4.4                                                     | Lower bounds on circuit diameters                                             | 89  |  |

| Out | tlook                                                   | <b>C</b>                                                                      | 95  |  |

| Bib | liog                                                    | raphy                                                                         | 101 |  |

## Introduction

An optimization problem over a polyhedron can be solved via a simple augmentation scheme: As long as the current solution is not optimal, improve it! The essential ingredient for such an algorithm is a *test set*, a set of vectors that contains an augmenting direction for every non-optimal solution. Such a set is also called an *optimality certificate*, as we have found the optimum if we can no longer improve our current solution along any vector in the test set.

In this thesis we consider a particularly interesting test set, the *circuits* [14, 15, 28]. These vectors are associated with the polyhedron that defines the feasible region of a linear program. They allow a particularly nice, intuitive interpretation: We will see that for a polyhedron of the form

$$P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \le \mathbf{d} \}$$

the circuits are given by all potential edge directions that appear as the right-hand sides  $\mathbf{b}$  and  $\mathbf{d}$  vary. Consequently, all these polyhedra, that result from translating the defining hyperplanes, admit the same set of circuits.

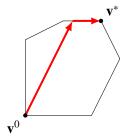

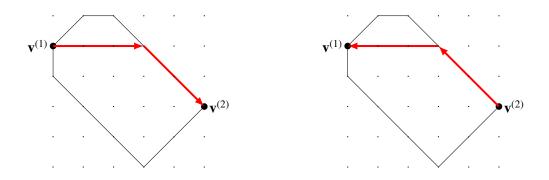

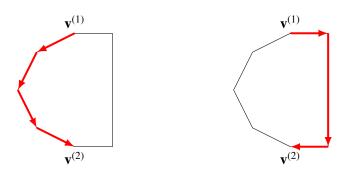

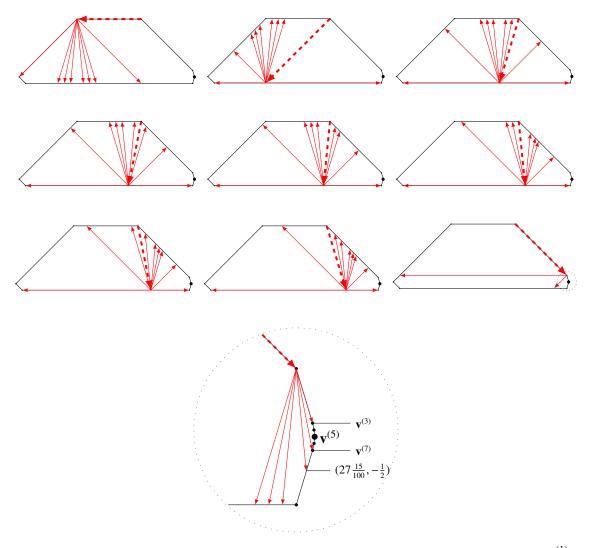

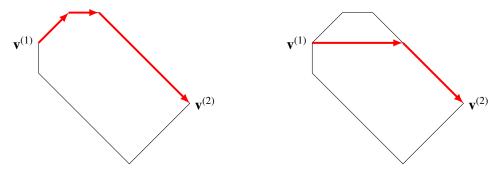

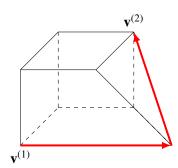

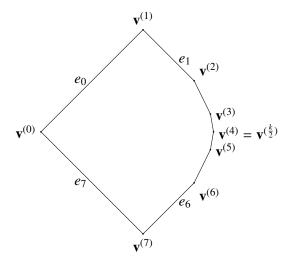

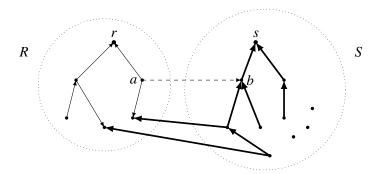

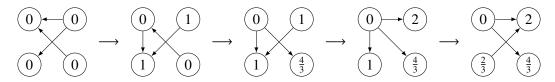

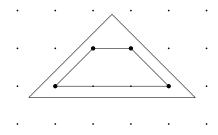

Using the circuits as a test set creates a path from an initial vertex  $\mathbf{v}^0$  to an optimal vertex  $\mathbf{v}^*$  of the associated optimization problem, illustrated in Figure 1. Observe that every augmenting direction is parallel to an edge and thus a circuit. We call a sequence of (not necessarily monotonic) circuit steps that connects two vertices of a polyhedron a circuit walk.

Figure 1: A circuit walk to the optimal vertex.

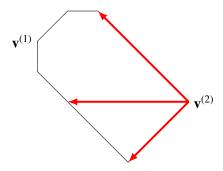

An immediate question is the following: Starting at any vertex of the polyhedron, how many augmentation steps do we need to reach an optimal vertex? It is not hard to see that in the example depicted in Figure 1 we could have used far less steps, see Figure 2.

Figure 2: A shorter circuit walk to the optimal vertex.

In [10] it was recently shown that the number of augmentation steps is bounded by the number of circuits if we always use a steepest-descent circuit direction and apply a step of maximum length. This thesis is concerned with the question of how many circuit steps we need to an optimal vertex of the polyhedron if we assume a 'perfect' selection rule. In this we even disregard monotonicity of the paths with respect to a certain objective function. In an attempt to answer this question, we introduce and study different types of *circuit diameters* of polyhedra.

Among these categories we will also recover the combinatorial diameter. This is a classical field of research in the theory of linear programming as it is of interest in the context of a best-case performance of the Simplex algorithm. The *Simplex method* is a well-known special case of augmentation algorithms along circuits: Every augmenting step goes along an actual edge of the polyhedron, from one vertex to a better one. We call such a sequence of steps an *edge walk*. The *combinatorial diameter* is the maximum number of edges we need to connect any two vertices of the polyhedron, and hence it is a lower bound on the number of steps the Simplex algorithm might take. It is still open whether there is a polynomial upper bound on the combinatorial diameter and thus whether there is hope for a pivot rule for the Simplex algorithm that takes only polynomially many steps. The connection to the Simplex algorithm becomes even more direct when investigating the *monotone* diameter. Here we consider monotone edge-walks, visiting vertices of non-decreasing objective values with respect to a certain linear functional.

One of the most famous problems associated with the combinatorial diameter is the *Hirsch conjecture*. In 1957, Warren M. Hirsch suggested an upper bound of f - d on the combinatorial diameter any d-dimensional polyhedron with f facets [8]. Only ten years later, Klee and Walkup showed that the conjecture does not hold for unbounded polyhedra of dimension  $\geq 4$  [21]. This led to the bounded version of the Hirsch conjecture, claiming an upper bound of f - d on the combinatorial diameter of *polytopes*. It was a long-standing open question, until Santos recently came up with the first counterexample in dimension 43 with 86 facets and diameter at least 44 [27]. Nevertheless, in the past decades validity of the Hirsch conjecture was proved for certain classes of polyhedra, such as (0,1)-polytopes [24], dual transportation polyhedra [1] and special combinations of the dimension d and the number of facets f (see [20] for a survey). However, despite great efforts the Hirsch conjecture remains open for most classes of polyhedra; even the more general polynomial Hirsch conjecture, asking only for a polynomial diameter bound in d and

## f. Yet, the latter one is not disproved either!

Being confronted with these long-standing open question in the context of the combinatorial diameter, we have to look out for new approaches. Introducing the circuit diameter as a generalization to the combinatorial diameter might help for a better understanding of this difficult field.

The present thesis is concerned with the very foundations of the circuit diameter, based on our definitions and results in [3] and [5]. Furthermore, it contains a demonstration of these concepts by considering transportation polytopes [4] and dual network flow polyhedra [5, 6].

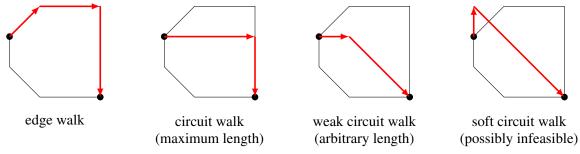

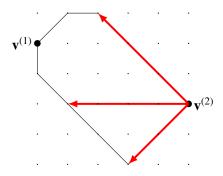

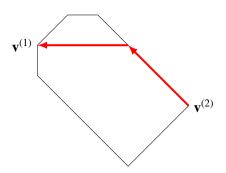

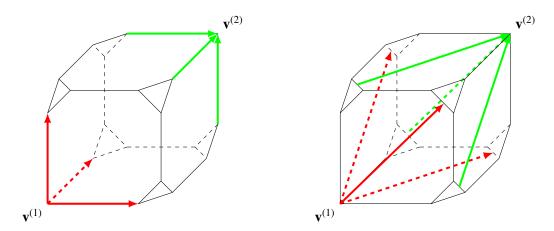

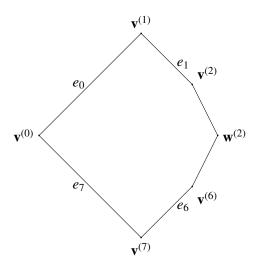

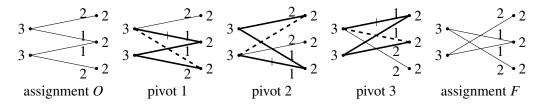

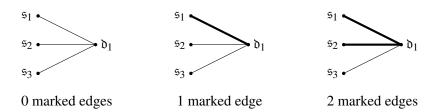

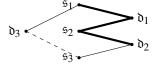

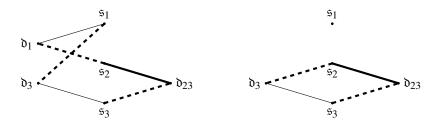

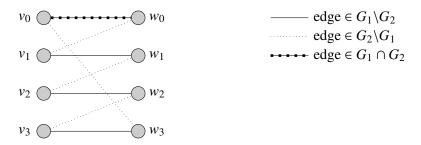

Let us now have a closer look at the general ideas behind the different types of circuit diameters. To define these notions, we extend the very specific edge walks related to the combinatorial diameter to different kinds of circuit walks between the vertices of the polyhedron (as already seen in Figure 1 and Figure 2 in the context of circuit augmentation algorithms). While the former only use the *actual edges* of the polyhedron and thus never leave its boundary, the latter ones go along *potential edge directions*, the circuits. In particular, a circuit walk may enter the interior of the polyhedron, which possibly yields fewer steps. Figure 3 illustrates four different types of circuit walks in a two-dimensional polytope that arise from imposing or relaxing certain restrictions on the circuit steps as stated below the respective images.

Figure 3: Four different types of circuit walks.

The first picture shows a traditional edge walk, but for the other examples we liberate ourselves from the stringent conditions of edge walks by allowing to leave the boundary of the polyhedron.

In the second picture we see a circuit walk that uses *maximum length steps*, that is, we always go along the circuit directions as far as possible, potentially also through the interior of the polyhedron. Our original definition of the circuit diameter in [5] is based on this kind of walks. The third and fourth picture depict even more general circuit walks, which we introduced in [3]. On *weak circuit walks* we skip maximality of the steps but we stay inside the polyhedron. In contrast, we can even leave the polyhedron along circuit directions on a *soft circuit walk*. These four main types of circuit walks are complemented by some more specific ones that arise from forbidding repeated and backwards steps, or asking for sign-compatible walks [3].

Now, every such type of circuit walk induces a circuit distance: The *circuit distance* from one vertex to another one is the minimum number of steps of a corresponding circuit walk, and the *circuit diameter* of a polyhedron is the maximum circuit distance among its vertices. Note that

each notion of circuit diameter can be seen as an indication for a best-case performance of circuit augmentation algorithms with corresponding properties.

We are particularly interested in how all these different circuit diameters are related. We answer this question in a comprehensive hierarchy of circuit distance concepts. The diameters associated with the four types of circuit walks in Figure 3 form the 'key chain' of this hierarchy: Note that the circuit walks become less restrictive from the left to the right and thus the corresponding distances trivially bound each other. In particular, the combinatorial diameter is an upper bound on all these circuit diameters, as an edge walk is just a special kind of circuit walk. On the other hand, the less restrictive notions provide some interesting lower bounds on the combinatorial diameter. What makes this so useful is the fact that the weaker categories are typically much easier to compute. Also, we often find similarities in the approaches for tackling the combinatorial and the 'original' circuit diameter. For these reasons, the availability of circuit diameter concepts of varying strength is an extremely valuable tool.

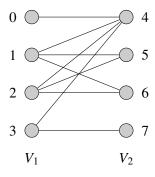

We demonstrate and exploit this by discussing the hierarchy for two families of polyhedra: *Transportation polytopes* and *dual network flow polyhedra*. These well-known problems are frequently used in combinatorial optimization to model a variety of problems.

Transportation problems [12, 13, 22, 29] describe the distribution of some product from M supply locations to N demand locations under minimum costs. Even though they are among the most fundamental problems in mathematical programming, it is still open whether the Hirsch conjecture holds for transportation polytopes; currently the best upper bounds are linear.

In contrast, the Hirsch conjecture is known to be true for *dual transportation polyhedra* [1]. This motivates the investigation of the other notions of circuit diameters for such polyhedra. In addition, we aim at generalizing the results to the case of *dual network flow polyhedra*, which are associated to minimum-cost flows through a network.

When studying these two families of polyhedra we focus on proving upper and lower bounds on the main categories of circuit diameters. For both types of polyhedra we easily obtain upper bounds on the weak and on the soft circuit diameter, which are actually tight. On the other hand, when investigating the two stronger diameter categories we often obtain only rough upper bounds unless we restrict ourselves to special cases. Typically, the combinatorial diameter is even more involved than the 'original' circuit diameter. However, our studies of the circuit diameter serve as a basis for addressing the combinatorial diameter, we often use similar approaches when proving upper or lower bounds on these notions of diameter.

### Structure of the thesis and main results

In Chapter 1 we introduce circuits as the most fundamental notion of this thesis. We summarize all definitions and results we need for the forthcoming discussions and illustrate them on some elementary examples.

Chapter 2 is the core part of the thesis. Here we formally introduce the different categories of

circuit walks, circuit distances and circuit diameters, as already initiated in the introduction. We then relate them to each other, resulting in our hierarchy. We also provide and discuss general upper bounds, in particular we show that the weaker categories of circuit diameter satisfy the bound induced by the Hirsch conjecture. Finally, we study the circuit diameter concepts in dimension two where we can refine our previous results. This is joint work with Steffen Borgwardt, Jesús A. De Loera and Raymond Hemmecke [3, 5].

In the last two independent chapters we investigate the 'key chain' of the hierarchy for two particular classes of polyhedra. In this we aim at upper and lower bounds on these diameters, where the bound induced by the Hirsch conjecture is of particular interest.

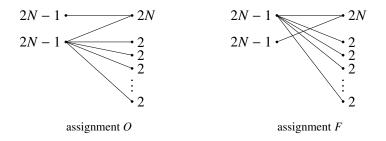

In Chapter 3 we consider the transportation polytopes. We prove that the Hirsch conjecture holds for  $2\times N$  and  $3\times N$  transportation polytopes. For the  $2\times N$  case can even prove the monotone Hirsch conjecture with a slightly stronger bound. We obtain similar results for the circuit diameter, but the discussion itself reveals some specifics of this diameter category. For the general  $M\times N$  transportation polytopes we show that the weak and the soft circuit diameter satisfy the Hirsch bound and that this bound is indeed tight. This is joint work with Steffen Borgwardt, Jesús A. De Loera and Jake Miller [4].

In Chapter 4 we then turn to dual network flow polyhedra. We prove linear bounds in the special case of dual transportation polyhedra. In the general setup of dual network flow polyhedra, we show that the weak and soft circuit diameter remain linear, while we prove quadratic upper bounds for the stronger categories. This is joint work with Steffen Borgwardt and Raymond Hemmecke [5, 6].

The thesis concludes with an outlook concerning future work and open questions on the circuit diameter. In particular, we emphasize a potential extension of circuit diameters to an integral setting of lattice points in a polyhedron.

# Chapter 1

## **Circuits**

We now start with a thorough introduction of the circuits, which are the most fundamental notion of this thesis: All chapters hereafter are based on this set of vectors. The circuits are associated with integral matrices  $A \in \mathbb{Z}^{m_A \times n}$  and  $B \in \mathbb{Z}^{m_B \times n}$  that define polyhedra of the form

$$P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}.$$

They only depend on A and B, but are independent of the rational right-hand sides  $\mathbf{b} \in \mathbb{Q}^{m_A}$ ,  $\mathbf{d} \in \mathbb{Q}^{m_B}$ ; we even allow  $\mathbf{b} \in \mathbb{Q}^{m_A}$ ,  $\mathbf{d} \in \mathbb{Q}^{m_B}$ , where  $\mathbb{Q}_{\infty} := \mathbb{Q} \cup \{\pm \infty\}$ . In fact, we will see that the circuits provide an optimality certificate (or test set) for a whole family of optimization problems with the right-hand sides  $\mathbf{b}$  and  $\mathbf{d}$  and the (linear) objective function as parameters.

Circuits as optimality certificates were introduced by Jack E. Graver in his seminal paper [14]. Most of the definitions and results we provide in the following were already stated therein. However, for completeness we prove all fundamental results we need throughout the thesis in this section. This also serves as an introduction to the topic and we can introduce our notation thereby.

We begin with a basic definition of circuits based on the support of vectors, followed by some fundamental observations on this set. We then turn to three equivalent descriptions of the circuits as we will make use of these characterizations in the forthcoming chapters. In this, the *representation property* immediately implies that circuits are indeed optimality certificates for linear programs. We close the section by providing some examples, including a remark on how a certain representation of the polyhedron affects the associated set of circuits.

Before we start, we make two assumptions on the matrices A and B. In the later chapters we want our polyhedra to have vertices. A vertex  $\mathbf{v}$  of  $P = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  is determined by n - rank(A) linearly independent inequalities that are tight. Thus we assume  $\text{rank}\begin{pmatrix} A \\ B \end{pmatrix} = n$  throughout the thesis, as otherwise the polyhedron cannot have vertices at all. We further assume that  $\text{rank}\begin{pmatrix} A \\ B \end{pmatrix} = \text{rank}(A) + \text{rank}(B)$ , which can easily be obtained by removing those rows (inequalities) from B that are linear combinations of the rows (equations) of A. This defines the same polyhedron, but we will see that it does not change the associated set of circuits.

## 1.1 Definition and fundamental properties

The definition of a circuit is based on the *support* of a vector: It is given by the indices of the non-zero components of  $\mathbf{v} \in \mathbb{R}^n$  as  $\operatorname{supp}(\mathbf{v}) = \{i \in \{1, \dots, n\} : v_i \neq 0\}$ . Note that for  $\mathbf{y} \in \ker(A)$ ,  $\operatorname{supp}(B\mathbf{y}) = \emptyset$  implies  $\mathbf{y} = \mathbf{0}$  as we assumed  $\operatorname{rank} \binom{A}{B} = n$ . We say that a vector  $\mathbf{v}$  is (set-wise) *support-minimal in a set*  $S \subseteq \mathbb{R}^n$  if  $\mathbf{v} \in S$  and there is no  $\mathbf{w} \in S$  with  $\operatorname{supp}(\mathbf{w}) \subseteq \operatorname{supp}(\mathbf{v})$ . We now can define the circuits of matrices A and B.

**Definition 1.1** (See Def. 3.8 in [14]). The circuits C(A, B) associated with matrices A and B are those non-zero vectors  $\mathbf{g} \in \ker(A) = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{0}\}$  for which  $B\mathbf{g}$  is support-minimal in the set  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}$ , where  $\mathbf{g}$  is normalized to (coprime) integer components.

There are a few remarks to make about this definition. First note that it is indeed independent of **b** and **d**. That is why the set of circuits was called the *universal test set* in [14]. The term 'circuit' for such vectors was first used in [28]. The set is always symmetric (that is, if  $\mathbf{g} \in C(A, B)$ ) then  $-\mathbf{g} \in C(A, B)$ ) and finite. The latter follows immediately from the next lemma, as vectors  $B\mathbf{y} \in \mathbb{R}^{m_B}$  admit only finitely many supports.

**Lemma 1.2** (See Prop. 3.9 in [14]). Let  $\mathbf{g} \in C(A, B)$  and  $\mathbf{v} \in \ker(A)$  with  $\operatorname{supp}(B\mathbf{g}) = \operatorname{supp}(B\mathbf{v})$ . Then  $\mathbf{v} = \alpha \mathbf{g}$  for some  $\alpha \in \mathbb{R}$ .

*Proof.* As  $\mathbf{g} \in \ker(A) \setminus \{\mathbf{0}\}$ , there is some  $i \in \{1, ..., m_B\}$  such that  $(B\mathbf{g})_i \neq 0$  and hence  $(B\mathbf{v})_i \neq 0$ . Let  $\mathbf{w} := \mathbf{g} - [(B\mathbf{g})_i/(B\mathbf{v})_i] \cdot \mathbf{v}$ . Then we have  $\mathbf{w} \in \ker(A)$  and further  $\sup(B\mathbf{w}) \subseteq \sup(B\mathbf{g})$  as  $(B\mathbf{w})_i = (B\mathbf{g})_i - [(B\mathbf{g})_i/(B\mathbf{v})_i] \cdot (B\mathbf{v})_i = 0$ . Hence we have  $\mathbf{w} = \mathbf{0}$  by support-minimality of  $\mathbf{g}$  and thus  $\mathbf{v} = [(B\mathbf{v})_i/(B\mathbf{g})_i] \cdot \mathbf{g}$ .

We want to highlight two special settings in which circuits frequently appear. Often one simply imposes upper or lower bounds on the variable  $\mathbf{x}$  instead of having a whole system of inequalities  $B\mathbf{x} \leq \mathbf{d}$ . In other words, we have  $B = \pm I_n$ , the identity matrix in  $\mathbb{R}^{n \times n}$ , and thus supp( $B\mathbf{x}$ ) = supp( $\mathbf{x}$ ). Then our definition of circuits is closely related to the *elementary vectors* of ker(A) as introduced in [26]. These are *all* support-minimal elements in ker(A)\{ $\mathbf{0}$ }. Observe that there are infinitely many such elements as the elementary vectors can be scaled arbitrarily: The elementary vectors are lines through the origin, with the origin excluded. However, Lemma 1.2 tells us that when restricting to those vectors whose components have greatest common divisor one, we recover the circuits  $C(A, I_n)$ , which we simply denote C(A). In particular, every vector of minimal-support in ker(A)\{ $\mathbf{0}$ } has two representatives in C(A), some circuit and its negative (compare Lemma 1.2). Further, note that our definition of circuits is consistent with the term 'circuits' used in matroid theory: The support of a support-minimal vector in ker(A)\{ $\mathbf{0}$ } describes an inclusion-minimal set of linearly dependent columns of A.

Another special case is that of having only inequality-constraints, that is, A = O, a matrix with all-zero entries. We then write  $C \subseteq (B) := C(O, B)$ . This special case will be particularly useful for investigating two-dimensional examples.

Finally, we want to point out the following: The set of circuits associated with the matrices A and B does not change when we modify B by

- 1. swapping rows of B,

- 2. multiplying a row of B by a non-zero scalar,

- 3. adding linear combinations of rows of A and B to another row of B

- 4. adding a row to the matrix B that is a linear combination of other rows of A and B, or

- 5. removing a row from B that is a linear combination of other rows of A and B,

as long as all entries remain integral. Even though these operations might change the support of some  $B\mathbf{x}$ , support-minimality is preserved. This follows immediately from the linear dependencies among the rows and from  $A\mathbf{g} = \mathbf{0}$  for all circuits  $\mathbf{g}$ . In particular this implies that the polyhedra

$$\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \le \mathbf{d}\}, \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \ge \mathbf{d}\} \text{ and } \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, \mathbf{l} \le B\mathbf{x} \le \mathbf{u}\}$$

all admit the same sets of circuits since it holds that  $C(A, B) = C(A, -B) = C(A, \binom{B}{-B})$ . Therefore, we may without loss of generality add lower bounds on  $B\mathbf{x}$  or replace the upper bounds by lower bounds.

## 1.2 Circuits as optimality certificates

We now aim at proving the test set property for circuits. Therefore, we have to consider sign-compatible vectors: Two vectors  $\mathbf{v}, \mathbf{w} \in \mathbb{R}^n$  are *sign-compatible with respect to the matrix B* defining the polyhedron  $P = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$ , if  $B\mathbf{v}$  and  $B\mathbf{w}$  belong to the same orthant of  $\mathbb{R}^{m_B}$ , that is, their *i*-th components  $(B\mathbf{v})_i$  and  $(B\mathbf{w})_i$  satisfy  $(B\mathbf{v})_i \cdot (B\mathbf{w})_i \geq 0$  for all  $i = 1, \ldots, m_B$ . Note that for  $B = I_n$  this definition becomes much simpler. We first need the following

**Lemma 1.3** (Cf. Lemma 3.11 in [14]). If  $\mathbf{v} \neq \mathbf{0}$  is not support-minimal in  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}\$ , then there is an element  $\mathbf{w} \in \ker(A) \setminus \{\mathbf{0}\}\$  such that  $\mathbf{w}$  and  $\mathbf{v}$  are sign-compatible with respect to B and  $\sup(B\mathbf{w}) \subseteq \sup(B\mathbf{v})$ .

*Proof.* As  $B\mathbf{v}$  is not support-minimal in  $\{B\mathbf{y}: \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}$ , there is  $\mathbf{y} \in \ker(A) \setminus \{0\}$  such that  $\sup(B\mathbf{y}) \subseteq \sup(B\mathbf{v})$ . We can assume without loss of generality that there is some  $i \in \{1, \ldots, m_B\}$  such that  $(B\mathbf{v})_i(B\mathbf{y})_i > 0$  (otherwise we replace  $\mathbf{y}$  by  $-\mathbf{y}$ ). Let  $\mathbf{w} := \mathbf{v} - \alpha \mathbf{y}$ , where  $\alpha := \min\{(B\mathbf{v})_i/(B\mathbf{y})_i: (B\mathbf{v})_i(B\mathbf{y})_i > 0\} \ge 0$ . Let  $(B\mathbf{v})_i = 0$ . Then  $(B\mathbf{w})_i = -\alpha(B\mathbf{y})_i = 0$  as  $\sup(B\mathbf{y}) \subseteq \sup(B\mathbf{v})$  and hence  $\sup(B\mathbf{w}) \subseteq \sup(B\mathbf{v})$ . It remains to show sign-compatibility, that is,  $0 \le (B\mathbf{w})_i(B\mathbf{v})_i = (B\mathbf{v})_i^2 - \alpha(B\mathbf{y})_i(B\mathbf{v})_i$ . For  $(B\mathbf{y})_i(B\mathbf{v})_i \le 0$  non-negativity of this term is obvious. Otherwise we have (by definition of  $\alpha$ ) that  $(B\mathbf{v})_i^2 - \alpha(B\mathbf{y})_i(B\mathbf{v})_i \ge (B\mathbf{v})_i^2 - [(B\mathbf{v})_i/(B\mathbf{y})_i](B\mathbf{y})_i(B\mathbf{v})_i = 0$ .

With this we now are able to state a crucial property of circuits.

**Proposition 1.4** (Representation property, see Theorem 3.12 in [14]). Every element  $\mathbf{v} \in \ker(A)$  can be written as a positive linear sign-compatible sum of elements in C(A, B), that is, we have a representation  $\mathbf{v} = \sum_{i=1}^{k} \alpha_i \mathbf{g}^i$ , such that for all i = 1, ..., k

- (i)  $\mathbf{g}^i \in C(A, B)$ ,

- (ii)  $\mathbf{g}^i$  and  $\mathbf{v}$  are sign-compatible and  $\operatorname{supp}(B\mathbf{g}^i) \subseteq \operatorname{supp}(B\mathbf{v})$ , and

- (iii)  $\alpha_i \in \mathbb{R}_+ := \{\alpha \in \mathbb{R} : \alpha \geq 0\}$ .

*Proof.* Let  $\mathbf{v} \in \ker(A)$ . If  $\mathbf{v} = \mathbf{0}$ , there is nothing to show. Else, if  $B\mathbf{v}$  is support-minimal in the set  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}$ , by Lemma 1.2 there is  $\mathbf{g} \in C(A, B)$  such that  $\mathbf{v} = \alpha \mathbf{g}$  for some  $\alpha \in \mathbb{R}$  and we can choose  $\alpha > 0$  as the set of circuits is symmetric. So assume  $\mathbf{v}$  is not support-minimal in  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}$ . Then by Lemma 1.3 there is some  $\mathbf{w} \in \ker(A) \setminus \{\mathbf{0}\}$  such that  $\mathbf{w}$  and  $\mathbf{v}$  are sign-compatible with respect to B and supp $(B\mathbf{w}) \subseteq \sup(B\mathbf{v})$ . Let  $\mathbf{w}' := \mathbf{v} - \alpha \mathbf{w}$  for  $\alpha := \min\{(B\mathbf{v})_i/(B\mathbf{w})_i : (B\mathbf{w})_i \neq 0\} \ge 0$ . Then supp $(B\mathbf{w}') \subseteq \sup(B\mathbf{v})$ , as clearly supp $(B(\mathbf{v} - \alpha \mathbf{w})) \subseteq \sup(B\mathbf{v})$ , and  $B(\mathbf{v} - \alpha \mathbf{w})$  has at least one extra zero-entry by definition of  $\alpha$ . Further  $\mathbf{w}'$  and  $\mathbf{v}$  are sign-compatible as  $(B\mathbf{v})_i(B\mathbf{w}')_i = (B\mathbf{v})_i^2 - \alpha(B\mathbf{v})_i(B\mathbf{w})_i \ge (B\mathbf{v})_i^2 - [(B\mathbf{v})_i/(B\mathbf{w})_i] (B\mathbf{v})_i(B\mathbf{w})_i = 0$ . Hence we found a representation  $\mathbf{v} = \alpha \mathbf{w} + \mathbf{w}'$  for vectors  $\alpha \mathbf{w}$  and  $\mathbf{w}'$  sign-compatible with  $\mathbf{v}$  and supp $(B(\alpha \mathbf{w}))$ , supp $(B\mathbf{w}') \subseteq \sup(B\mathbf{v})$ . The claim follows inductively. □

Note that the circuits  $\mathbf{g}^i$  are also pairwise sign-compatible with respect to B. The following corollary now gives us an alternative definition for circuits.

**Corollary 1.5** (Circuit definition via representation property). The set of circuits C(A, B) is (up to scaling) the unique inclusion-minimal set admitting the representation property posed in Proposition 1.4.

*Proof.* By Proposition 1.4, C(A, B) has this representation property. On the other hand, (ii) and (iii) from Proposition 1.4 together with Lemma 1.2 imply that such a set must contain a representative  $\alpha \mathbf{g}$ ,  $\alpha \in \mathbb{R}_+$  of every circuit  $\mathbf{g} \in C(A, B)$ .

Now it is not hard to show that the circuits are indeed a test set for maximizing (or equivalently minimizing) linear objectives, as already proven in [14].

**Corollary 1.6** (See Cor. 3.13 in [14]). Let  $\mathbf{x}^0$  be a non-optimal solution of

$$\max \{ \mathbf{c}^{\mathsf{T}} \mathbf{x} : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}, \mathbf{x} \in \mathbb{R}^n \}$$

.

Then there is an augmenting direction  $\mathbf{g} \in C(A, B)$  and some  $\alpha \in \mathbb{R}_+$  such that  $\mathbf{x}^0 + \alpha \mathbf{g} \in P$ =  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}\$ and  $\mathbf{c}^{\mathsf{T}}(\mathbf{x}^0 + \alpha \mathbf{g}) > \mathbf{c}^{\mathsf{T}}(\mathbf{x}^0).$

*Proof.* Let  $\mathbf{x}^* \in P$  be a better solution of the linear program, that is,  $\mathbf{c}^{\mathsf{T}}\mathbf{x}^* > \mathbf{c}^{\mathsf{T}}\mathbf{x}^0$ . Then  $\mathbf{x}^* - \mathbf{x}^0 \in \ker(A)$  and by Proposition 1.4 it can be written as  $\mathbf{x}^* - \mathbf{x}^0 = \sum_{i=1}^k \alpha_i \mathbf{g}^i$ , satisfying (i),(ii),(iii). Observe that  $B\mathbf{x}^0 \leq \mathbf{d}$  and  $B(\mathbf{x}^0 + \sum_{i=1}^k \alpha_i \mathbf{g}^i) = B\mathbf{x}^* \leq \mathbf{d}$  together with sign-compatibility of  $B\mathbf{g}^i$  and  $B(\mathbf{x}^* - \mathbf{x}^0)$  imply that  $B(\mathbf{x}^0 + \alpha_i \mathbf{g}^i) \leq \mathbf{d}$  for  $i = 1, \dots, k$ . Thus we have  $\mathbf{x}^0 + \alpha_i \mathbf{g}^i \in P$  for all i. We further know that  $0 < \mathbf{c}^{\mathsf{T}}(\mathbf{x}^* - \mathbf{x}^0) = \mathbf{c}^{\mathsf{T}}(\sum_{i=1}^k \alpha_i \mathbf{g}^i) = \sum_{i=1}^k \alpha_i \mathbf{c}^{\mathsf{T}}\mathbf{g}^i$  and hence there is some i such that  $\mathbf{c}^{\mathsf{T}}\mathbf{g}^i > 0$ . Therefore, we found  $\mathbf{x}^0 + \alpha_i \mathbf{g}^i$  satisfying the claim.

This proves the test set property of C(A, B) for linear objectives for any choice of **b** and **d**. It is not hard to show that the circuits are in fact the unique inclusion-minimal set with this property (up to scaling). Note that this result can easily be extended to the minimization of separable convex functions  $f: \mathbb{R}^n \to \mathbb{R}$ , i.e. f is convex and can be written as  $f(\mathbf{x}) = \sum_{i=1}^n f_i(x_i)$  for convex functions  $f_1, \ldots, f_n \colon \mathbb{R} \to \mathbb{R}$ .

Observe that the circuits can also be used to check whether the linear program is bounded: This is the case if and only if there is no  $\mathbf{g} \in C(A, B)$  with  $B\mathbf{g} \leq \mathbf{0}$  and  $\mathbf{c}^{\mathsf{T}}\mathbf{g} > \mathbf{0}$  (if we maximize); see for example Prop. 3.15 in [14].

Finally, we want to point out that one has to be careful when using circuits in an augmentation procedure as an infinite zig-zagging can occur, see Section 4 in [15]. An example for a strategy that ensures termination is the steepest-descent approach from [10].

## 1.3 Further characterizations of circuits

The definition of circuits via the representation property is directly connected to a third characterization that is based on minimal generating sets of cones: Denote by  $B_i$  the i-th row of B and consider the hyperplanes  $\{\mathbf{x} \in \mathbb{R}^n : B_i\mathbf{x} = \mathbf{0}\}$ . These hyperplanes partition  $\mathbb{R}^n$  into  $2^{m_B}$  rational polyhedral cones of the form  $C_{\sim} = \{\mathbf{x} \in \mathbb{R}^n : B\mathbf{x} \sim \mathbf{0}\}$ , where  $\sim \in \{\leq, \geq\}^{m_B}$ . All elements in such a cone  $C_{\sim}$  are pairwise sign-compatible. Let  $H_{\sim}$  the unique minimal generating set of  $C_{\sim} \cap \ker(A)$  over  $\mathbb{R}$ , where the components of each generator are scaled to integers with greatest common divisor one. Then we get the following characterization of the circuits.

**Proposition 1.7.** The circuits of A and B are given by

$$C(A,B) = \bigcup_{\sim \in \{\leq,\geq\}^{m_B}} H_{\sim}.$$

*Proof.* Let  $\mathbf{g} \in C(A, B)$ . Then  $\mathbf{g} \in C_{\sim}$  for some  $\sim \in \{ \leq, \geq \}^{m_B}$  and  $\mathbf{g}$  can be written as  $\mathbf{g} = \sum_{i=1}^k \beta_i \mathbf{h}^i$  for  $\beta_i \in \mathbb{R}_+$ ,  $\mathbf{h}^i \in H_{\sim}$ . As all coefficients are positive we must have  $\operatorname{supp}(B\mathbf{h}^i) \subseteq \operatorname{supp}(B\mathbf{g})$  for all  $i = 1, \ldots, k$ . As  $\mathbf{h}^i \neq \mathbf{0}$ , Lemma 1.2 implies that  $\mathbf{h}^i = \alpha_i \mathbf{g}$  for  $\alpha_i \in \mathbb{R}$ ,  $i = 1, \ldots, k$ . Thus  $\mathbf{g} = \mathbf{h}^i$  for all i as the generators are normalized and hence  $\mathbf{g} \in H_{\sim}$ .

Now let  $\mathbf{h} \in H_{\sim}$  for some  $\sim \in \{\leq, \geq\}^{m_B}$ . Then  $\mathbf{h} \in \ker(A)$ . By Proposition 1.4 there is a representation  $\mathbf{h} = \sum_{i=1}^k \alpha_i \mathbf{g}^i$  with (i),(ii),(iii), in particular  $\mathbf{g}^i \in C_{\sim}$  by (ii). Thus  $\mathbf{h} = \mathbf{g}^i$  for  $i = 1, \ldots, k$  as  $\mathbf{h}$  belongs to the minimal normalized generating set of  $C_{\sim} \cap \ker(A)$ , in particular  $\mathbf{h} \in C(A, B)$ .

Our last description of the set of circuits is of a different nature: We show that the circuits coincide with all potential edge directions of the polyhedron  $P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$  that can appear when we fix the matrices A and B, but let the right-hand sides  $\mathbf{b}$  and  $\mathbf{d}$  vary. In [28] this was proven for the special case  $B = I_n$  and [14] states that all these edge directions are contained in C(A, B). We now prove that these two sets are indeed the same. Note that an edge

of the polyhedron  $P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$  is determined by n - rank(A) - 1 linearly independent inequalities that are tight.

**Theorem 1.8.** The set of circuits C(A, B) coincides with the edge directions of polyhedra

$$P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} < \mathbf{d} \}$$

that can appear for any choice of rational **b** and **d**.

*Proof.* Let e be an edge of  $P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$ . Let  $r := \operatorname{rank}(A)$ . Then e is determined by n - r - 1 linearly independent inequalities of the system  $B\mathbf{x} \leq \mathbf{d}$  that are tight for all elements of e, that is, there is a submatrix  $B^e \in \mathbb{R}^{l \times n}$  of B with  $\operatorname{rank}(B^e) = n - r - 1$  and a corresponding subvector  $\mathbf{d}^e \in \mathbb{R}^l$  of  $\mathbf{d}$  such that  $\binom{A}{B^e}\mathbf{v} = \binom{\mathbf{b}}{\mathbf{d}^e}\mathbf{v}$  for all  $\mathbf{v} \in e$ . Observe that  $\operatorname{rank}\binom{A}{B^e}\mathbf{v} = n - 1$ . Let  $\mathbf{g}$  be the direction of e (that is,  $\mathbf{g} = \mathbf{w} - \mathbf{v}$  for two distinct vectors  $\mathbf{v}, \mathbf{w} \in e$ ). Then  $\mathbf{g} \in \ker\binom{A}{B^e}\mathbf{v}$  and this kernel is one-dimensional. Every element  $\mathbf{v} \in \ker(A) \setminus \{\mathbf{0}\}$  with  $\sup(B\mathbf{v}) \subseteq \sup(B\mathbf{g})$  must satisfy  $B^e\mathbf{v} = 0$ . Thus  $\mathbf{v} \in \ker(A) \setminus \{\mathbf{0}\}$ , and hence  $\mathbf{v} = \lambda \mathbf{g}$  for some  $\lambda \in \mathbb{R}$ . Therefore,  $B\mathbf{g}$  is support-minimal in  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\}\}$ .

Now let  $\mathbf{g}$  be a circuit. We set  $\mathbf{b} := \mathbf{0}$  and define  $\mathbf{d}$  as the component-wise maximum of  $B\mathbf{g}$  and  $\mathbf{0}$ . We claim that  $P = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  has an edge of direction  $\mathbf{g}$ . Clearly  $\mathbf{0}, \mathbf{g} \in P$ . It remains to show that these two vectors are contained in a common one-dimensional face of P. Let  $B^0 \in \mathbb{R}^{l \times n}$  be the submatrix of B that satisfies  $B^0\mathbf{g} = \mathbf{0}$ , where I is chosen maximal (i.e.  $(B\mathbf{g})_i \neq 0$  for all rows i of B not contained in  $B^0$ ). Observe that the support of  $B\mathbf{g}$  corresponds to the rows of B that are not in  $B^0$ . Assume  $\operatorname{rank}(B^0) < n - r - 1$ . Then we can add rows of B to  $B^0$  to obtain a matrix B of  $\operatorname{rank}(B^0) = \{A\mathbf{x} : A \in \mathbb{R}\}$  for some  $\mathbf{x} \neq \mathbf{0}$ . Thus we have  $\sup(B\mathbf{x}) \subseteq \sup(B\mathbf{g})$ , a contradiction to  $\mathbf{g}$  being a circuit.

We will frequently use this quite intuitive definition when studying *circuit diameters* in the forthcoming chapters.

## 1.4 Examples

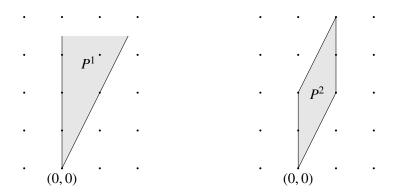

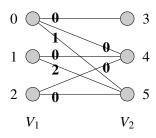

We now give two examples to illustrate the prior definitions and characterizations of circuits, one for each of the special cases A = O and  $B = I_n$ .

**Example 1.9.** Let  $B = \begin{pmatrix} -1 & 0 \\ 2 & -1 \end{pmatrix}$ . The circuits are given by

$$C_{\leq}(B) = \left\{ \pm \begin{pmatrix} 0 \\ 1 \end{pmatrix}, \pm \begin{pmatrix} 1 \\ 2 \end{pmatrix} \right\}.$$

To see this, we compute the vectors Bg for all circuits g:

$$B \cdot \pm \begin{pmatrix} 0 \\ 1 \end{pmatrix} = \pm \begin{pmatrix} 0 \\ -1 \end{pmatrix}, \quad B \cdot \pm \begin{pmatrix} 1 \\ 2 \end{pmatrix} = \pm \begin{pmatrix} -1 \\ 0 \end{pmatrix}.$$

Obviously, both products  $\pm \binom{0}{-1}$  and  $\pm \binom{-1}{0}$  are support-minimal in  $\{B\mathbf{y} : \mathbf{y} \in \ker(A) \setminus \{\mathbf{0}\} = \mathbb{R}^2 \setminus \{\mathbf{0}\}\}$  and there can be not other vectors of minimal support. Thus the corresponding factors  $\binom{0}{1}$  and  $\binom{1}{2}$  constitute the set of circuits as they are integral vectors and their components have greatest common divisor one.

Now consider the polyhedra

$$P^1 = \left\{ \mathbf{x} \in \mathbb{R}^2 : B\mathbf{x} \le \mathbf{d} \right\}, \quad where \ \mathbf{d} = \left( \begin{array}{c} 0 \\ 0 \end{array} \right)$$

and

$$P^2 = \left\{ \mathbf{x} \in \mathbb{R}^2 : \mathbf{l} \le B\mathbf{x} \le \mathbf{u} \right\}, \quad where \ \mathbf{l} = \begin{pmatrix} -1 \\ -2 \end{pmatrix}, \ \mathbf{u} = \begin{pmatrix} 0 \\ 0 \end{pmatrix}.$$

We know that both polyhedra admit the same set of circuits. The polyhedra look as follows:

Figure 1.1: Two polyhedra defined by the same matrix *B*.

$P^1$  is an unbounded cone, while  $P^2$  is a polytope. We see that the circuits  $\{\pm \binom{0}{1}, \pm \binom{1}{2}\}$  are indeed the directions of the edges of the polyhedra, as stated in Theorem 1.8.

**Example 1.10.** Let

$$A = \begin{pmatrix} -1 & 0 & 1 & 0 \\ 2 & -1 & 0 & 1 \end{pmatrix}$$

,  $B = I_4$ . Then

$$C(A) = \left\{ \pm \begin{pmatrix} 0 \\ 1 \\ 0 \\ 1 \end{pmatrix}, \pm \begin{pmatrix} 1 \\ 2 \\ 1 \\ 0 \end{pmatrix}, \pm \begin{pmatrix} 1 \\ 0 \\ 1 \\ -2 \end{pmatrix} \right\}.$$

Clearly, all these elements lie in the kernel of A and it is not hard to check that there are no non-zero elements in that kernel of strictly smaller support.

To illustrate the representation property, consider  $(-2, 3, -2, 7)^{\mathsf{T}} \in \ker(A)$ . We can express this

vector as a sign-compatible non-negative linear combination of circuits:

$$\begin{pmatrix} -2\\3\\-2\\7 \end{pmatrix} = 3 \cdot \begin{pmatrix} 0\\1\\0\\1 \end{pmatrix} + 2 \cdot \begin{pmatrix} -1\\0\\-1\\2 \end{pmatrix}$$

## Circuits for equivalent descriptions of polyhedra

We want to point out that the particular representation of a polyhedron affects the set of circuits in the following sense: The polyhedra

$$P = \{ \mathbf{x} \in \mathbb{R}^n : B\mathbf{x} \le \mathbf{d} \}$$

and

$$P' = \left\{ \begin{pmatrix} \mathbf{x} \\ \mathbf{x}' \end{pmatrix} \in \mathbb{R}^{n+m_B} : \begin{pmatrix} B & I_{m_B} \end{pmatrix} \begin{pmatrix} \mathbf{x} \\ \mathbf{x}' \end{pmatrix} = \mathbf{d}, \ \mathbf{x}' \geq \mathbf{0} \right\}$$

are equivalent, but this is not necessarily true for the associated circuits  $C_{\leq}(B)$  and C(A), where  $A = \begin{pmatrix} B & I_{m_B} \end{pmatrix}$  as Example 1.11 shows. More precisely, we will see that C(A) can contain additional elements, as the circuits associated with A allow for more elements of minimal support.

**Example 1.11.** Observe that the matrix B in Example 1.9 and the matrix A in Example 1.10 are indeed related via  $A = \begin{pmatrix} B & I_2 \end{pmatrix}$ . But  $C_{\leq}(B)$  contains four vectors while C(A) consists of six elements. Hence the sets of circuits are not equivalent.

However, one can deduce the set  $C_{\leq}(B)$  from the circuits of  $A = \begin{pmatrix} B & I_{m_B} \end{pmatrix}$ .

**Lemma 1.12.** Let  $B \in \mathbb{Z}^{m_B \times n}$ ,  $A := \begin{pmatrix} B & I_{m_B} \end{pmatrix}$  and  $\mathbf{g} \in \mathbb{R}^n$ . Then  $\mathbf{g} \in C_{\leq}(B)$  if and only if there is some  $\begin{pmatrix} \mathbf{g} \\ \mathbf{g'} \end{pmatrix} \in C(A)$  such that  $\mathbf{g'}$  is support-minimal in the set  $\{\mathbf{y'} : \begin{pmatrix} \mathbf{y} \\ \mathbf{y'} \end{pmatrix} \in C(A)$  for some  $\mathbf{y} \in \mathbb{R}^n \}$ .

*Proof.* Let  $\mathbf{g} \in C_{\leq}(B)$ . Then  $B\mathbf{g}$  is support-minimal  $\{B\mathbf{y} : \mathbf{y} \in \mathbb{R}^n\} = \{-B\mathbf{y} : \mathbf{y} \in \mathbb{R}^n\}$  and  $\binom{\mathbf{g}}{-B\mathbf{g}} \in \ker(A)$ . Let  $\mathbf{g}' := -B\mathbf{g}$ . Then  $\binom{\mathbf{g}}{\mathbf{g}'} \in \ker(A)$  and  $\mathbf{g}'$  is support-minimal in  $\{\mathbf{y}' : \binom{\mathbf{y}}{\mathbf{y}'} \in \ker(A) \setminus \{\mathbf{0}\} \text{ for some } \mathbf{y} \in \mathbb{R}^n\}$ . But then also  $\binom{\mathbf{g}}{\mathbf{g}'}$  is support-minimal in  $\ker(A) \setminus \{\mathbf{0}\}$  and hence  $\binom{\mathbf{g}}{\mathbf{g}'} \in C(A)$ . Further, as  $\mathbf{g}'$  is support-minimal in  $\{\mathbf{y}' : \binom{\mathbf{y}}{\mathbf{y}'} \in \ker(A) \setminus \{\mathbf{0}\} \text{ for some } \mathbf{y} \in \mathbb{R}^n\}$ , it is also support-minimal in the subset  $\{\mathbf{y}' : \binom{\mathbf{y}}{\mathbf{y}'} \in C(A)\}$ .

Now let  $\binom{\mathbf{g}}{\mathbf{g}'} \in C(A)$  such that  $\mathbf{g}'$  is support-minimal in the set  $\left\{\mathbf{y}': \binom{\mathbf{y}}{\mathbf{y}'} \in C(A) \text{ for some } \mathbf{y} \in \mathbb{R}^n \right\}$ . For  $\mathbf{g}$  being a circuit it is enough to show that  $\mathbf{g}' = -B\mathbf{g}$  is support-minimal in  $\{-B\mathbf{y}: \mathbf{y} \in \mathbb{R}^n \setminus \{\mathbf{0}\}\}$ . Assume that  $\mathbf{g}'$  is not support-minimal in this set. Then there is some  $\mathbf{y} \in \mathbb{R}^n \setminus \{\mathbf{0}\}$  such that  $\sup(\mathbf{y}') \subseteq \sup(\mathbf{g}')$  for  $\mathbf{y}' := -B\mathbf{y}$ . By case-assumption,  $\binom{\mathbf{y}}{\mathbf{y}'} \notin C(A)$ , but  $\binom{\mathbf{y}}{\mathbf{y}'} \in \ker(A) \setminus \{\mathbf{0}\}$  by definition of  $\mathbf{y}'$ . Hence there is  $\binom{\mathbf{x}}{\mathbf{x}'} \in C(A)$  such that  $\sup(\mathbf{y}) \subseteq \sup(\mathbf{y})$  and  $\sup(\mathbf{x}') \subseteq \sup(\mathbf{y}') \subseteq \sup(\mathbf{y}')$  supp $(\mathbf{y}')$ , that is,  $\mathbf{g}'$  is not support-minimal in  $\left\{\mathbf{y}': \binom{\mathbf{y}}{\mathbf{y}'} \in C(A) \text{ for some } \mathbf{y} \in \mathbb{R}^n \right\}$ , a contradiction.

**Example 1.11 cont'd.** To deduce  $C_{\leq}(B)$  from C(A), we have to look for support-minimality in the 'slack', i.e. within the vectors formed by the third and forth components of the elements in C(A). These are

$$\left\{\mathbf{y}': \begin{pmatrix} \mathbf{y} \\ \mathbf{y}' \end{pmatrix} \in C(A) \text{ for some } \mathbf{y} \in \mathbb{R}^2 \right\} = \left\{ \pm \begin{pmatrix} 0 \\ 1 \end{pmatrix}, \ \pm \begin{pmatrix} 1 \\ 0 \end{pmatrix}, \ \pm \begin{pmatrix} 1 \\ -2 \end{pmatrix} \right\}.$$

The first two elements are support-minimal in this set. Hence the vectors formed by the first and second components of the corresponding vectors in C(A),  $\pm \begin{pmatrix} 0 \\ 1 \end{pmatrix}$  and  $\pm \begin{pmatrix} 1 \\ 2 \end{pmatrix}$ , constitute the set  $C_{\leq}(B)$  as already shown in Example 1.9.

#### **Outlook**

In the next Chapter 2 we will introduce a hierarchy of circuit distances. These distances are based on circuit walks, which connect two vertices of a polyhedron by a number of steps along circuit directions. Proposition 1.4 tells us that there always is such a walk, even a sign-compatible one. Further, we know that we can reach any vertex of the polyhedron from any point within the polyhedron along circuits by Corollary 1.6. All these results will be important for the upcoming investigations. The characterization of circuits as edge directions from Theorem 1.8 will be stressed in Chapter 3 and 4, where we study the circuit distances of transportation polytopes and dual network flow polyhedra, respectively.

# **Chapter 2**

# A hierarchy of circuit distances

We now come to the key part of the present thesis: In this chapter we introduce the different categories of circuit diameters. Most of these classes are less restrictive than the combinatorial diameter: Instead of only going along the edges of the polyhedron we liberate ourselves from these restrictions. We try to go from one vertex of the polyhedron to another one more efficiently by possibly going through the interior of the polyhedron, along linear combinations of circuits. We are even willing to leave the feasible region.

As already outlined in the introduction, the purpose of this approach is two-fold: On the one hand we have the intimate connection of circuit distances to a best-case performance of augmentation algorithms along circuit directions. In particular, this could serve as an indication on how to use circuits in such algorithms. Recall that augmentation algorithms are a generalization of the Simplex method.

On the other hand, we hope that the circuit diameters as a generalization to the classical combinatorial diameter might shed some light on this difficult field of research and help us for a better understanding. In particular, the combinatorial diameter is bounded below by diameters that have much weaker properties and therefore may be much easier to bound or to compute. We will exploit this in Chapter 3 for transportation polytopes and in Chapter 4 for dual network flow polyhedra.

This chapter is based on joint work with Steffen Borgwardt, Jesús A. De Loera and Raymond Hemmecke, published in [3] and [5]. It is structured the following way: In Section 2.1 we begin with a formal introduction of circuit walks, circuit distances, and circuit diameters, along with an overview of their characteristics. In Section 2.2 we then present the core result, the hierarchy of circuit distances, followed by the proofs of the relations claimed therein. In Section 2.3 we have a look at general upper bounds for circuit diameters. In particular we will see that many of the diameter categories satisfy the bound induced by the Hirsch conjecture. We conclude the chapter by investigating the hierarchy in dimension two in Section 2.4. In this special case many of the circuit diameter concepts coincide such that the hierarchy 'collapses' into only few distinct categories.

## 2.1 Definitions and preliminaries

In this section we first define a very general notion of *distance* based on circuits. We then introduce additional properties for these walks, which leads to a variety of circuit distances. After explaining these categories, we summarize some basic characteristics of circuit walks and circuit distances.

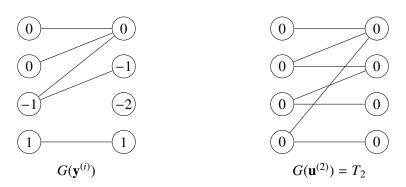

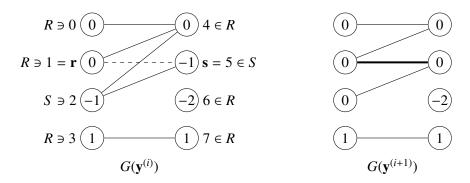

#### 2.1.1 Circuit walks

Let  $P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$  be a polyhedron and let C(A, B) be the set of circuits associated with the matrices A and B. For a pair of vertices  $\mathbf{v}^{(1)}$ ,  $\mathbf{v}^{(2)}$  of P, we call a sequence  $\mathbf{v}^{(1)} = \mathbf{y}^{(0)}, \ldots, \mathbf{y}^{(k)} = \mathbf{v}^{(2)}$  a *circuit walk of length k* if for all  $i = 0, \ldots, k-1$  we have  $\mathbf{y}^{(i+1)} - \mathbf{y}^{(i)} = \alpha_i \mathbf{g}^i$  for some circuit  $\mathbf{g}^i \in C(A, B)$  and some  $\alpha_i > 0$ . Note that because we are allowing the  $\alpha_i$  to be arbitrary real non-negative numbers, circuit walks can be infinite, but we restrict our attention to those that are finite. We are particularly interested in circuit walks that satisfy certain combinations of additional properties:

- (e) If  $\mathbf{y}^{(i)}$  and  $\mathbf{y}^{(i+1)}$  are neighboring vertices of the polyhedron (vertices connected by an edge) for all  $i = 0, \dots, k-1$ , we call the walk an *edge walk*. This is the term that corresponds to the classical combinatorial diameter.

- (m) If the extension multipliers  $\alpha_i$  are maximal, i.e. if  $\mathbf{y}^{(i)} + \alpha \mathbf{g}^i$  is infeasible for all  $\alpha > \alpha_i$ , we say that the walk is of *maximum extension length* or simply *maximal*. Otherwise, we say that the extension is of *arbitrary length*.

- (f) If  $\mathbf{y}^{(i)} \in P$  for all  $i = 0, \dots, k-1$ , then we say the circuit walk is *feasible*.

- (r) If no circuit is repeated, then we say the walk is *non-repetitive*.

- (b) If no pair of circuits  $\mathbf{g}^i$ ,  $-\mathbf{g}^i$  is used, we say the walk is *non-backwards*.

- (s) If all the circuits are pairwise sign-compatible and are all sign-compatible with the vector  $\mathbf{v}^{(2)} \mathbf{v}^{(1)}$ , we say the circuit walk is *sign-compatible*. Recall that two vectors  $\mathbf{x}$  and  $\mathbf{y}$  are sign-compatible (with respect to the matrix B), if  $(B\mathbf{x})_i \cdot (B\mathbf{y})_i \ge 0$  for all  $i = 1, \dots, m_B$ .

## 2.1.2 Categories of circuit distances and circuit diameters

We now define the *circuit distance* from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  as the minimum length of a circuit walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$ . A circuit walk that realizes the circuit distance is called a *shortest* or *optimal* walk. The *circuit diameter* of a polyhedron P is the maximum circuit distance between any two vertices of P. Considering different types of circuit walks yields different categories of circuit distances and diameters.

The main goal of this chapter is to relate these distances to each other. We now introduce a notation for this discussion: CD refers to the circuit distance defined on circuit walks without any further restrictions. We call it the *soft circuit distance*. When we consider circuit distances with

respect to circuit walks that satisfy some of the properties stated in Section 2.1.1, we denote this by small subscript letters as used in the above list. For example, the classical *combinatorial diameter* is defined on circuit walks that always go along an edge to the next vertex. These are maximal steps that always remain feasible, so we write  $CD_{efm}$  for the combinatorial distance. By dropping the edge walk property, we obtain  $CD_{fm}$ . This is the *circuit distance* we originally introduced in [5]. We call the category  $CD_f$ , defined on feasible circuit walks with steps of arbitrary length, the *weak circuit distance*. These four types of circuit distances will form the 'key chain' in the hierarchy of distances we introduce in Section 2.2.

Note that circuit distances on which we impose more restrictions trivially bound less restrictive ones from above. We denote this with a weak-inequality sign. For example, the 'key chain' looks as follows:

$$C\mathcal{D}_{efm} \geq C\mathcal{D}_{fm} \geq C\mathcal{D}_{f} \geq C\mathcal{D}$$

.

If we have ' $\geq$ ' and there is a polyhedron with a pair vertices such the respective circuits distances actually differ, we use '>'. For example, we will see that  $\mathcal{CD}_{fm} > \mathcal{CD}_f$ . Note that this notation is transitive: Clearly  $\mathcal{CD}_{fm} \geq \mathcal{CD}_f \geq \mathcal{CD}$  implies  $\mathcal{CD}_{fm} \geq \mathcal{CD}$  and  $\mathcal{CD}_{fm} > \mathcal{CD}_f \geq \mathcal{CD}$  implies  $\mathcal{CD}_{fm} > \mathcal{CD}$ . We sometimes want to refer to several combinations at the same time. We then use brackets to emphasize this, for example  $\mathcal{CD}_{fm(b)} \geq \mathcal{CD}_{f(b)}$  means that both statements hold,  $\mathcal{CD}_{fmb} \geq \mathcal{CD}_{fb}$  and  $\mathcal{CD}_{fm} \geq \mathcal{CD}_f$ .

Note that we may equally use this ' $\mathcal{CD}$ -notation' to refer to the circuit *diameter* of a polyhedron as the maximum distance over all pairs of vertices.

Theoretically, there are many different categories of circuit distances that arise from combining the properties above. However, we will not consider every such combination in our hierarchy in Section 2.2 for two reasons: Some of these combinations are not well-defined and there are combinations that actually refer to the same concepts.

For the latter, note that certain combinations of properties already imply other properties. For example, every edge walk is feasible and maximal, that is,  $C\mathcal{D}_e = C\mathcal{D}_{efm}$ , the classes coincide. Thus one can use both notations equally. However, in this chapter we stick to  $C\mathcal{D}_{efm}$  to keep all the properties in sight. Similarly, maximal circuit walks are always feasible and thus  $C\mathcal{D}_m = C\mathcal{D}_{fm}$ . In Lemma 2.14 we will see that same holds for sign-compatible circuit walks, that is,  $C\mathcal{D}_s = C\mathcal{D}_{fs}$ . Note that we even have  $C\mathcal{D}_{e(b)(r)} = C\mathcal{D}_{efm(b)(r)}$  and  $C\mathcal{D}_{m(b)(r)} = C\mathcal{D}_{fm(b)(r)}$ .

Circuit distance categories can also coincide in the sense that the *optimal* circuit walks satisfy additional properties. For example, every optimal circuit walk without any restrictions is non-backwards and non-repetitive as we could combine opposite or repeated steps to one single circuit step, yielding a shorter circuit walk. Thus we have  $CD = CD_b = CD_r$ . Again by Lemma 2.14 this is also true for sign-compatible walks, so we have  $CD_{fs} = CD_{fsbr} = CD_s = CD_{sbr}$ .

Next we come to combinations of properties that are not well-defined. This happens if we require sign-compatibility for edge walks or for feasible maximal walks.

**Lemma 2.1.** In dimension n = 2, there is a polytope with a pair of vertices such that there is no

feasible maximal sign-compatible circuit walk from one vertex to the other one. In particular there is no sign-compatible edge walk.

Proof. Consider the polytope

$$P = \left\{ \mathbf{x} \in \mathbb{R}^2 : \mathbf{l} \le B\mathbf{x} \le \mathbf{u} \right\}$$

defined by

$$B = \begin{pmatrix} 1 & 0 \\ 1 & 1 \\ 1 & -1 \\ 1 & -2 \end{pmatrix}, \quad \mathbf{l} = \begin{pmatrix} 0 \\ 0 \\ -1 \\ -3 \end{pmatrix}, \quad \mathbf{u} = \begin{pmatrix} \infty \\ 6 \\ 4 \\ \infty \end{pmatrix}.$$

All possible edge directions  $\mathbf{g}$  of P (the circuits) are given by

$$\pm \begin{pmatrix} 0 \\ 1 \end{pmatrix}, \pm \begin{pmatrix} 1 \\ -1 \end{pmatrix}, \pm \begin{pmatrix} 1 \\ 1 \end{pmatrix}, \pm \begin{pmatrix} 2 \\ 1 \end{pmatrix},$$

and the corresponding vectors  $B\mathbf{g}$  are

$$\pm \begin{pmatrix} 0 \\ 1 \\ -1 \\ -2 \end{pmatrix}, \ \pm \begin{pmatrix} 1 \\ 0 \\ 2 \\ 3 \end{pmatrix}, \ \pm \begin{pmatrix} 1 \\ 2 \\ 0 \\ -1 \end{pmatrix}, \ \pm \begin{pmatrix} 2 \\ 3 \\ 1 \\ 0 \end{pmatrix}.$$

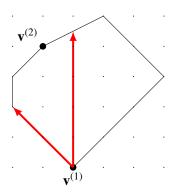

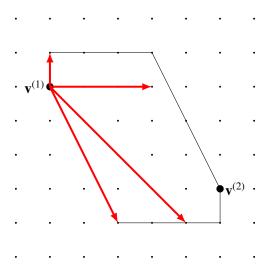

We want to perform a circuit walk from  $\mathbf{v}^{(1)} = (2, -2)^{\mathsf{T}}$  to  $\mathbf{v}^{(2)} = (1, 2)^{\mathsf{T}}$ . We have  $B \cdot \left( \mathbf{v}^{(2)} - \mathbf{v}^{(1)} \right) = (-1, 3, -5, -6)^{\mathsf{T}}$ . The only sign-compatible circuits are  $(0, 1)^{\mathsf{T}}$  (as  $B \cdot (0, 1)^{\mathsf{T}} = (0, 1, -1, -2)^{\mathsf{T}}$ ) and  $(-1, 1)^{\mathsf{T}}$  (as  $B \cdot (-1, 1)^{\mathsf{T}} = (-1, 0, 2, 3)^{\mathsf{T}}$ ). But choosing the directions  $(0, 1)^{\mathsf{T}}$  and  $(-1, 1)^{\mathsf{T}}$ , respectively, as a first feasible maximal circuit step at  $\mathbf{v}^{(1)}$  we arrive at  $(0, 0)^{\mathsf{T}}$  and  $(2, 2\frac{1}{2})^{\mathsf{T}}$ , respectively. From neither of these points we can go to  $\mathbf{v}^{(2)}$  using only the circuits  $(0, 1)^{\mathsf{T}}$  and  $(-1, 1)^{\mathsf{T}}$ , which are the only ones that are sign-compatible with  $\mathbf{v}^{(2)} - \mathbf{v}^{(1)}$ .

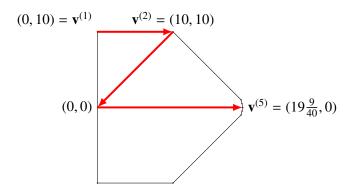

Figure 2.1: All feasible maximal circuit steps at  $\mathbf{v}^{(1)}$  that are sign-compatible with  $\mathbf{v}^{(2)} - \mathbf{v}^{(1)}$ .

In contrast, we already know from our discussion in the previous chapter that any two vertices of a polyhedron  $P = \{ \mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$  are connected by a feasible sign-compatible circuit walk if we allow arbitrary length steps, and thus  $\mathcal{CD}_{fs}$  is well-defined (see Proposition 1.4). In Lemma 2.18 we will further prove that there are good upper bounds on the length of such walks.

#### 2.1.3 Fundamental observations

First of all, let us point out that there are classes of polyhedra for which all notions of circuit diameters coincide: In simplices any two vertices are connected by an edge and thus all circuit diameters are just one. Further, for any *n*-dimensional zonotope, all circuit diameters equal *n*; the *n*-dimensional cube is a particularly simple special case. Recall that a zonotope is point-symmetric with respect to its center of gravity. Vertices that correspond to each other with respect to this point symmetry are connected by an edge walk of length exactly *n*. Using any set of circuits and no restrictions on the walk we cannot do any better, as the circuits here correspond to the actual, existing edge directions.

We continue with some elementary characteristics of circuit walks and circuit distances.

#### Reversible circuit walks

Given a circuit walk from a vertex  $\mathbf{v}^{(1)}$  to a vertex  $\mathbf{v}^{(2)}$  we get a circuit walk from  $\mathbf{v}^{(2)}$  to  $\mathbf{v}^{(1)}$  by simply reversing the steps. This obviously preserves the properties feasible ( $\mathbf{f}$ ), non-repetitive ( $\mathbf{r}$ ), non-backwards ( $\mathbf{b}$ ) and sign-compatible ( $\mathbf{s}$ ), and it turns an edge walk into another edge walk ( $\mathbf{e}$ ). Thus, circuit walks of all categories except  $\mathcal{CD}_{fm(b)(r)}$  are reversible. In particular the corresponding distances are *symmetric*, that is, a certain circuit distance from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  coincides with the respective circuit distance from  $\mathbf{v}^{(2)}$  to  $\mathbf{v}^{(1)}$ . But if we do not have an edge walk, maximality ( $\mathbf{m}$ ) is not necessarily maintained and thus circuit walks of type  $\mathcal{CD}_{fm(b)(r)}$  are not always reversible, neither is the distance symmetric, as illustrated in the following example.

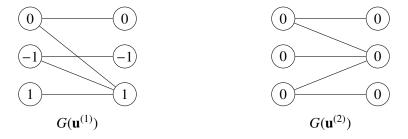

**Example 2.2.** Consider the polyhedron

$$P = \{ \mathbf{x} \in \mathbb{R}^2 : \mathbf{l} < B\mathbf{x} < \mathbf{u} \}$$

given by

$$B = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 1 & 1 \\ 1 & -1 \end{pmatrix}, \quad \mathbf{l} = \begin{pmatrix} 0 \\ -\infty \\ 0 \\ -1 \end{pmatrix}, \quad \mathbf{u} = \begin{pmatrix} \infty \\ 2 \\ 4 \\ 6 \end{pmatrix}.$$

P is a two-dimensional polytope with six vertices whose circuits are given by

$$C_{\leq}(B) = \left\{ \pm \left( \begin{array}{c} 0 \\ 1 \end{array} \right), \pm \left( \begin{array}{c} 1 \\ 0 \end{array} \right), \pm \left( \begin{array}{c} 1 \\ -1 \end{array} \right), \pm \left( \begin{array}{c} 1 \\ 1 \end{array} \right) \right\} \ ,$$

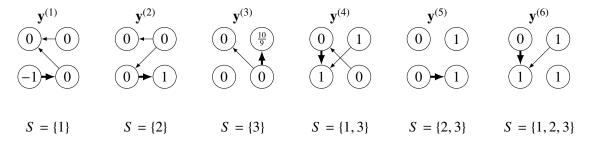

as these are obviously all possible edge directions (the polytope is depicted in Figure 2.2). Let us have a look at circuit walks between  $\mathbf{v}^{(1)}$  and  $\mathbf{v}^{(2)}$ .

Figure 2.2: An optimal circuit walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  and the reversed walk.

The walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  is maximal, but the reversed walk is not. We can even show that there is no feasible maximal circuit walk of length two from  $\mathbf{v}^{(2)}$  to  $\mathbf{v}^{(1)}$  and thus the circuit distances  $\mathcal{CD}_{fm}$  do not coincide. To see this, we illustrate all maximal feasible circuit steps that could be applied at  $\mathbf{v}^{(2)}$ .

Figure 2.3: Feasible maximal circuit steps at  $\mathbf{v}^{(2)}$ .

No matter which circuit direction we choose for a first maximal step starting at  $\mathbf{v}^{(2)}$ , we cannot go to  $\mathbf{v}^{(1)}$  with only one more step.

#### Commutative circuit walks

Given a circuit walk from a vertex  $\mathbf{v}^{(1)}$  to a vertex  $\mathbf{v}^{(2)}$  we can construct alternative circuit walks from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  by rearranging the circuit steps. We say that a circuit walk is *commutative* if it does not matter in which order we apply the steps; all circuit walks obtained by rearranging fall into the same category as the original one.

While circuit walks in general have to be regarded as ordered sequences of vectors, commutative walks can be interpreted simply as linear combinations of the form  $\mathbf{v}^{(2)} - \mathbf{v}^{(1)} = \sum_{i=1}^{k} \alpha_i \mathbf{g}^i$  for circuits  $\mathbf{g}^i$ . In particular, the non-restricted walks of type CD are commutative and thus, in a way, the soft circuit distance CD is just a linear algebra bound on the diameter given in terms of the support (or number of elements) of a linear combination of circuits.

It is not hard to see that almost all other types of circuit walks are not commutative as in general rearranging does not preserve feasibility. However, this is the case for sign-compatible circuit walks: It follows immediately from the representation  $\mathbf{v}^{(2)} = \mathbf{v}^{(1)} + \sum_{i=1}^{k} \alpha_i \mathbf{g}^i$  for circuits  $\mathbf{g}^i$  that are sign-compatible with  $\mathbf{v}^{(2)} - \mathbf{v}^{(1)}$  and thus satisfy  $\operatorname{supp}(B\mathbf{g}^i) \subseteq \operatorname{supp}(B(\mathbf{v}^{(2)} - \mathbf{v}^{(1)}))$ .

This significant observation shows that sign-compatibly is a natural and extremely useful property for circuit walks. For example, in [18] sign-compatible walks play a crucial role in showing that there is a selection strategy such that only polynomially many circuit augmentation steps are needed to reach an optimal solution (recall that this is still unresolved for the Simplex method). However, it is still open how to implement this greedy-type augmentation oracle in polynomial time.

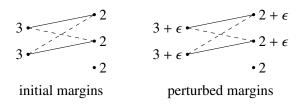

## Perturbing the right-hand side

Recall that it suffices to consider generic polyhedra to bound the combinatorial diameter, as by a perturbation any polyhedron can be turned into a generic one whose diameter is at least as big as that of the original polyhedron. It is not clear whether the same is true for the other notions circuit diameters.

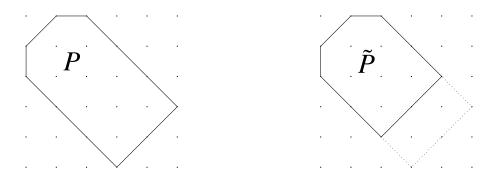

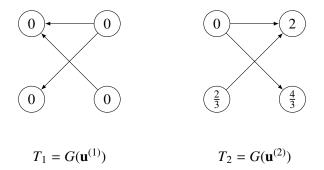

In the following example we will see that a perturbation of the right-hand side vector might affect the circuit diameter in a way that is hard to predict. In particular, it may change the circuit diameter while keeping the combinatorial structure of the polyhedron. Note that such a perturbation does not change the set of circuits.

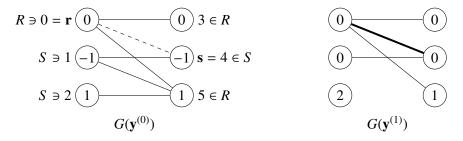

## **Example 2.3.** Consider the polyhedron

$$\tilde{P} = \{ \mathbf{x} \in \mathbb{R}^2 : \mathbf{l} \leq B\mathbf{x} \leq \tilde{\mathbf{u}} \}$$

given by

$$B = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 1 & 1 \\ 1 & -1 \end{pmatrix}, \quad \mathbf{l} = \begin{pmatrix} 0 \\ -\infty \\ 0 \\ -1 \end{pmatrix}, \quad \tilde{\mathbf{u}} = \begin{pmatrix} \infty \\ 2 \\ 4 \\ 4 \end{pmatrix},$$

and the polyhedron P as defined in Example 2.2. As P and  $\tilde{P}$  are both defined by the matrix B, these polyhedra possess the same sets of circuits. Further they have identical combinatorial structure:

Figure 2.4: Two polyhedra with same combinatorial structure.

As already seen in Example 2.2, the circuit diameter  $CD_{fm}$  of P equals three. In contrast, it can easily be checked that in  $\tilde{P}$  any two vertices can be connected by a feasible maximal circuit walk of length at most two.

## 2.2 The circuit distance hierarchy

We now turn to the main result of this chapter - our hierarchy of circuit distances. Observe that the results on the circuit distances readily transfer to statements about the circuit diameters of polyhedra. Thus, we can equally view it as a hierarchy of circuit diameters.

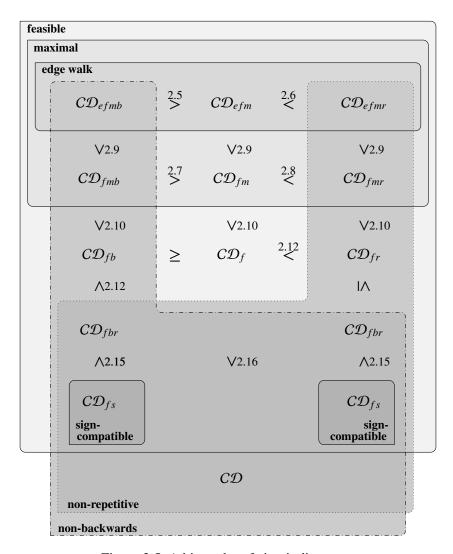

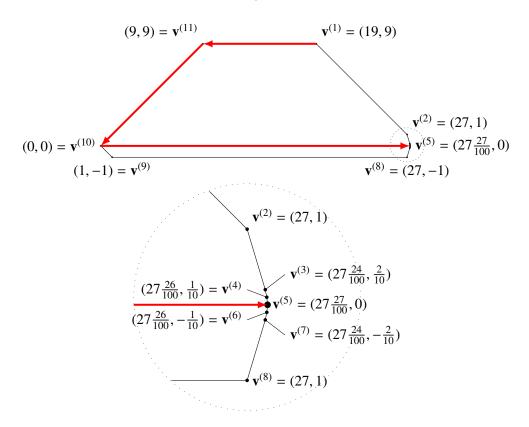

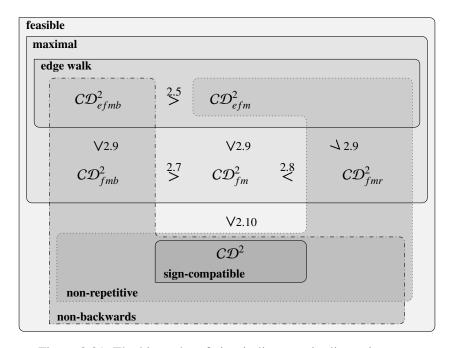

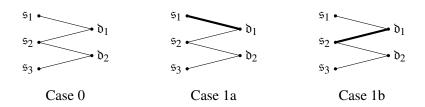

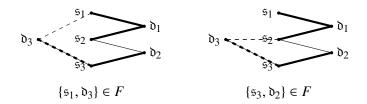

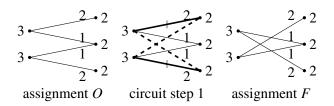

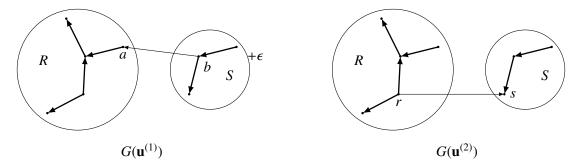

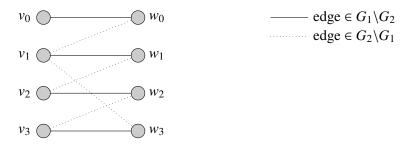

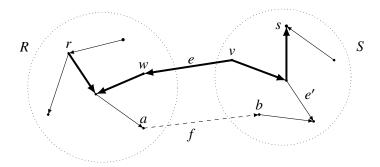

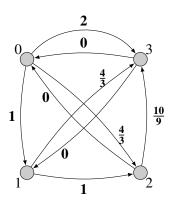

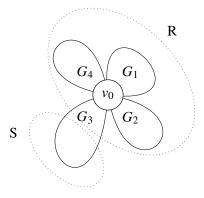

**Theorem 2.4.** The circuit distances satisfy a hierarchy as depicted in Figure 2.5.

This hierarchy states the relations between certain categories of circuit distances that arise from combining the properties introduced in the previous section. We want to point out that these categories are indeed a viable choice: We are able to prove that almost all circuit distances in the hierarchy are distinct (as we have '>') and our discussion in Section 2.1.2 showed that we included all relevant classes. Note that for sake of having a clear layout the lower left and lower right parts refer to the same categories  $\mathcal{CD}_{fbr}$  and  $\mathcal{CD}_{fs}$ . Distance notions that share properties are grouped in boxes.

The remaining section is concerned with the proof of Theorem 2.4. We have to show that the distances indeed satisfy the claimed relations. For most of the 'weak' inequalities this follows immediately as we are just imposing additional constraints. In order to prove the 'strict' inequalities, we exhibit polytopes with pairs of vertices  $v^{(1)}$ ,  $v^{(2)}$  for which the lengths of optimal walks with the respective properties indeed differ. The numbers at the '<' -symbols refer to the lemmas that show these strict inequalities.

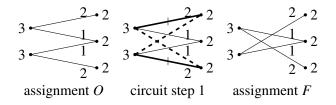

Figure 2.5: A hierarchy of circuit distances.

The top horizontal layer of the table contains the distances defined on edge walks. An edge walk always is both feasible and maximal, so there are only combinations that contain all of these properties at the same time. We distinguish between  $C\mathcal{D}_{efm}$  and  $C\mathcal{D}_{efmb}$ ,  $C\mathcal{D}_{efmr}$ . Recall that  $C\mathcal{D}_{efms}$  is not included in the hierarchy as it is not necessarily well-defined, see Lemma 2.1. Same holds for  $C\mathcal{D}_{fms}$ . As we just impose additional constraints we immediately get  $C\mathcal{D}_{efmb} \geq C\mathcal{D}_{efm}$  and  $C\mathcal{D}_{efmr} \geq C\mathcal{D}_{efm}$ . The following two Lemmas show that allowing the opposite or the repeated use of an edge direction can indeed yield a shorter edge walk and thus we have strict inequalities.

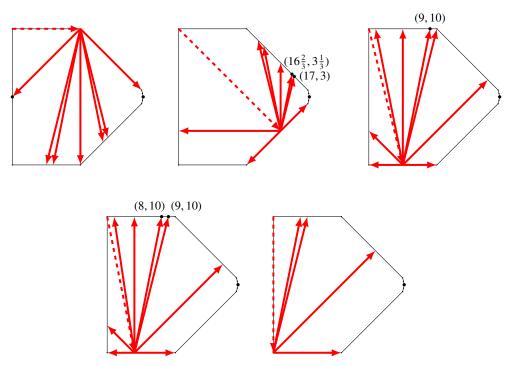

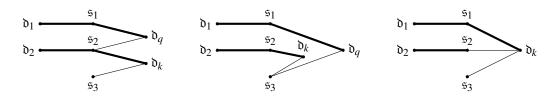

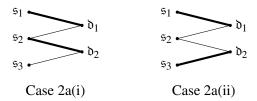

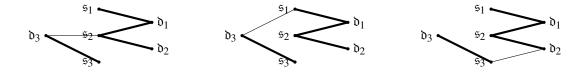

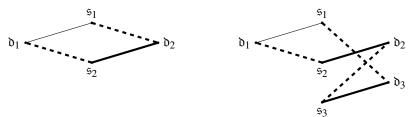

**Lemma 2.5** ( $CD_{emfb} > CD_{efm}$ ). For n = 2, there is a polytope with a pair of vertices for which the unique optimal edge walk is backwards. Hence the distances  $CD_{efmb}$  and  $CD_{efm}$  differ in this case.

*Proof.* In the polytope below, the unique non-backwards edge walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  has length four, while there is an edge walk of length three that uses edges in opposite directions.

Figure 2.6: An optimal non-backwards edge walk and a backwards edge walk.

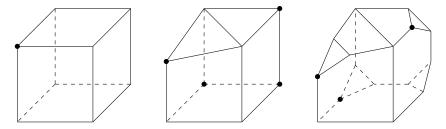

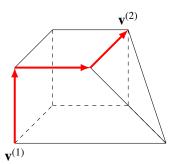

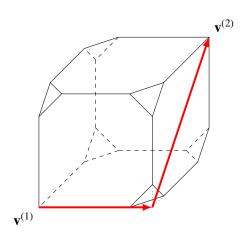

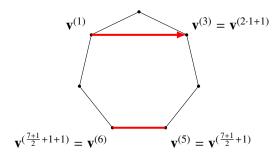

**Lemma 2.6** ( $CD_{efmr} > CD_{efm}$ ). For n = 3, there is a polytope with a pair of vertices for which the unique optimal edge walk is repetitive. Hence the distances  $CD_{efmr}$  and  $CD_{efmr}$  differ in this case.

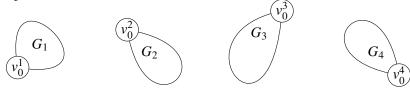

*Proof.* We construct a polytope with the claimed property by cutting off vertices of a three-dimensional cube as illustrated in the following figures:

Figure 2.7: Constructing the polytope by cutting off vertices (marked with dots).

We obtain the polytope below, in which there is a repetitive edge walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  of length four. It is easy to check that any other edge walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$  has length at least five.

Figure 2.8: Unique optimal edge walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(2)}$ .

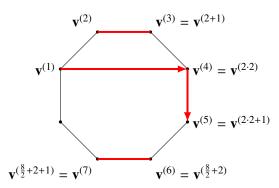

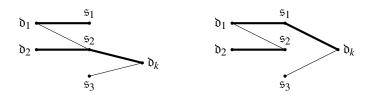

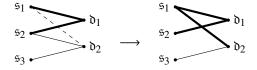

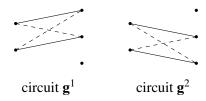

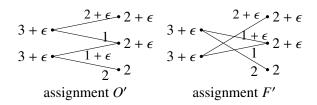

We now relax the constraint (e) and allow circuit walks through the interior of the polyhedron. For feasible maximal circuit walks we again distinguish between  $CD_{fm}$  and  $CD_{fmb}$ ,  $CD_{fmr}$ . In Lemmas 2.7 and 2.8 we prove that these concepts do not coincide. We first exhibit a polytope in which going backwards yields shorter circuit walks, that is,  $CD_{fm} < CD_{fmb}$ .

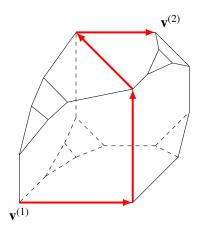

**Lemma 2.7** ( $CD_{fmb} > CD_{fm}$ ). For n = 2, there is a polytope with a pair of vertices for which every optimal feasible maximal circuit walk is backwards. Hence the distances  $CD_{fmb}$  and  $CD_{fm}$  differ in this case.

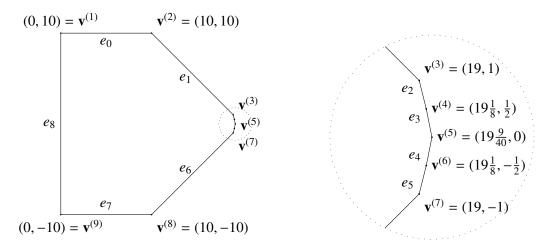

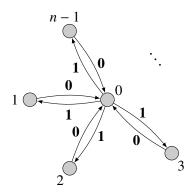

*Proof.* We consider the polytope on 11 vertices depicted in Figure 2.9; the lower subfigure is a zoomed-in view on the right part of the polygon. The edge directions are given by

$$\binom{1}{1}$$

,  $\binom{1}{0}$ ,  $\binom{-1}{1}$ ,  $\binom{3}{-10}$ ,  $\binom{2}{-10}$ ,  $\binom{1}{-10}$ ,  $\binom{1}{10}$ ,  $\binom{2}{10}$ ,  $\binom{3}{10}$ .

There is a feasible maximal circuit walk of length three from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(5)}$  that is backwards.

Figure 2.9: A polytope with a feasible maximal backwards circuit walk of length three.

Every other feasible maximal circuit walk from  $\mathbf{v}^{(1)}$  to  $\mathbf{v}^{(5)}$  has length at least four. To see this, we illustrate all possible combination of first (dashed) and second feasible maximal circuit steps in Figure 2.10. From none of these second step points we can reach  $\mathbf{v}^{(5)}$  in only one additional step, except from the point  $\mathbf{v}^{(10)}$  in the top left picture. But this yields the backwards circuit walk

depicted in Figure 2.9. Observe that all second steps that end in the upper edge  $(\mathbf{v}^{(11)}, \mathbf{v}^{(1)})$  have coordinates  $(x, 9)^{\mathsf{T}}$  for an *integral* x, and thus we cannot reach  $\mathbf{v}^{(5)} = (27\frac{27}{100}, 0)^{\mathsf{T}}$  by applying the circuit  $(-1, 1)^{\mathsf{T}}$  at these points. The final sketch is a zoomed-in view on the bottom right picture. It illustrates all possible second steps after applying  $(-1, 1)^{\mathsf{T}}$  at  $\mathbf{v}^{(1)}$  for a convenient verification of the fact that we cannot get to  $\mathbf{v}^{(5)}$  with only one more step.

Figure 2.10: Possible combinations of first and second feasible maximal circuit steps from  $\mathbf{v}^{(1)}$ .

Likewise, one may obtain a shorter circuit walk by allowing oneself to use a circuit twice, and thus  $\mathcal{CD}_{fm} < \mathcal{CD}_{fmr}$ .

**Lemma 2.8** ( $CD_{fmr} > CD_{fm}$ ). For n = 2, there is a polytope with a pair of vertices for which every optimal feasible maximal circuit walk is repetitive. Hence the distances  $CD_{fmr}$  and  $CD_{fm}$  differ in this case.

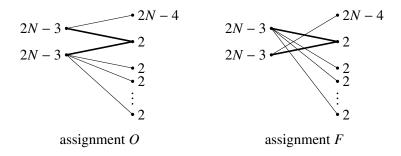

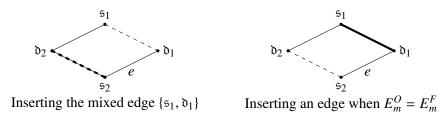

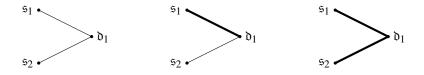

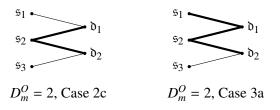

28