# TECHNISCHE UNIVERSITÄT MÜNCHEN

# Lehrstuhl für Rechnertechnik und Rechnerorganisation

#### **Automated Design of Computer Clusters**

### Konstantin S. Solnushkin

Vollständiger Abdruck der von der Fakultät für **Informatik** der Technischen Universität München zur Erlangung des akademischen Grades eines Doktors **der Naturwissenschaften**

genehmigten Dissertation.

| Vorsitzender:            | UnivProf. Dr. Martin Bichler           |

|--------------------------|----------------------------------------|

| Prüfer der Dissertation: | UnivProf. Dr. Arndt Bode               |

|                          | UnivProf. Dr. Dieter Kranzlmüller,     |

|                          | Ludwig-Maximilians-Universität München |

Die Dissertation wurde am 17.09.2014 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 16.12.2014 angenommen.

# FAKULTÄT FÜR INFORMATIK

# DER TECHNISCHEN UNIVERSITÄT MÜNCHEN

Dissertation

# Automated Design of Computer Clusters

# Automatisierter Entwurf von Rechnerclustern

| Author:     | Konstantin S. Solnushkin                        |

|-------------|-------------------------------------------------|

| Supervisor: | UnivProf. Dr. Arndt Bode                        |

| Advisor:    | UnivProf. Dr. Dieter Kranzlmüller (LMU München) |

| Date:       | September 17, 2014                              |

Ich versichere, dass ich diese Dissertation selbständig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe.

München, den 17. September 2014

Konstantin S. Solnushkin

# Acknowledgements

Ever since my childhood, I wanted to become a scientist. On my way to this ambitious goal, I met a lot of wonderful people who provided me with help and guidance. In this section, I try to give them a due credit.

It all started in 2005 when I became a PhD student at the Saint Petersburg State Polytechnic University. Professor Valery D. Masin, who supervised my MSc thesis, agreed to become my PhD advisor. By that time, I have already worked as a system administrator at the university's computing centre for a couple of years. We were actively procuring computer clusters but had difficulties determining an optimal configuration of these machines to suit our tasks. Therefore, a topic of the dissertation emerged naturally: designing cost-efficient computer clusters.

I started to work tirelessly, presenting at conferences and publishing in journals. My colleagues at the computing centre gave me enough time to pursue science. At my department, I participated in PhD seminars, receiving useful feedback from fellow students and professors. I also drew a lot from lectures on the philosophy of science and scientific discovery, delivered by wise professors: Konstantin K. Gomoyunov, Alexander A. Krauze, and Vadim G. Knorring.

But despite all the hard work, the progress was not very visible. My grandmother always met me with the question, when will I produce the first page of my thesis? I evaded a direct answer, quoting the number of papers and conference proceedings. The figures were impressive, but I was only a bit closer to my goal than in the beginning, because I apparently tried to "embrace the unembraceable".

Cruel fate dealt me a severe blow when, in the beginning of 2008, two and a half years into my PhD term, my grandmother passed away. I was condemning myself, since I was unable to produce even the first page of the thesis that she so frequently had asked me about. My research work only continued through inertia. I tried to find solace in my everyday job. The prospects were becoming grim, or so it appeared.

It was only in the December of 2009 when I saw the light at the end of the tunnel. Professor Vyacheslav P. Shkodyrev invited me to participate in the "School on Granular Computing" in Erice, Italy, organised by Prof. Dr. Bruno Apolloni and his younger colleague, Dr. Simone Bassis, both from the University of Milan. This event was an eye-opener, a week of pure joy, excitement and scientific discovery. I met many new people and learned many new things. Quotation of Prof. Apolloni has become an epigraph to Chapter 1, "Introduction". An amazing class on interval computation by Prof. Dr. Vladik Kreinovich from the University of Texas at El Paso inspired me to use the methods of interval arithmetic in this thesis: see section 6.4. The School breathed a new life into me. I saw how international – and European – science operates, and wanted to be a part of it. I revived my research work, and in April of 2011 I visited a PRACE conference in Helsinki, Finland. There I met Dr. Markus Rampp from Rechenzentrum Garching and shared my concerns about completing my PhD in Europe. Markus proposed that I ask Prof. Dr. Arndt Bode to become my PhD advisor. That conversation became another turning point in my life.

Luckily, upon seeing my existing work, Prof. Bode agreed to become my advisor for the next three long years. I promised to complete the PhD as soon as possible, perhaps in a few months, but many times I found new branches worth exploring. I am deeply grateful to Prof. Bode for not urging me with my work and being patient and considerate.

Presenting at international conferences, I met many colleagues, young and old, and these acquaintances helped me see new directions in my scientific work and get in touch with knowledgeable senior colleagues. I am thankful to Dr. José Duato who provided insightful comments on the fat-tree design algorithm in Chapter 13.

Prof. Dr. Dieter Kranzlmüller from Ludwig-Maximilians-Universität München became a thesis co-advisor. Finally, it was time to complete the activities and submit the thesis. Here, invaluable help was provided by Mrs. Manuela Fischer, the secretary of the dean of the Informatics faculty. She supported me in all administrative matters, and we exchanged over one hundred e-mails since my enrolment in the PhD program.

Last but not least, I want to mention my parents and relatives – especially my mother and grandmother – who believed in what I was doing during all these years. At times, I lost hope, but my whole family supported me, both psychologically and financially, no matter what. I dedicate this thesis to the memory of my grandmother; I wish she could be here and share my success with me.

# Abstract

Computer clusters made of mass-produced, off-the-shelf components are able to deliver the same real-life performance on a variety of tasks as other types of supercomputers, but at a lower cost. Current ad hoc design practices are characterised by only partial exploration of design space and inability to accurately predict capital and operating expenses. We provide the framework for a more comprehensive design space exploration, paving the way to a future CAD system for computer clusters and warehouse-scale computers with decision support and "what if" analysis capabilities.

We formulate the design task as a discrete combinatorial optimisation problem, with the non-linear objective function being the ratio of total cost of ownership to real-life performance. Although complex, the objective function allows for an unbiased assessment of proposed design alternatives. Various constraints can be imposed on technical and economic characteristics of the computer cluster, including minimal performance, maximal capital and operating expenses, power consumption, occupied space, etc.

Obtaining the value of the objective function is only possible after several consecutive stages of design process are completed: choosing an optimal configuration of a single compute node, designing interconnection network and a power supply system, etc. We provide a prototype CAD tool that implements these stages. We also propose heuristics to deal with combinatorial explosion at various stages.

# Zusammenfassung

# Automatisierter Entwurf von Rechnerclustern

Rechnercluster aus Standardkomponenten können für eine Vielzahl von Anwendungen vergleichbare Rechenleistung bieten wie spezielle Supercomputer, jedoch zu einem besseren Preis-Leistungsverhältnis. Heutige Adhoc-Entwürfe sind charakterisierbar durch beschränkte Auswertung des Entwurfsraums und die Unfähigkeit, Investitionskosten und Betriebskosten korrekt vorherzusagen. Im Rahmen dieser Arbeit wird eine Methode zur besseren Auswertung des Entwurfsraums vorgeschlagen, die die Basis für künftige automatisierte Entwurfssysteme für Rechnercluster auf Basis von Standardkomponenten darstellen können und entsprechende Entscheidungsunterstützungssysteme beinhalten.

Die Aufgabe des Entwurfs wird dabei als diskretes kombinatorisches Optimierungsproblem formuliert, wobei die nichtlineare Zielfunktion das Verhältnis zwischen Gesamtkosten und Rechenleistung für reale Anwendungen beschreibt. Trotz hoher Komplexität erlaubt die Zielfunktion eine klare Analyse möglicher Entwurfsalternativen. Verschiedenste Randbedingungen für technische und wirtschaftliche Eigenschaften des Rechenclusters können formuliert werden, wie z.B. minimale Rechenleistung, maximale Herstellungskosten und Betriebskosten, Leistungsaufnahme, Raumanforderungen, usw.

Der Wert der Zielfunktion kann erst bestimmt werden, wenn mehrere konsekutive Schritte des Entwurfsprozesses fertiggestellt sind: Auswahl der optionalen Konfiguration des einzelnen Rechenknotens, Entwurf des Verbindungsnetzwerks, der Stromversorgung usw. Im Rahmen der Arbeit wird der Prototyp eines automatisierten Entwurfswerkzeuges realisiert, der diese Arbeitsschritte implementiert. Weiterhin werden Heuristiken entwickelt, die mit der kombinatorischen Explosion die verschiedenen Schritte eingrenzt.

# Contents

| Acknowledgements |                                                                                                                                                                                                                                                                                         | vii                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Ał               | bstract                                                                                                                                                                                                                                                                                 | ix                                            |

| I.               | Introduction and Problem Statement                                                                                                                                                                                                                                                      | 1                                             |

| 1.               | Introduction1.1. Motivation1.2. Benefits of Automated Design Space Exploration1.3. A System-Level Complement to EDA1.4. Generality of Approach                                                                                                                                          | <b>3</b><br>3<br>4<br>6<br>7                  |

| 2.               | Related Work         2.1.       McDermott, 1980                                                                                                                                                                                                                                         | <b>9</b><br>9<br>10<br>11<br>12<br>13         |

| 3.               | Problem Statement3.1. Problem Statement3.2. Defining a Configuration3.3. Representing Configurations with Multipartite Graphs3.4. Algorithm for Designing Computer Clusters3.5. Combinatorial Explosion3.6. Interdependencies3.7. Proposed Design Framework as a Means of Collaboration | <b>15</b><br>15<br>16<br>18<br>19<br>20<br>21 |

| 4.               | Outline of the Thesis                                                                                                                                                                                                                                                                   | 23                                            |

| 5.               | Scientific Contribution         5.1. CAD systems         5.2. Performance modelling         5.3. Computer networks         5.4. Data centre design         5.5. Cooling systems         5.6. Economics                                                                                  | 27<br>27<br>27<br>27<br>27<br>27<br>28<br>28  |

| II. | Criterion Function and Design Constraints                                                                                                                                                                                                          | 29                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 6.  | <ul> <li>Choice of the Criterion Function</li> <li>6.1. Multi-Objective Optimisation</li></ul>                                                                                                                                                     | 32                                      |

| 7.  | Economics of Cluster Computing7.1. From Innovative to Commodity Technologies7.2. Questions of Balance7.3. Total Cost of Ownership and Its Components7.4. Aggregate and Specific Characteristics7.5. Public Spending Issues                         | <b>39</b><br>39<br>40<br>45<br>49<br>50 |

| 8.  | Dealing with Combinatorial Explosion8.1. Sources of Combinatorial Explosion8.2. Heuristics8.3. Design Constraints8.4. The Case Against Local Optimisations                                                                                         | 56                                      |

| 9.  | Performance Modelling         9.1. Related Work                                                                                                                                                                                                    | 65<br>66<br>69                          |

| III | . Automated Design of Computer Clusters                                                                                                                                                                                                            | 75                                      |

| 10  | Graph Representation of Configurations10.1. Undirected vs. Directed Graphs10.2. Expression Evaluation During Graph Traversal10.3. Graph Transformations10.4. Defining Software Configurations with Graphs10.5. XML Syntax for Graph Representation |                                         |

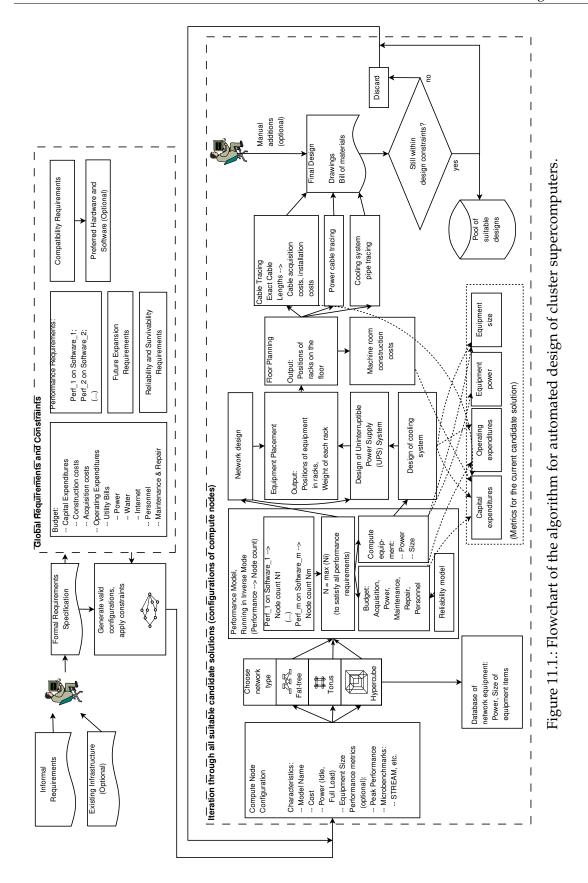

| 11. | Algorithm for Automated Design of Cluster Supercomputers11.1. Generating Candidate Solutions                                                                                                                                                       | <b>87</b><br>87<br>88<br>88<br>91<br>93 |

| 12. | <b>. CAD System for Computer Clusters</b><br>12.1. Overall Structure of the Main CAD Application                                                                                                                                                   | <b>95</b><br>95                         |

| 12.2. "Performance" Tab                                       | 97  |

|---------------------------------------------------------------|-----|

| 12.3. "Network" Tab                                           | 98  |

| 12.4. "UPS" Tab                                               | 99  |

| 12.5. "Design" Tab                                            | 99  |

| 12.6. Module Invocation Sequence                              | 102 |

| 12.7. Parallelisation Strategy for the CAD Tool               | 103 |

|                                                               |     |

| 13. Fat-tree Network Design                                   | 105 |

| 13.1. Introduction                                            | 105 |

| 13.2. Related Work                                            | 106 |

| 13.3. Algorithm                                               | 107 |

| 13.4. Discussion                                              | 112 |

| 13.5. Experimental Results                                    | 113 |

| 13.6. Per-port Metrics                                        | 114 |

| 13.7. Designing for Future Expansion                          | 115 |

| 13.8. Conclusions                                             | 117 |

|                                                               | 117 |

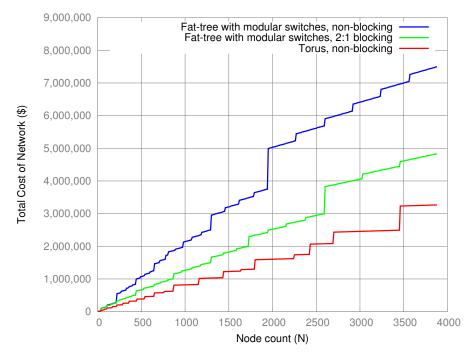

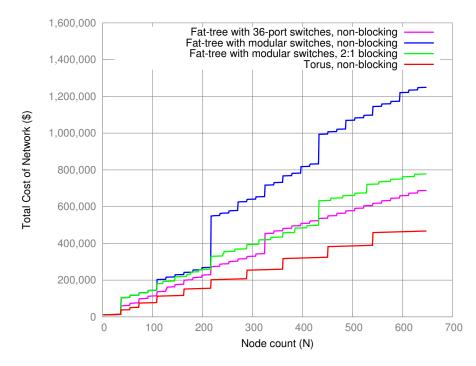

| 14. Torus Network Design                                      | 119 |

| 14.1. Related Work                                            | 119 |

| 14.2. 3D Dual-rail Torus Network of the Gordon Supercomputer  | 119 |

| 14.3. Algorithm for Designing Torus Networks                  | 120 |

| 14.4. Cost Comparison of Torus and Fat-tree Networks          | 120 |

|                                                               | 141 |

| 15. Designing Other Subsystems of Computer Clusters           | 127 |

|                                                               | 127 |

| 0 0                                                           | 128 |

| 15.3. Cooling System                                          | 129 |

| 15.4. Calculating Partial Cooling Capacity                    | 131 |

| 15.5. Comparing Cooling Solutions                             | 134 |

| 15.6. Liquid-based Cooling Methods                            | 135 |

| 15.7. Waste Heat Reuse                                        | 135 |

|                                                               |     |

| 15.8. Power Supply System                                     | 138 |

| 15.9. Algorithm for UPS Design                                | 138 |

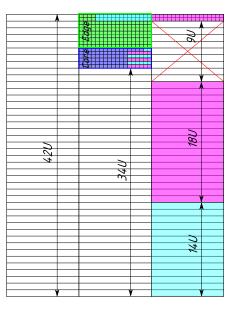

| 16. Equipment Placement and Floor Planning                    | 145 |

| 16.1. Partitioning Strategies: Consolidation vs. Distribution | 145 |

| · ·                                                           | 145 |

| 16.2. Distributed Structure for High Survivability            |     |

| 16.3. Equipment Placement Heuristics                          | 146 |

| 16.4. Algorithm for Floor Planning                            | 150 |

| 17. Practical Evaluation of the Algorithm                     | 155 |

| 6                                                             | 155 |

| 17.1. Overview of Equipment                                   | 155 |

| 17.2. Characteristics of Individual Compute Nodes             |     |

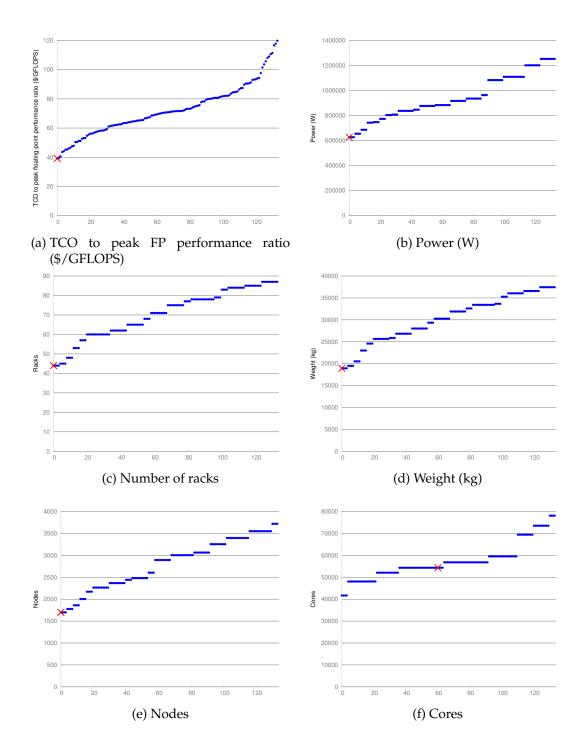

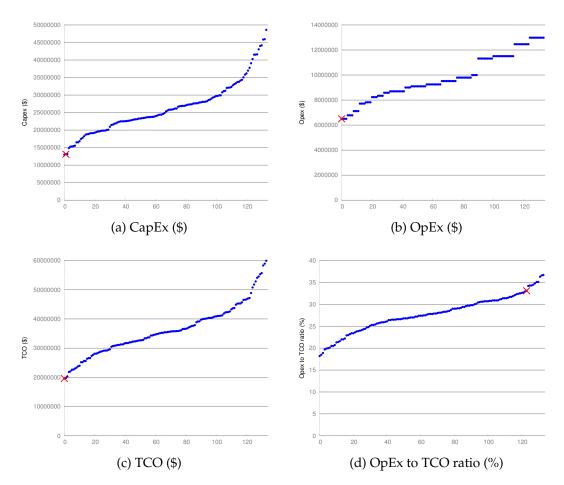

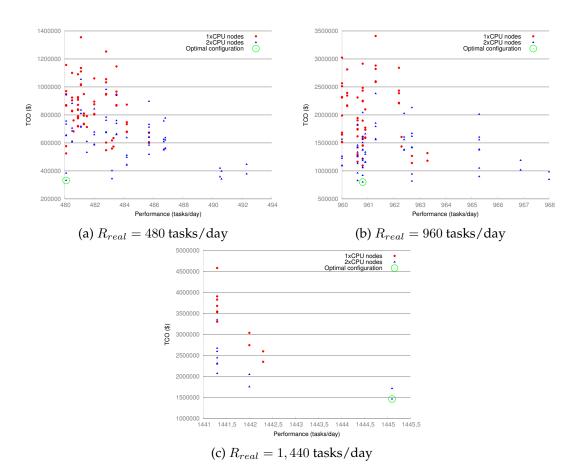

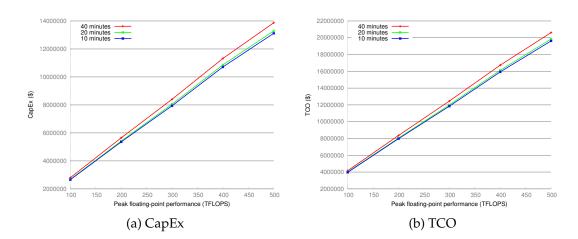

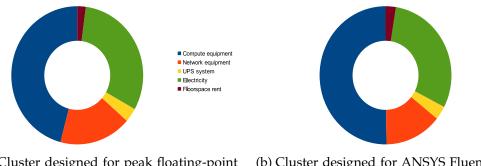

| 17.3. Designing for Peak Performance Requirements             | 159 |

| 17.4. Designing for ANSYS Fluent Performance Requirements     | 162 |

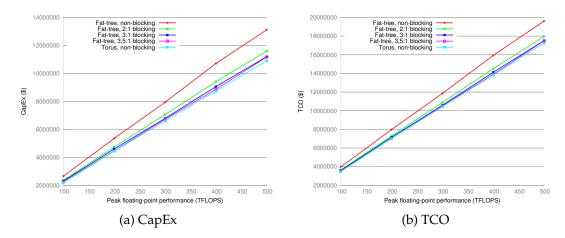

| 17.5. Impact of Network Topology and Blocking Factor          | 165 |

| 17.6. Impact of UPS Backup Time                                                        |     |

|----------------------------------------------------------------------------------------|-----|

| <b>18. Summary and Future Directions</b> 18.1. Summary         18.2. Future Directions |     |

| Appendices                                                                             |     |

| A. ANSYS Fluent Benchmark Data                                                         | 179 |

| B. Hardware of Compute Nodes                                                           | 181 |

| Bibliography                                                                           | 183 |

# Part I.

# **Introduction and Problem Statement**

# 1. Introduction

To those who are called upon to make decisions, practically the whole of mankind, politicians included. Faced with necessarily granular information, we don't expect people to arrive at the optimum decision. But we demand that they make reasonable choices.

> Prof. Dr. Bruno Apolloni University of Milan

In this chapter we introduce the reader to the task of synthesis of cluster supercomputers. Design procedures result in good, and under certain conditions even mathematically optimal solutions. Extended discussion of optimality is available in section 11.4.

We also explain why the design process should be automated, and show the connection between our task and the field of Electronic Design Automation (EDA).

# 1.1. Motivation

Computer clusters made of mass-produced, off-the-shelf components have been successful since their emergence in the early 1990s. Having continuously earned high rankings in the TOP500 list [81], they are able to deliver the same real-life performance on a variety of tasks as other types of supercomputers — but at a lower cost.

The off-the-shelf components that serve as the basis for computer clusters are available in great assortment. This means that a basic building block – a compute node – can have many different configurations. Every component, like Central Processing Unit (CPU), memory, local storage device or hardware accelerator, can be present in a compute node in different types and quantities. Even if two nodes have similar sets of inside components, they still can vary greatly in their mechanical characteristics, such as size and weight, which depends on packaging: rack-mounted versus blade servers.

For every distinct compute node configuration, building a compute cluster out of these nodes requires several stages. The first is choosing the number of compute nodes: it should be large enough to satisfy performance constraints, but still should not violate budget constraints. Then storage is added, and a network is designed to connect compute nodes together and to the storage. Finally, equipment is placed into racks, and cables are routed. Every of this stages can be implemented in several ways, which essentially yields a combinatorial optimisation problem. Additionally, a solution to this problem is subject to many constraints, e.g., physical size and power consumption of the future supercomputer are often limited.

Therefore, a challenge exists to build an optimal supercomputer – the one that brings optimality to a certain criterion function while satisfying a set of design constraints.

Supercomputer vendors must be able to meet that challenge. The ability to accurately predict characteristics of a supercomputer is especially important for the bigger systems, when only a small prototype system can be built and evaluated before the bidding procedure with a prospective customer. Additionally, the biggest supercomputers are often based on novel ideas. In this case, many unconventional solutions can be proposed by designers, and evaluating their characteristics should be done automatically.

Currently government organisations are the primary consumers of the largest supercomputers. In the USA, supercomputers sponsored by the National Science Foundation should be procured according to the guidelines outlined in [33]. According to the document, requirements specification for the supercomputer issued by the procuring body should specify the minimum performance that a system has to achieve on a set of benchmarks.

The vendor, in turn, proposes a system that fits within performance, reliability and budgetary constraints. The figures should be obtained from prototype systems or be "estimated by well-justified extrapolation from analogous systems", as the guidelines term it.

The European entity, PRACE, summarised its procurement strategies in [76], citing similar requirements for the bidding process.

A vendor's ability to optimise hardware structure is crucial for winning a contract. For example, a poor initial choice of a CPU which is too expensive can lead to the necessity to choose a low-budget interconnection network, yielding a low performance of the whole system. Choosing a less expensive CPU leaves more funds for the network, and the resulting system may have a higher performance. Such decisions can only be made if designs can be quickly evaluated and compared, which calls for automation.

For scientists, who are today's prevalent users of supercomputers, the existence of such framework means better systems within the same budget.

# 1.2. Benefits of Automated Design Space Exploration

There is a complex interdependence between many factors that influence the design process. A set of components that looked promising in the beginning may eventually result in a design with unacceptable characteristics.

Given the wide assortment of off-the-shelf components, a single compute node can have tens of favourable configurations, and further design stages quickly add to thousands of combinations, each representing a different design, characterised by a number of technical figures (performance, power consumption, size, weight, etc.) and economic figures (procurement costs, total cost of ownership).

The amount of designs that need to be analysed is big, and major technical and economic characteristics for each design must be predicted using complex mathematical models. Existing vendor software tools [38, 44] do not provide required functionality. They check compatibility of user-supplied components and can calculate cost, size and power consumption of a design (but don't try to predict performance), and are unable to automatically iterate through many possible combinations.

Hence, these tools solve the direct problem: given a hardware configuration, assess its

(a) JUROPA, a supercomputer installed

in the Jülich Supercomputing Centre.

(b) Underfloor cables of JU-(Source: fz-juelich.de)

ROPA. (Source: fci.com)

Figure 1.1.: Cabling plans are essential for large installations

technical and economic characteristics. We need, however, to solve an inverse problem: given a set of constraints, determine a hardware configuration that is optimal in a certain sense. It is evident that the solution of the inverse problems involves solving a direct problem many times.

Therefore, a framework for automated design of computer clusters is required. In the absence of such a framework, ad hoc design practices are utilised. They are characterised by only partial exploration of design space and inability to accurately predict capital and operating expenses.

For example, a human designer may restrict one's attention to a specific part of design space due to reasons such as bias, personal preferences or simply lack of time.

Employing a Computer-Aided Design (CAD) system to automatically solve a design problem has many benefits. First, a complete exploration of the design space can be ensured, which eventually leads to better designs. The CAD system can evaluate architectures that a human designer would never consider due to one's stereotypes; can do it in less time, with less paperwork and without mistakes.

Second, all infrastructure components – storage, power, cooling – will be automatically taken care of. Tedious task of selecting a proper power supply and cooling systems for every candidate design can be commissioned to a CAD system. Choosing a different CPU model for a compute node can lead to a change in power consumption and therefore required cooling capacity for the entire system in the range of tens of percent. A CAD system will track these changes automatically.

Third, automated design leads to the capability of precise documentation being automatically generated. Not only will a resultant solution meet all design constraints, it will also have its network layout and floor plan available. All power and network cables, as well as cooling water pipes, can be automatically routed in a non-conflicting manner. Figure 1.1 illustrates benefits of cabling plans.

Fourth, automation is the only possible way to track a rapidly changing market situa-

tion. New components frequently appear on the supercomputing market. It also means that existing components become outdated, and their prices decrease. However, the decrease is temporary: when components are out of stock, they become hard to find, and in this situation of low supply the price increases according to market laws. Automation allows to choose an optimal hardware configuration which has the lowest price at a particular moment of time.

Finally, automation makes it possible, in principle, to estimate many auxiliary useful metrics, such as labour expenditures during the system installation.

# 1.3. A System-Level Complement to EDA

Engineers that design new microprocessors are always challenged with constraints and trade-offs. They can put more cache memory onto a die, but this will increase die size and production costs and decrease yield. They can make cores with a simple instruction set architecture and connect them with a simpler on-chip network, but this may have performance implications. Inflating clock frequency causes heat dissipation problems.

Designers of servers face similar challenges, although on a higher level. Instead of die surface constraints, they have size constraints of a printed circuit board (PCB). Traces on a PCB have to be carefully routed to reduce electromagnetic interference. Heat rejection issues stay important as well.

In this sense, design of supercomputers is a system-level complement to the above mentioned problems of electronic design automation. Even more interesting is that EDA approaches can be utilised to solve problems of cluster computer design. For example, partitioning components between boards in EDA is governed by the same algorithms as partitioning equipment between racks in cluster design. Routing of PCB traces is very similar to routing network cables in clusters. This continuity of ideas and approaches when moving to higher abstraction levels is remarkable. (Note that the placement problem – the problem of placing blocks on a VLSI die or placing components on a PCB – also has a correspondence in cluster design, in the form of placing racks in a machine room. It has, however, a much simpler formulation due to the fact that racks usually have identical dimensions).

In 2010, HiPEAC, the European initiative on architecture and compilation, described in its roadmap [26] the forthcoming shift of Electronic Design Automation to a new abstraction level, Electronic System Level, with one of key issues being "component-based design, from the basic building blocks up to the complete datacenter". This has much in common with our vision.

It is not far away from now when we will apply the principles of silicon compilers – used to automatically design silicon chips with particular structure and functions – to a whole new field of automated design of *complete machines* with particular structure and functions. We even might need new languages for this, like Verilog and VHDL that are used for silicon chips. The proposed framework moves us one step further to this future.

The quest for exascale systems is changing the landscape of cluster computing in yet another way. While current petascale systems have on order of  $O(10^4)$  individual CPU chips, future exascale systems are estimated [24] to have two orders of magnitude more chips. Current cluster computers have to refer to off-the-shelf components to keep costs low: mass-produced CPUs are used because they are cheap, not because they are perfect.

In contrast, in future supercomputers the number of CPU chips will be so big that it would justify their custom development. In view of the approach to system development outlined above – from chips to servers to entire supercomputers – this future mass-production not only poses challenges but also opens new prospects. It can signify the convergence between custom supercomputers and the ones based on off-the-shelf components.

# 1.4. Generality of Approach

The framework that we develop can be applied to more general problems, like the design of "warehouse-scale" computing facilities – the big data centres, as the ones used for cloud computing. Indeed, the distinctive feature of computer clusters is that they are built from a small variety of types of compute nodes, usually just one or two types, and the notion of performance of a supercomputer is clearly defined.

In contrast, big data centres can utilise a diversity of equipment types, and the concept of "performance" of a data centre is defined differently. Aside from that, problems remain the same and are solved in the same way: assessing technical and economic characteristics of a given hardware configuration, designing interconnection networks, placing equipment into racks and positioning racks on the floor, routing cables and so on.

# 2. Related Work

If I have seen further it is by standing on the shoulders of giants.

Isaac Newton

The process of designing a cluster supercomputer basically consists of several steps: (1) exploring design space to find favourable configurations, (2) estimating performance of each configuration, (3) adding infrastructure components, such as network, power, cooling, etc., (4) assessing economic and technical characteristics of resulting designs.

The configuration step is of particular importance: using domain-specific knowledge, it combines components in a compatible fashion, and simultaneously filters out poor designs. This significantly reduces the number of designs that have to participate in subsequent procedures.

In this chapter we review a number of works: papers [60, 62, 43] address just the configuration problem in the field of computer design, while papers [22, 112] try to solve the whole problem of choosing an optimal computer cluster. (Literature on other tasks is reviewed in relevant chapters, e.g., literature on networks is discussed in Chapters 13 and 14).

Additionally, article [57] contains an extensive review of different combinatorial mathematics formulations of system configuration task. It shows that a problem of finding a set of distinct representatives, shortest path problem, knapsack problem, assignment problem and morphological analysis – both in one-criterion and multi-criterion formulations – can be successfully used to describe real-world configuration tasks.

# 2.1. McDermott, 1980

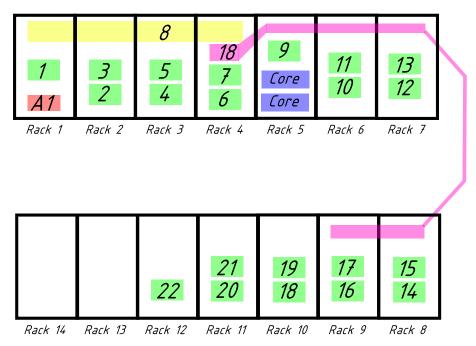

*R1* is an expert system created by John P. McDermott in late 1970s [60]. Its main task was to configure VAX-11/780 minicomputers made by Digital Equipment Corporation. As VAX computers supported a large assortment of peripheral devices, the total number of possible configurations was very big.

A bus called Unibus was used to connect low-speed peripheral modules to a minicomputer. There were lots of mechanical and power constraints that directed placement of Unibus modules into backplanes, backplanes into boxes, and boxes into cabinets.

Unibus modules should be put into backplanes in a specific precomputed optimal sequence. If, after placing a module, the remaining space in the backplane is not sufficient to accommodate the next module in the sequence, the designer has to consider two choices: (1) either add a next backplane, possibly increasing the volume taken by hardware, and eventually the occupied floorspace, or (2) deviate from the optimal sequence of modules.

#### 2. Related Work

Similar rules and constraints apply to configuring another bus, the Massbus, used to connect disk and tape drives.

Working with human designers, McDermott was able to initially extract 480 rules that represented domain knowledge. Then, *R1*, an expert system, was implemented as a production rule system.

*R1* was designed to check customers' orders for validity and complement them if necessary. Given a partially defined order, the system would extend the configuration using the design rules. For example, if one backplane was not enough to accommodate all peripherals specified in the order, the system would add as many backplanes as required.

The system didn't try to iterate through different models of components, assessing cost and performance of resulting designs, simply because it was created to solve a different problem. Therefore, the *R1*'s approach could not be directly applied to design cluster supercomputers. However, integrating an expert system into a CAD tool for cluster supercomputers appears beneficial, and this approach is detailed in chapter 18.

In a certain sense, *R1* set the standards for future automated configurers of computers. Indeed, the system was able to determine spatial location of components in cabinets, position of cabinets on the floor, length of cables (and produced a wiring table), and also reported unused capacity – i.e., what other components could potentially be added to expand a computer in the future.

Additionally, *R1*, as a CAD system, was able to produce more detailed documentation for technicians performing the physical assembly than human designers could do. This feature, implemented in a future CAD system for supercomputers, would be especially useful for larger installations.

#### 2.2. Mittal and Frayman, 1989

In 1989, Sanjay Mittal and Felix Frayman revisited a general configuration task [62]. They pointed at the deficiency of then-current aproaches: namely, the reliance on naïve definition of configuration as a design activity, which didn't allow for comparison between approaches. As a uniformly accepted formal definition seemed to be lacking, Mittal and Frayman introduced it.

According to their general definition, there exists a set of components, and each component has a set of ports to connect to other components. The general version of the configuration task – any component can be connected to any other compatible one – has an exponential complexity.

They further introduce two restriction. The first relates to *"functional architecture"*: instead of trying all possible arbitrary combinations of compatible components, real-world configuration tasks usually connect components according to a certain set of rules which together define an *architecture*, intended to fulfil a specific *function*. All other combinations, although valid, should not be considered, which reduces search.

The second restriction concerns "key components": if a certain functionality must be available, there is usually a key component that is crucial in providing that functionality, and which also entails a set of auxiliary components.

**Example 2.1** Cluster supercomputers are commonly built using commercially available servers. Each server has a video display interface which can be used for local debugging. However, the

architecture of cluster supercomputers does not assume that displays would be connected to every cluster node in the resulting machine: it is a computing farm, not a visualisation wall. Hence, although the connection is formally valid, it contradicts the architecture and shall not be considered during the automated configuration.

Similarly, to implement a function "interconnection network", several key components are required: network adapters in cluster nodes, network switches and network cables. Network switches additionally entail an auxiliary sub-component: power cables.

Together, these two restrictions, based on domain-specific knowledge, not only reduce search space, but also help to partition the global configuration task into a number of relatively independent subtasks.

Although the above considerations of knowledge representation may seem obvious for any particular domain, the merit of the cited work is in formalising the ideas for the most general abstract case. We will often refer to the concepts outlined above throughout this thesis.

The authors also proposed an algorithm to search for configurations. They advised to check compatibility constraints as early as possible during the design process to reduce the need to backtrack.

# 2.3. Hsiung et al., 1998

*ICOS* – an Intelligent Concurrent Object-Oriented Synthesis methodology – was proposed in 1998 by Pao-Ann Hsiung *et al.* [43] and focuses on design of multiprocessor systems. In this object-oriented methodology, system components are modelled as classes with hierarchical relationships between them.

Previously synthesised subsystems are reused as building blocks of new designs. To achieve this, *ICOS* applies machine learning techniques. It compares specifications of previously learnt designs with current specifications, using fuzzy logic, and in case of a match, a previous design is reused.

Several design alternatives can be evaluated concurrently (in parallel), with the aim of further reducing time to solution. Performance, cost, scalability, reliability and faulttolerance constraints can all be specified. Logic rules are used to detect incorrect or contradictory input specifications.

Unsuccessfully synthesised components (violating constraints) cause the rollback procedure by propagating messages in the class hierarchy and subsequent re-synthesis. Of several system designs that match constraints, the one with the best performance is selected.

Overall, *ICOS* provides a way to represent design data and candidate solutions in the memory of a CAD tool, in the form of a class hierarchy. It is theoretically capable of designing cluster supercomputers, which can be specified therein as "MIMD hybrid architectures", i.e., a number of multiprocessor compute nodes, each with a shared memory, connected together by an interconnection network.

However, *ICOS*, being a rather general tool, cannot evaluate performance on different workloads, doesn't take infrastructural component of cluster supercomputers (power, cooling, etc.) into account and is unable to calculate the total cost of ownership (TCO). The approach that we propose in this thesis overcomes these deficiencies, while utilising certain ideas from *ICOS* – namely, representing components as objects and ability to specify an array of practically meaningful constraints.

# 2.4. Dieter and Dietz, 2005

At Supercomputing 2002 conference, William R. Dieter and Henry G. Dietz presented the tutorial on *Cluster Design Rules (CDR)*, the methodology to design computer clusters suited for specific workloads. By 2005, their web-based CAD tool, *CDR*, was used many times, and certain patterns started to emerge in the tool's output. The findings were summarised in 2005 in the technical report [22].

*CDR* is perhaps the first documented attempt to create a CAD tool for clusters, specific enough to take care of necessary details, such as infrastructural equipment and component prices, and at the same time general enough to allow for a wide variety of components.

Dieter and Dietz found an important regularity: for the criterion functions they were using, there were no simple ways to derive a globally-optimal model of a component from its parameters. For example, the fastest (and hence the most expensive) CPU as well as the cheapest (and hence the slowest one) did not necessarily deliver optimality to the resultant design. Similarly, the CPU with the lowest price to performance ratio did not yield optimality, too.

It means that global optimality of the entire system cannot be ensured via using locally optimal components. In this example, the correct choice of a CPU can only be made through exhaustive search, trying every candidate CPU and evaluating the global criterion function. Additionally, when market prices change, the design procedure has to start anew, because now it could be a different model that would bring global optimality.

During the execution, the tool presents a designer with a series of questions that mainly describe workload characteristics. Of particular importance are (1) main memory bandwidth within a compute node, measured in GBytes/second per a GFLOPS, that an application needs, and (2) network parameters – namely, latencies of ordinary and collective operations, bisection bandwidth per a processor core, and the number of neighbouring compute nodes that an application will typically communicate with.

Unfortunately, there are problems with these parameters. First, they are difficult to quantify (although a link is given to the paper that suggests to determine them using hardware counters). Second, application's needs may change during different phases of its execution. It is unclear whether we should engineer the cluster for the worst case, or for the average case, or otherwise. Third, in current cases of shared usage of big supercomputers, applications come and go, and requirements of the same application change with code updates, introduction of new mathematical models, or with different input data. In this case, precise tracking of the above parameters becomes useless.

It makes sense to determine workload requirements when workload is rather stable, such as day-to-day weather predictions in national weather forecasting facilities. In other cases, instead of the fairly low-level parameters, performance modelling appears a viable alternative. *CDR* allows to specify the minimum required performance of the supercomputer on High Performance Linpack and SWEEP3D benchmarks (the latter is a particle transport simulation).

Additionally, physical constraints (rack space and available cooling) and budgetary constraints (acquisition cost, operating costs: electricity and floor space rent) can be specified.

The criterion function is a weighted linear combination of metrics, sought to be maximised. (Another criterion function, aimed to optimise for the minimal total cost of ownership (TCO), is marked as "experimental" and does not work). Weights can be specified as zero (to disregard values of certain metrics) or as  $10^n$ , where  $0 \le n \le 6$ . Metrics are either ordinary (memory space size, memory bandwidth, disk space size, network bandwidth and raw performance) or inverse (the lower the value, the better: network latency, acquisition cost, operating cost per year).

The difficulty with the weightings is their voluntaristic assignment by the user. There is no "ideal" assignment, so different assignments result in different "optimal" designs. This depreciates the whole idea of optimisation.

*CDR* builds network structures for the supercomputers it designs, using the auxiliary *NetWires* tool [23]. *NetWires* is capable of designing and visualising network topologies; however, it is unable to calculate network cost, or design networks according to constraints (such as expandability).

The results in [22] indicated the complex nature of design space when pricing is taken into account. For example, when setting varying constraints for network performance and cost, *CDR* suggested radically different network solutions, in terms of hardware and topologies. Similarly, for smaller clusters, uniprocessor compute nodes were found to have a higher performance within the same budget than the multiprocessor ones – a non-intuitive conclusion. These examples once again underline that a thorough automated search is required.

Overall, *CDR* was a successful project that pointed to new directions for research in its field.

#### 2.5. Venkateswaran et al., 2009

The problem of automated design of cluster supercomputers was attacked again in 2009 by Nagarajan Venkateswaran et al. [112]. Their methodology, "Modeling and integrated design automation of supercomputers (MIDAS)", tried to analyse and model cluster supercomputers via the use of simulation. Although the methodology is aimed at Supercomputers-on-a-Chip (SCOC), it can be generalised to wider areas as well.

*MIDAS* builds a dependency graph of many parameters that determine performance and power consumption of a cluster supercomputer. Then the relationships are expressed as analytical mathematical models, in form of equations. Separate components of a computer are optimised using a simulated annealing procedure, to parametrise each model. Then, high-level characteristics, such as performance, power, performance per watt are inferred from separate models.

As *MIDAS* is intended for Supercomputers-on-a-Chip, it's authors suggested to build the chips – the basis of cluster nodes – using a library of IP cores. The functionality of cores ranges from numerical to linear algebra to graph algorithms. Placing cores on a chip in necessary quantities delivers specific functionality and performance of a cluster node. Designing these custom chips (ASICs) is done using familiar EDA tools.

#### 2. Related Work

*MIDAS* does not address problems of building interconnection networks to connect cluster nodes, nor it concerns infrastructural components or equipment placement problems. However, it serves as an important link for implementing the Electronic System Level design workflow detailed in "Introduction": from chips to servers to supercomputers.

# 3. Problem Statement

Dr. Hoenikker used to say that any scientist who couldn't explain to an eightyear-old what he was doing was a charlatan.

> *Kurt Vonnegut* CAT'S CRADLE, CHAPTER 15

This chapter presents a concise formulation of the problem that we are trying to solve, and introduces the reader to the possible mathematical formalisms that could be employed for the task.

# 3.1. Problem Statement

We formulate the problem as follows: build a cluster supercomputer from identical compute nodes, connected together via a network, equipped with uninterruptible power supply system (and possibly other infrastructural systems), subject to constraints imposed on minimum performance and maximum acquisition cost, total cost of ownership (TCO), space, power consumption (and possibly other characteristics), and yielding minimality to the criterion function: f = TCO/Performance. The criterion function is therefore the simplest multiplicative function, but its non-linearity induces certain consequences. This choice is justified in Chapter 6.

We call for the use of total cost of ownership instead of using just capital expenditures (the procurement costs), because operating expenditures can comprise a substantial share of the TCO. For example, water-cooled equipment, seemingly expensive in terms of up-front costs, may have lower operating expenditures, whilst allowing easy recuperation of waste heat which leads to further savings.

The problem is a discrete optimisation problem. To perform a thorough search, we need to: (1) try every possible compute node configuration, (2) choose the number of compute nodes that meets constraints; if there are multiple variants, try all of them, (3) connect compute nodes with all possible networks, (4) design infrastructural systems, etc. Of course, this formulation makes the task intractable. We need to introduce substantial simplifications, and we start with a definition of a *configuration*.

# 3.2. Defining a Configuration

Following Mittal and Frayman [62], if we have a set of components, and every component has ports to connect it to other compatible components, then a configuration is defined by exact instances of components and structure of their connections with each other.

This "material" definition is easily transferred into the field of cluster supercomputers. Indeed, a compute node has a number of distinct ports, designed specifically to connect it to other components of a supercomputer. Certain network ports can be used to connect to a high-speed interconnection network, while others can serve to build a storage network. Power ports connect compute nodes to relevant power equipment, such as uninterruptible power supplies (UPS).

Some "ports" are less material but still stipulate compatibility between components. For example, mechanical compatibility between rack-mounted servers and racks is ensured by following industry standards. On the contrary, blade servers are normally compatible only with enclosures made by the same vendor. In a CAD tool, two models of blade servers made by different vendors will have to be represented as having incompatible "ports".

But a configuration is not described merely with material items. Let us consider an example. Multiprocessor compute nodes often have a system setting called "*Memory interleave*", which alters the assignment of memory blocks to CPUs. By turning this setting on or off, hardware structure can be tuned to a particular memory access pattern of applications. For any given algorithm, both values of this setting can result in either performance increase or degradation. Choosing inappropriate value can result in a performance loss of this particular node. In parallel computing, where overall performance is often determined by the slowest node, this can lead to slowing down the entire cluster computer. For such a non-material configuration item, there are no "ports" to connect it to other components, still we need a way to represent this item in a CAD system. The key question is therefore knowledge representation.

# 3.3. Representing Configurations with Multipartite Graphs

For a start, we must be able to construct valid configurations of compute nodes. In layman terms, building a compute node from components boils down to filling provided "sockets" and "slots" with these components, according to certain rules.

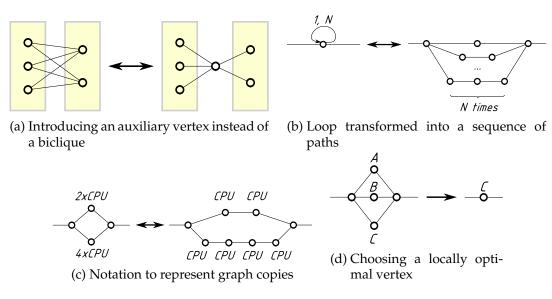

We follow the approach of Bozhko and Tolparov [14] for representing configurations of arbitrary technical systems using multipartite graphs. However, instead of undirected graphs with cycles we propose to use directed acyclic graphs, and rationalise our choice in Chapter 10.

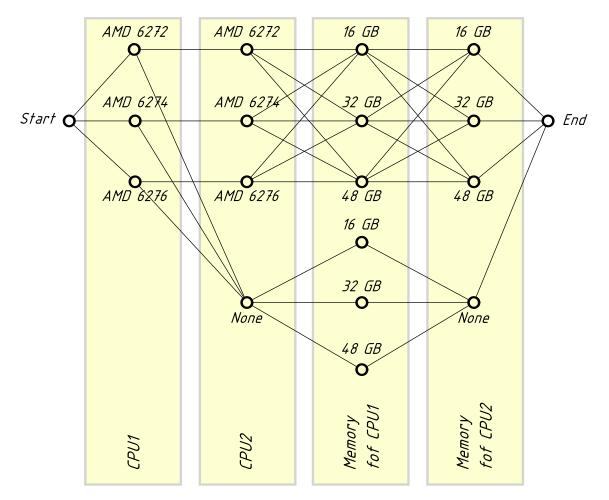

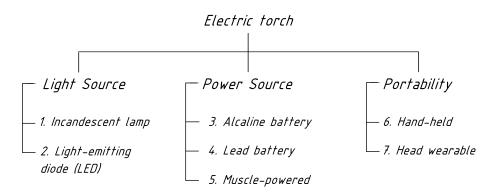

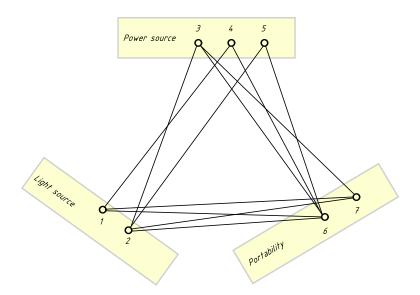

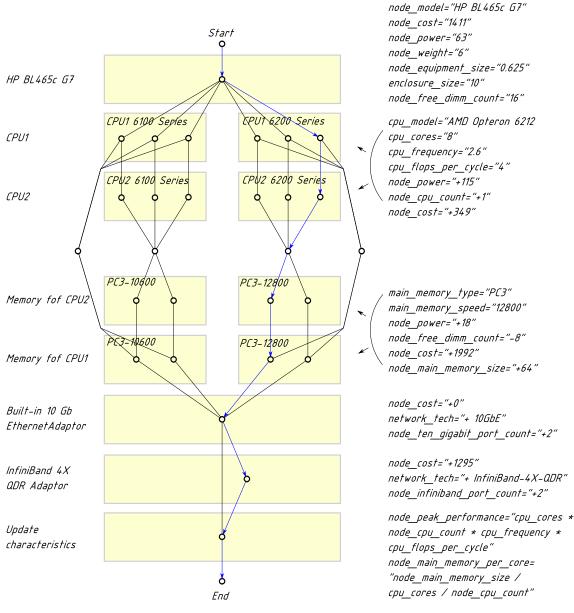

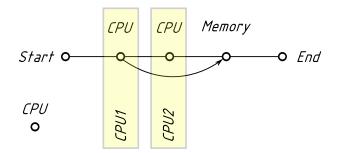

A relatively simple example of representing a compute node configuration with a multipartite graph is shown in Figure 3.1 (the graph is directed, but arrows are not shown to reduce clutter). Each partition of the graph contains components of the same type. Edges between components in different partitions represent compatibility of those components (components are considered compatible if there are no restrictions on their simultaneous use in the technical system). Every path in the graph represents a valid configuration.

This fictional compute node can have either one or two CPUs. Three CPU models are available, but if two CPUs are used, the models must be identical. Additionally, each CPU has a set of memory slots associated with it (a NUMA architecture). Note that we do not represent memory slots in this particular graph, as this would further complicate matters. Instead, we specify three available sizes of memory that can be attached to a single CPU.

There are two rules according to which this compute node must be configured: (1) at least one CPU must be installed, (2) memory slots belonging to a certain CPU socket can

3.3. Representing Configurations with Multipartite Graphs

Figure 3.1.: Representing configuration of a fictional compute node with a multipartite graph.

only be filled if the corresponding CPU is installed.

Traversal of this graph models possible scenarios of configuring a compute node from components. The process begins with filling the first CPU socket with one of three possible CPU models. Then, if no second CPU is used, we only need to choose one of three possible memory sizes for CPU1. Hence, a uniprocessor configuration has 9 realisations. If we decide, however, to install a second CPU, then we can choose one of three possible memory sizes for CPU1 and one of three sizes for CPU2. Therefore, in a dual-processor node, for any given CPU model, there are nine possible memory configurations, and combined with three CPU models, this gives 27 realisations. Together, this fictional node can be configured in 9 + 27 = 36 distinct ways.

Even though only some of these 36 configurations are close to optimal, we need to represent all of them in a graph, to avoid invalid configurations. Trying to "simplify" this graph may generate invalid solutions, such as having both CPU sockets empty, or having memory attached to both CPU sockets while only one is filled.

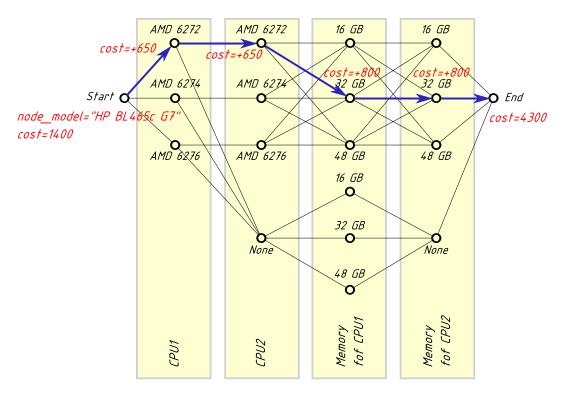

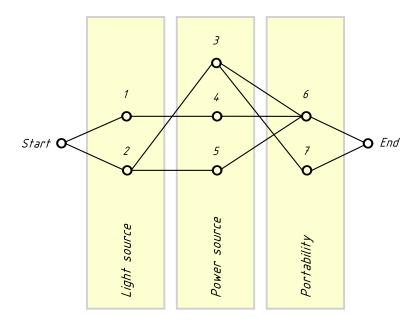

Figure 3.2 describes traversal of the graph. Vertices - components of the compute node -

#### 3. Problem Statement

Figure 3.2.: Traversing the graph to calculate characteristics of a configuration.

are assigned with a set of characteristics, literal or numeric, such as "cost=650". Traversing the graph involves finding all possible paths from "Start" to "End". One such path is highlighted with arrows. Traversing vertices along the path allows to accumulate characteristics assigned to vertices or to perform evaluation of expressions. For example, expression "cost=+800" signifies adding "800" to the current value of variable "cost". (See complete syntax in Chapter 10). Thereby, after traversing the path, the value of cost is determined and stored for future use.

Real-life equipment can be configured in much more ways. For example, Hewlett-Packards's "SL390s G7" server (the 4U height version) has two CPU sockets, and 13 CPU models are supported. Twelve memory slots are available, providing for numerous memory configurations, with both ordinary and low-power modules. Internal x16 PCIe 2.0 slots allow installation of up to three GPU accelerators. Up to eight hard drives can be installed, combined into RAID arrays of three possible levels – 0, 1 and 5. A server can also have an optional InfiniBand adapter, and last but not least, it is shipped in either left or right variant, depending on its final position in the enclosure. As can be seen, the possibilities for configuration are endless, as is the combinatorial difficulty of the task.

# 3.4. Algorithm for Designing Computer Clusters

The algorithm is described in full in Chapter 11. The required input to the algorithm is the minimal performance that the cluster computer must be able to achieve. Optional inputs include design constraints (see Chapter 8). The output of the algorithm is the *configuration*

of the cluster computer, with all technical and economic characteristics necessary to (a) conduct procurement, and (b) perform further design procedures as necessary. For each configuration of a compute node obtained via traversing the graph, the following stages of the algorithm are performed:

- 1. Using inverse performance modelling (see Chapter 9), calculate the number of compute nodes that is required to attain the specified performance.

- 2. Design an interconnection network (see Chapters 13 and 14).

- 3. Design infrastructural systems, such as uninterruptible power supply system (see Chapter 15).

- 4. Place equipment into racks and place racks on the floor plan (see Chapter 16).

- 5. Compute the criterion function for the configuration (see Chapter 6).

On every stage of this algorithm various technical and economic characteristics of the configuration are evaluated, such as its cost, power consumption, amount of equipment, etc. Simultaneously, on every stage configurations are checked against specified constraints, which allows to detect and discard violating configurations as early as possible.

The characteristic feature of our approach is that we propose to perform separate stages of the design process by querying, via network, appropriate modules – performance modelling module, network design module, and so on. This modular approach ensures extensibility of the CAD tool. It also allows to utilise the most current versions of design algorithms by plugging in corresponding modules.

# 3.5. Combinatorial Explosion

Separate stages of the design process are subjected to local optimisation performed by the corresponding modules. This allows to put a limit on combinatorial explosion. For example, suppose that for each configuration a network can be designed in 5 ways, and a UPS system in 3 ways. Therefore, for each configuration it will be required to run the network design stage 5 times (5 units of work), and then for each of these semi-complete designs the UPS design stage must be run 3 times (15 units of work), resulting in 20 instances of design modules invocation.

In our approach, we run the network design stage 5 times and choose a locally optimal solution. Then, we run a UPS design stage for 3 times, and again choose a locally optimal solution. This approach may miss some globally optimal designs; however, it allows to keep design times reasonably low.

There are other occasions where combinatorial explosion may manifest itself. For example, turning the "Memory interleave" option in the BIOS of a compute node on or off results, in fact, in two separate configurations, with drastically different performance characteristics (see section 9.1.1 for this and other examples). The "Memory interleave" setting *can* be represented with a configuration graph (by adding a new partition to the graph with two vertices); however, it only makes sense to do so if there exist performance models that can adequately predict performance based on this BIOS setting. Yet another case is choosing a software environment for the computer cluster. If there are several software packages to solve a problem, and each is characterised by its own performance curve and total cost of ownership (licensing costs as well as maintenance and support costs), then thorough search among all software alternatives is required. In the current implementation of our CAD tool, we ask the user to manually specify what software (and its performance model) should be used to drive design decisions.

# 3.6. Interdependencies

Real life computing equipment can present unexpected interdependencies of components. We review several examples of such situations where the configuration graph can adequately represent valid configurations.

- 1. Modern commodity CPUs have a built-in memory controller which only supports a specific amount of RAM. Therefore, a uniprocessor configuration can only be equipped with a limited amount of memory. If more memory is needed, it is necessary to install a second CPU, and use its designated memory slots. Here the requirement of adding more memory unexpectedly entails the need to install more CPUs. (See, for example, Fig. 3.2, where installing 64 GBytes or more memory inevitably requires installation of both CPUs).

- 2. Highest-capacity memory modules (such as 32 GByte DDR3 SDRAM modules) often work at lower speeds than modules of lower capacity (16 or 8 GBytes). In highperformance computing, the performance of memory subsystem is of utmost importance. To reflect the issue, the configuration graph can be reworked to specify exact types of memory modules and their performance characteristics.

Traversing the graph will generate all possible configurations. Then, constraints can be imposed on the minimal total amount of memory and on the minimal memory speed. This will weed out unsuitable configurations with slow memory. (It is also desirable to pass the memory performance characteristics on to the performance modelling module for more accurate performance predictions).

- 3. Some servers have a large number of memory slots, but when using high-capacity memory modules, only part of the slots can be utilised, because the memory controller built into a lower-end CPU can only address a limited amount of memory. However, when using a higher-end CPU, all slots can be occupied.

- 4. Some servers can accommodate a wide variety of CPUs, ranging from low-end, lowpower models to hi-end models with high power consumption. It is possible that due to thermal constraints either two low-power CPUs can be installed in a server, or only one high-power CPU. The configuration graph can take care of this situation.

In all of these cases, using graphs allows to adequately represent real life interdependencies of components. There are, of course, more than these few examples of interdependencies. Some of those listed above can be obsoleted with introduction of new hardware, while at the same time new interdependencies will emerge.

## 3.7. Proposed Design Framework as a Means of Collaboration

Procurement of an HPC system involves at least three parties: hardware vendors, application software vendors, and byers; the latter are research institutions and companies. (In certain settings, although not in general, buyers can write their own software to be run on a supercomputer, and therefore also play the role of application software vendors).

These three parties have little in common. Hardware vendors have knowledge of their hardware and peculiarities of its usage. Application software vendors know the properties of their software, and can predict how well it will run on the system being designed and built, and how the software performance will be affected by changing computer parameters.

For example, they can predict what impact a twice faster network could have on the overall performance of their software. At the same time, they might not know complex compatibility relations between hardware components. During the procurement process, both groups – hardware and software vendors – work together to determine an "optimal" configuration of a supercomputer for the task, and benchmarking is the main method employed.

Buyers, constrained by tight deadlines, necessarily face uncertainties. When large supercomputers are procured, it is generally impossible to run a full-scale benchmark, because hardware vendors are unwilling to commit resources and time to building large prototype machines. Similarly, if a decision to install a twice faster network is considered, buyers need cooperation from both hardware and software vendors to make a conclusion.

A faster network will increase procurement and possibly operating costs. It is difficult to quantify the increase unless the hardware vendor is willing to prepare several network designs for the client, or if buyers possess tools to automatically design networks and assess their technical and economic characteristics. On the other hand, a faster network may increase performance of the supercomputer, perhaps surpassing associated cost increase. Again, it is difficult to quantify performance increase unless software vendor cooperates, or if there are tools to predict performance depending on computer parameters.

The proposed framework gives in the hands of buyers, the most numerous group of players in the HPC market, a convenient set of tools which lessens their dependence on hardware and software vendors. Software vendors can turn informal knowledge of their software into performance models. Such models can be built and verified (similarly to how we built a performance model for ANSYS Fluent software suite in section 9.4), and then tweaked to be precise enough to make useful performance predictions.

Hardware vendors then can provide a configuration graph for their hardware, which will generate valid configurations, together with cost, power and other characteristics. Network, UPS and other vendors can provide modules that can design networks (see Chapters 13 and 14), UPS systems (see Chapter 15), etc. The CAD tool will bring all components together, allowing buyers to quickly search their chosen part of the design space, without unnecessary reliance on vendors, and arrive to provably good designs.

## 4. Outline of the Thesis

## Part I: Introduction and Problem Statement

#### **CHAPTER 1: INTRODUCTION**

We start the thesis by explaining motivation behind the work, highlighting benefits of automated design space exploration, and clarifying how design of computer clusters complements the field of electronic design automation (EDA).

#### CHAPTER 2: RELATED WORK

We review related work in the filed of configuration of computer systems: from the general formulation of the task, dating back to 1970s, to multiprocessor systems (1998), to automated design of high-performance computers (2005 and 2009).

#### CHAPTER 3: PROBLEM STATEMENT

This chapter formulates the design task in terms of a discrete optimisation problem, explains the use of multipartite graphs to represent configurations, outlines the algorithm for automated design of cluster supercomputers, and proposes strategies to deal with combinatorial explosion.

We also provide the overview of complex interdependencies between components that can arise in real life configurations of supercomputers, and the role of configuration graphs in representing compatibility between components.

Finally, we explain how the automated design framework presented in the thesis, together with its software tools, lessens the dependence of supercomputer buyers on hardware and software vendors.

#### **CHAPTER 5: SCIENTIFIC CONTRIBUTION**

Here, we list scientific contributions of the thesis, i.e., what the reader can learn from the thesis compared to the state of the art.

### Part II: Criterion Function and Design Constraints

#### **CHAPTER 6: CHOICE OF THE CRITERION FUNCTION**

In this chapter, we propose the criterion function to be used throughout the thesis: the ratio of total cost of ownership to performance. We explain why using one-criterion instead of muti-criterion optimisation is possible and provides good results. Additionally, a generalisation of the criterion function based on interval arithmetic is introduced.

#### CHAPTER 7: ECONOMICS OF CLUSTER COMPUTING

We explain the benefits of total cost of ownership compared to procurement cost as a metric guiding design decisions. We also compare capital and operating expenditures. Finally, questions of balance between high-speed, high-cost components and low-power, low operating cost components are addressed.

#### CHAPTER 8: DEALING WITH COMBINATORIAL EXPLOSION

Here, we detail strategies to deal with combinatorial explosion. The first approach is to impose constraints on characteristics of compute nodes or the whole machine, and the second one is to use heuristics that allow to quickly weed out unpromising solutions.

#### **CHAPTER 9: PERFORMANCE MODELLING**

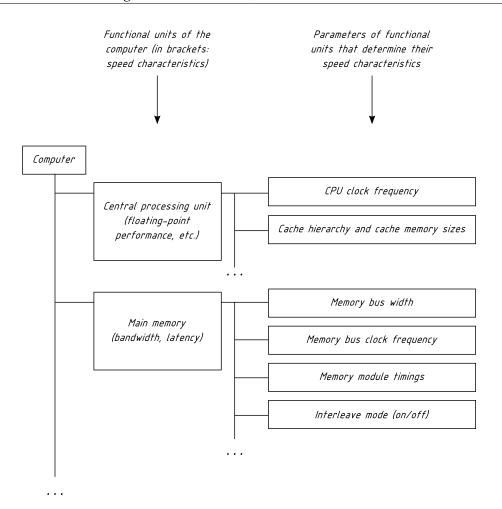

In this chapter, we introduce the notion of performance and speed of computer components, and then review related work concerning factors that influence performance as well as approaches to performance modelling.

We then discuss the "optimal" number of computing blocks (cores, CPUs, compute nodes) to be used for parallel execution, and the corresponding "throughput mode" of operation of large supercomputers.

Further, we introduce inverse performance models and the algorithm to determine the number of compute blocks required to attain a given performance level.

Finally, a simple analytical performance model for "ANSYS Fluent" CAE software suite is proposed, and the process of querying performance models via Internet is explained.

### Part III: Automated Design of Computer Clusters

CHAPTER 10: GRAPH REPRESENTATION OF CONFIGURATIONS

We explain the use of directed acyclic graphs for representing compatibility between components of arbitrary technical systems, comparing benefits and disadvantages of directed and undirected graphs.

We then propose assigning arithmetic expressions to vertices and edges of the configuration graphs, which results in evaluation of technical and economic characteristics of systems during graph traversal. Finally, XML syntax for representing graphs is introduced.

CHAPTER 11: ALGORITHM FOR AUTOMATED DESIGN OF CLUSTER SUPERCOMPUTERS

Here, we describe in detail stages of the main algorithm used in the thesis, as well as discuss the limits of the design framework and their influence on the optimality of solutions in the mathematical sense.

We then make the case for designing computer clusters based on their minimum performance rather than on maximum budget.

#### CHAPTER 12: CAD SYSTEM FOR COMPUTER CLUSTERS

This chapter describes the user interface of the prototype CAD tool for computer clusters. We also discuss currently implemented modules of the CAD system and their invocation sequence, and propose a parallelisation strategy for the CAD tool.

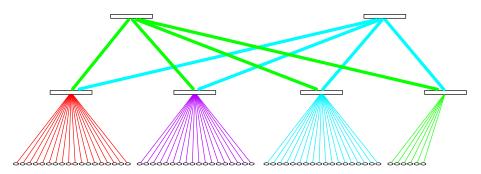

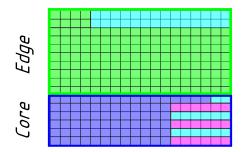

#### CHAPTER 13: FAT-TREE NETWORK DESIGN

We propose an algorithm for designing two-level fat-tree networks with arbitrary blocking factors, automatically choosing the best combination of monolithic or modular switches on both levels, subject to various constraints.

We then discuss how technical and economic characteristics of fat-tree networks can be easily derived from corresponding per-port metrics. Comparison of strategies for future expansion of fat-trees concludes the chapter.

Note: the contents from this chapter were deposited in Arxiv, an open-access pre-print repository [94].

#### CHAPTER 14: TORUS NETWORK DESIGN

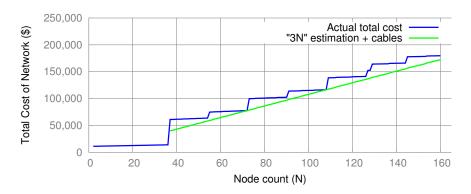

We propose an algorithm for designing torus networks, and a heuristic for automatically choosing the number of torus dimensions. We then compare cost of torus and fat-tree networks.

Note: the contents from this chapter were deposited in Arxiv, an open-access pre-print repository [93].

#### CHAPTER 15: DESIGNING OTHER SUBSYSTEMS OF COMPUTER CLUSTERS

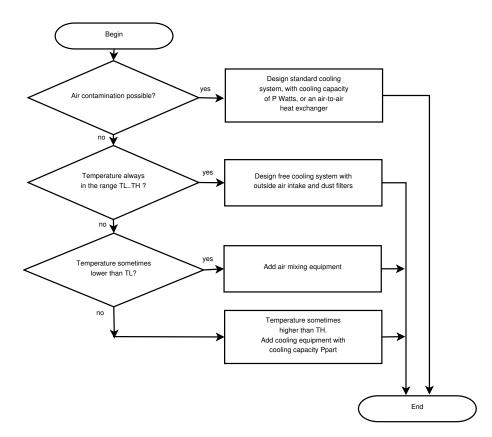

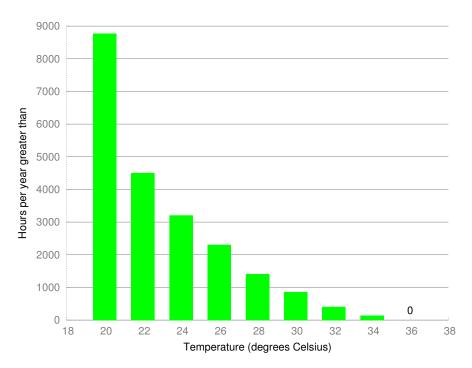

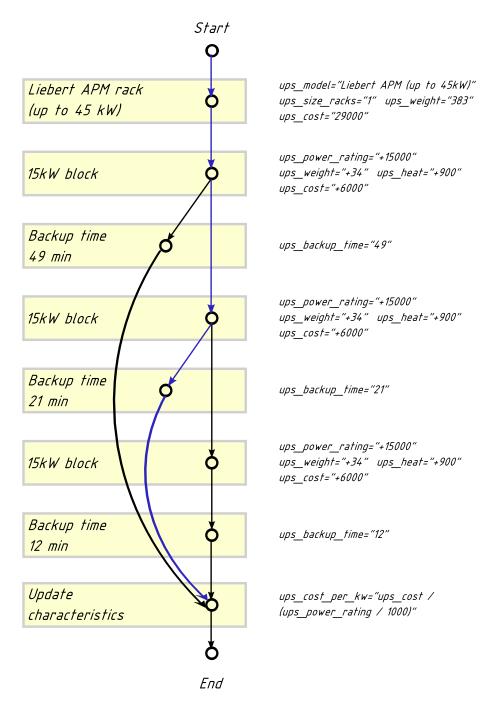

We describe strategies to design storage and cooling systems, investigating the possibility of using outside air for cooling purposes, depending on climate. We then compare costs of cooling solutions, including water-based cooling, and propose to reuse waste heat for agricultural purposes. Finally, we introduce an algorithm for designing UPS systems.

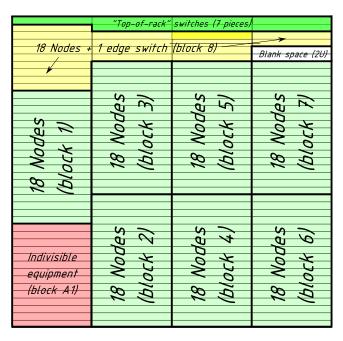

#### CHAPTER 16: EQUIPMENT PLACEMENT AND FLOOR PLANNING

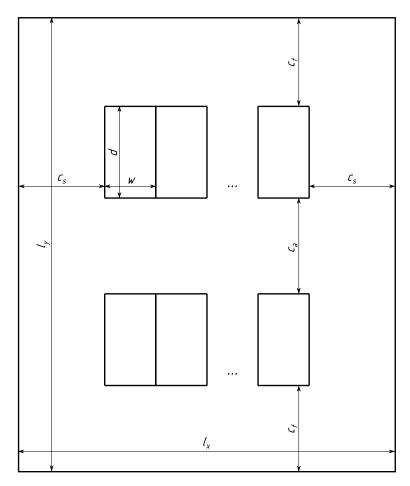

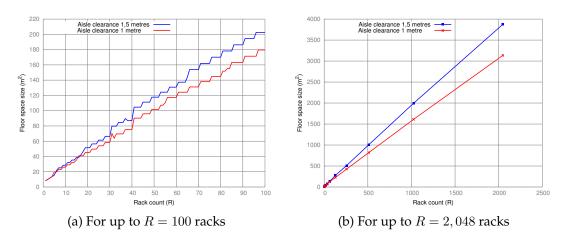

This chapter introduces heuristics for placing equipment into racks, and compares approaches of equipment consolidation and distribution. We then provide a simple analytical model for determining floorspace required to host a computer installation.

#### CHAPTER 17: PRACTICAL EVALUATION OF THE ALGORITHM

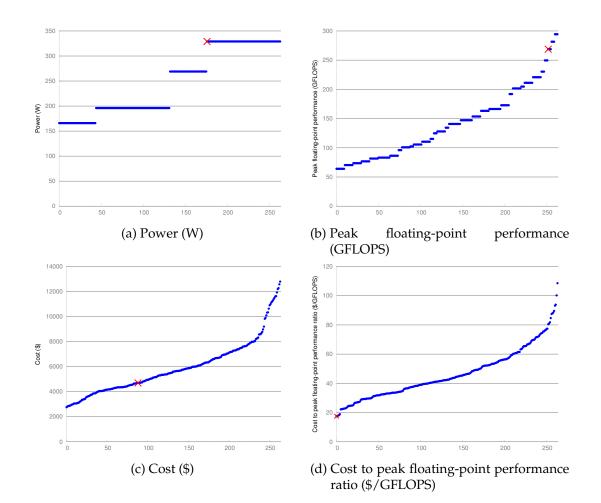

In this chapter, we evaluate the main algorithm of the thesis on a set of real life hardware. We compare technical and economic characteristics of individual configurations of compute nodes as well as clusters built using that configurations, with full infrastructure, such as interconnection networks and UPS systems.

We further provide a detailed analysis of several cluster designs, and quantitatively investigate how changes in technical characteristics of interconnection networks and UPS systems impact economic characteristics of cluster computers.

#### CHAPTER 18: SUMMARY AND FUTURE DIRECTIONS

Here, we summarise the contribution of the thesis, and provide guidelines for future directions of work, such as turning the prototype CAD tool into a decision support system.

## 5. Scientific Contribution

To be of use to the world is the only way to be happy.

Hans Christian Andersen

In this chapter, we list scientific contributions made by the thesis, listed by knowledge areas.

## 5.1. CAD systems

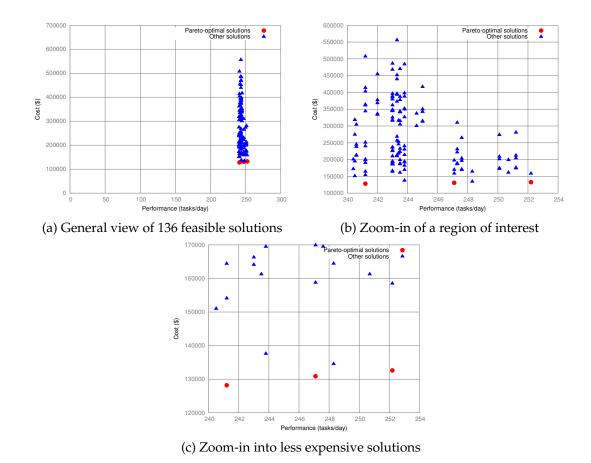

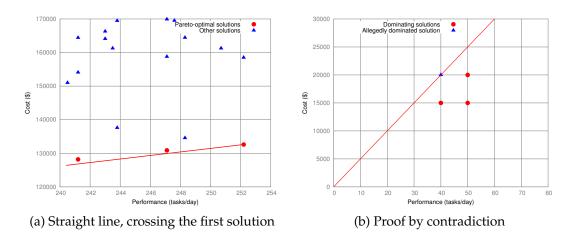

We propose a method for representing compatibility between components of arbitrary technical systems using directed acyclic multipartite graphs for the purpose of structural synthesis. We make the case for a modular CAD system for cluster supercomputers, with modules supplied and maintained by hardware and software vendors, ensuring the use of the most current price data and most recent algorithms to design separate subsystems. We envision the use of interval arithmetic to capture uncertainty in both cost and performance. We provide a proof that the single-objective optimisation used in the thesis always results in a Pareto-optimal solution. We suggest a heuristic that allows to decrease design space by a factor of ten but does not accidentally reject optimal solutions. We also offer arguments against using local optimisations.

## 5.2. Performance modelling

We introduce the notion of inverse performance models and propose a two-phase iterative algorithm for inverse performance modelling.

## 5.3. Computer networks

We propose algorithms to design two-level fat-tree and torus networks, with arbitrary blocking factors. The algorithms operate with real life equipment characteristics such as cost, power consumption, occupied rack space, weight and others, and are able to arrive to cost-efficient network designs by utilising partially populated modular switches.

## 5.4. Data centre design

We propose strategies and heuristics for placing equipment into racks, for the general case of non-identical equipment blocks, taking into account space, weight and power budget

of individual racks. We devise an algorithm for calculating floor space size required for a given number of racks, with a constant run time. We also offer a greedy algorithm for sizing an uninterruptible power supply system.

## 5.5. Cooling systems

We provide a chart for choosing air preparation methods for cooling with outside air and suggest an algorithm for calculating cooling capacity for cooling with outside air. We then perform comparison of capital and operating costs of three types of cooling solutions.

## 5.6. Economics

We provide a comparison of factors that influence cost and performance of cluster supercomputers, together with a quantitative analysis of using low-power ("green") memory modules. We then investigate properties of the total cost of ownership (TCO) as a function of the number of compute nodes. Further, we offer an overview of TCO components for supercomputers. Finally, we propose reusing waste heat from data centres for large-scale greenhouses, outlining an implementation plan.

# Part II.

# Criterion Function and Design Constraints

## 6. Choice of the Criterion Function

There are decision objectives other than maximizing expected return and minimizing maximum loss. That is, in many practical situations there are criteria of optimality that are more appropriate than these two mentioned.

Russell L. Ackoff The development of operations research as a science

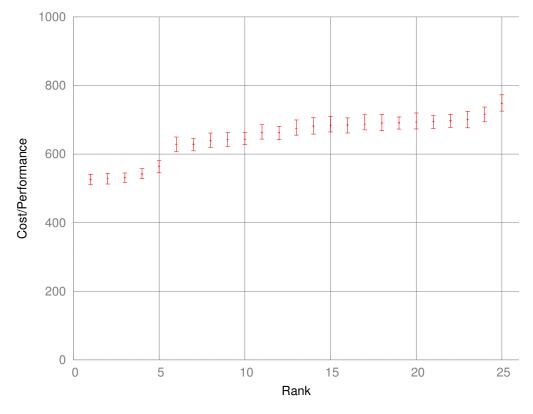

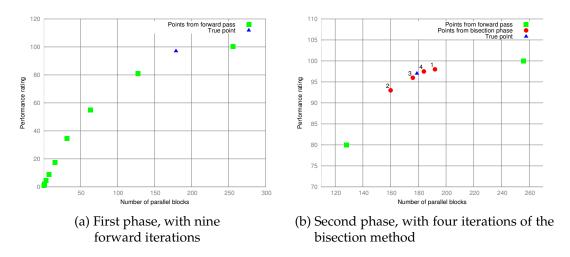

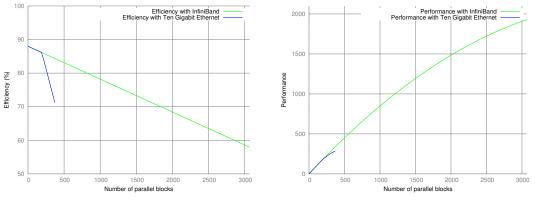

As we are solving a combinatorial optimisation problem with many alternative solutions, we need criteria to guide design decisions. The main approaches here are: (a) define a set of criteria and perform multi-objective optimisation, (b) convolve multiple criteria into a weighted additive or multiplicative criterion function and perform single-objective optimisation, and (c) impose constraints on all but one criteria, and optimise the remaining criterion.