# **TUM**

TECHNISCHE UNIVERSITÄT MÜNCHEN INSTITUT FÜR INFORMATIK

Seminar: Embedded Systems

Maria Spichkova (Editor), Alarico Campetelli (Editor), Klaus Lochmann (Editor)

TUM-I1336

## Abstract

Embedded systems are not only one of the most important fields for current computer-based applications, it is also one of the most challenging fields of software engineering: embedded system must meet real-time requirements, are safety critical and distributed over multiple processors. Embedded systems are used in many areas - from vehicles and mobile phones to washing mashines and printes. Nowadays it is impossible to imagine our life without them. The increasing complexity and real-time requirements require new modelling techniques as well as application of formal methods. In the seminar "Embedded systems" we will try to answer the following questions:

- What does the term "embedded system" mean?

- Which methods are especially important to the development of these systems?

- What are the distinctive features of one of the most interesting kinds of the embedded systems automotive systems?

This report presents the results of our first seminar on "Embedded Systems" held in the winter term of 2012/13. The deliverables to be developed by the students were a learning module prepared by each student as final presentation and the documentation of the learning module in an essay (content of this report). The topics were:

- Topic 1: What does "Embedded System" mean? Student: Fan Zhuosi (Advisor: Klaus Lochmann)

- Topic 2: Cyber-Physical systems Student: Johannes Muhr (Advisor: Alarico Campetelli)

- Topic 3: Real-time systems Student: Christian Lichtmannegger (Advisor: Klaus Lochmann)

- Topic 4: Tasks in Embedded Systems Student: Manuel Bonk (Advisor: Maria Spichkova)

- Topic 5: CAN Protocol Student: Nicolas Beneš (Advisor: Alarico Campetelli)

- Topic 6: FlexRay Protocol: general idea, synchronization Student: Robert Lang (Advisor: Maria Spichkova)

- Topic 7: OSEKtime OS: Scheduling Student: Kostadin Kotev (Advisor: Maria Spichkova)

- Topic 8: Testing vs. Verification and Model Checking vs. Theorem Proving

Student: Philipp Pickel (Advisor: Alarico Campetelli)

## Contents

| 1 | Far | Zhuosi: Introduction to the ES               | 1  |

|---|-----|----------------------------------------------|----|

|   | 1.1 | Introduction                                 | 1  |

|   | 1.2 | The foundation of ES                         | 1  |

|   |     | 1.2.1 Embedded system vs PC                  | 2  |

|   |     | 1.2.2 Characteristics                        | 3  |

|   |     | 1.2.3 The history of ES                      | 4  |

|   | 1.3 | The composition of ES                        | 5  |

|   |     | 1.3.1 Embedded hardware                      | 5  |

|   |     | 1.3.2 Embedded software:                     | 6  |

|   | 1.4 | Application fields                           | 7  |

|   | 1.5 | Problems                                     | 8  |

|   | 1.6 | Conclusion                                   | 9  |

| า | Lah | annea Muhn, Cuhan physical Systems           | 11 |

| 2 |     | annes Muhr: Cyber-physical Systems           | 11 |

|   | 2.1 | Introduction                                 | 11 |

|   | 2.2 | Cyber-physical Systems                       | 11 |

|   |     | 2.2.1 The development and concept            | 11 |

|   |     | 2.2.2 Classification                         | 14 |

|   | 0.0 | 2.2.3 Vision and Aims                        | 16 |

|   | 2.3 | Challenges                                   | 16 |

|   |     | 2.3.1 Non-functional Challenges              | 17 |

|   |     | 2.3.2 Digital and analog world               | 17 |

|   |     | 2.3.3 Complexity Challenge                   | 17 |

|   |     | 2.3.4 Lack of Timing                         | 18 |

|   | 2.4 | Modelling techniques                         | 18 |

|   |     | 2.4.1 Models of Computation                  | 18 |

|   |     | 2.4.2 Multimodelling                         | 19 |

|   |     | 2.4.3 Hybrid Systems                         | 20 |

|   | 2.5 | Conclusion                                   | 20 |

| 3 | Chi | ristian Lichtmannegger: Real-time systems    | 23 |

|   | 3.1 | v v                                          |    |

|   | 3.2 |                                              | 23 |

|   | J   | 3.2.1 Different types of tasks               | 25 |

|   | 3.3 | Scheduling                                   | 25 |

|   | 0.0 | 3.3.1 Scheduling: The basics                 | 25 |

|   |     | 3.3.2 Static scheduling                      | 26 |

|   |     | 3.3.2.1 Round Robin/Static cyclic scheduling | 26 |

|   |     | , , ,                                        |    |

|   |                           | 3.3.2.2 Cyclic static table driven algorithm            | . 27 |

|---|---------------------------|---------------------------------------------------------|------|

|   |                           | 3.3.2.3 Analysis                                        | 28   |

|   |                           | 3.3.3 Dynamic scheduling                                | . 28 |

|   |                           | 3.3.3.1 Least laxity first (LLF)/Dynamic earliest dead- | -    |

|   |                           | line first                                              | . 29 |

|   |                           | 3.3.3.2 The problem with overloads                      | . 29 |

|   |                           | 3.3.3. Fault tolerance                                  | . 30 |

|   |                           | 3.3.3.4 Resource reclaiming                             | . 30 |

|   |                           | 3.3.3.5 Discussion                                      | . 30 |

|   | 3.4                       | RT operating systems                                    | . 31 |

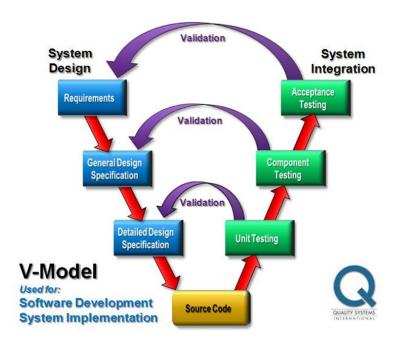

|   | 3.5                       | Developing of RT systems                                | . 32 |

|   | 3.6                       | Conclusion                                              | . 32 |

|   |                           |                                                         |      |

| 4 |                           | nuel Bonk: Tasks in Embedded Systems                    | 33   |

|   | 4.1                       | Introduction                                            |      |

|   | 4.2                       | Definition of Tasks                                     |      |

|   | 4.3                       | Processes                                               |      |

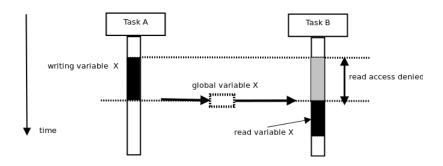

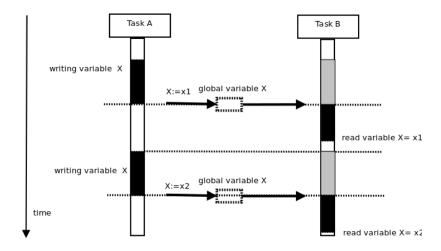

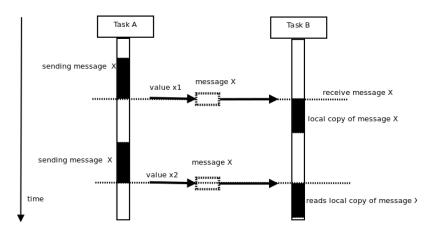

|   | 4.4                       | Interaction between Tasks                               |      |

|   |                           | 4.4.1 Synchronization via Events                        |      |

|   |                           | 4.4.2 Cooperation via Global Variables                  |      |

|   |                           | 4.4.3 Communication via Messages                        |      |

|   | 4.5                       | Tasks in OSEK-OS and OSEKtime OS                        |      |

|   | 4.6                       | Conclusion                                              | . 39 |

| 5 | Nic                       | olas Beneš: CAN Protocol                                | 41   |

| J | 5.1                       |                                                         |      |

|   | $5.1 \\ 5.2$              | Introduction                                            |      |

|   | 5.2                       | Functional Key Concepts                                 |      |

|   |                           | 1 0                                                     |      |

|   |                           | <ul><li>5.2.2 Messaging Principle</li></ul>             |      |

|   |                           | 5.2.4 Fault Confinement Entity and Frame Timing         |      |

|   | F 9                       | v e                                                     |      |

|   | 5.3                       | Protocol Stack                                          |      |

|   |                           | 5.3.1 Logical Link Control                              |      |

|   |                           | 5.3.1.1 Data Frame and Remote Request Frame             |      |

|   |                           | 5.3.2 Medium Access Control                             |      |

|   |                           | 5.3.2.1 Data Frame and Remote Request Frame             |      |

|   |                           | 5.3.2.2 Error Frame                                     |      |

|   |                           | 5.3.2.3 Overload Frame                                  |      |

|   |                           | 5.3.3 Physical Signalling and Physical Medium Access    |      |

|   | 5.4                       | Time Triggered Communication                            |      |

|   | 5.5                       | Alternative Protocols                                   |      |

|   | 5.6                       | Conclusion                                              | . 56 |

| E | $\mathbf{D}_{\wedge}^{1}$ | port I and Flow Day Drotagal, ganaral idea grache       | 30   |

| 6 |                           | pert Lang: FlexRay Protocol: general idea, synchr       |      |

|   |                           | ation                                                   | 57   |

|   | 6.1                       | Introduction                                            | 57   |

|   | 6.2 | FlexR  | ay Specification                                  | 9 |

|---|-----|--------|---------------------------------------------------|---|

|   |     | 6.2.1  | Communication                                     | 9 |

|   |     |        | 6.2.1.1 Architecture                              | 9 |

|   |     |        | 6.2.1.2 Topologies                                | 0 |

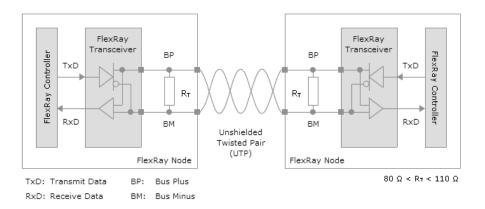

|   |     |        | 6.2.1.3 Node                                      | 1 |

|   |     |        | 6.2.1.4 Bus                                       | 1 |

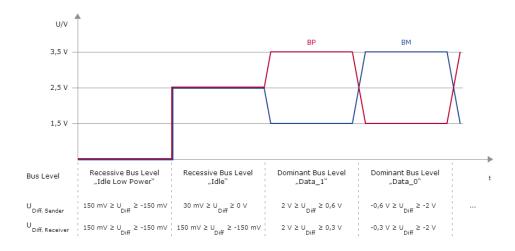

|   |     |        | 6.2.1.5 Bus Level                                 | 3 |

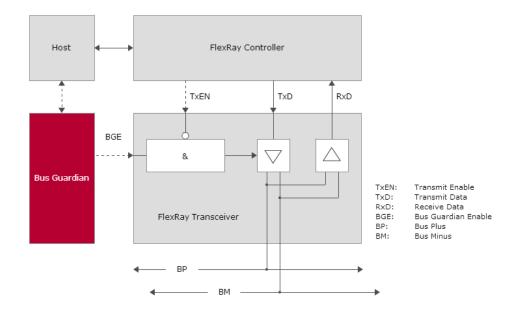

|   |     |        | 6.2.1.6 Bus Guardian 6                            | 3 |

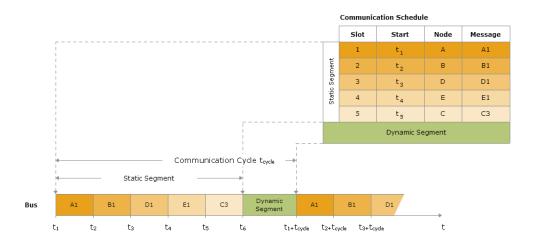

|   |     | 6.2.2  |                                                   | 4 |

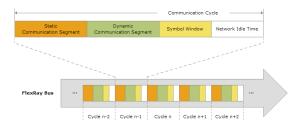

|   |     |        | 6.2.2.1 Communication Cycle 6                     | 5 |

|   |     |        | 6.2.2.2 Static Segment                            | 6 |

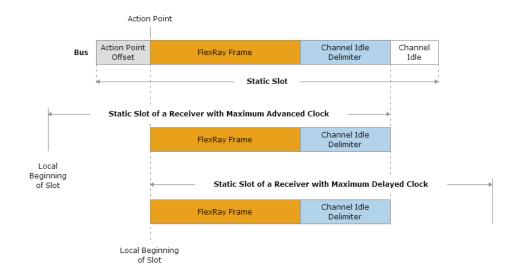

|   |     |        | 6.2.2.3 Static Slot                               | 6 |

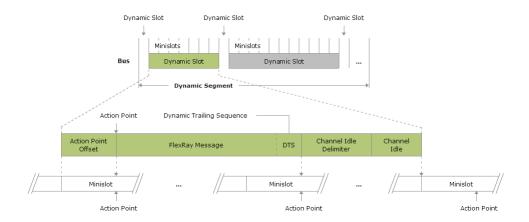

|   |     |        | 6.2.2.4 Dynamic Segment 6                         | 6 |

|   |     |        | 6.2.2.5 Dynamic Slot                              | 7 |

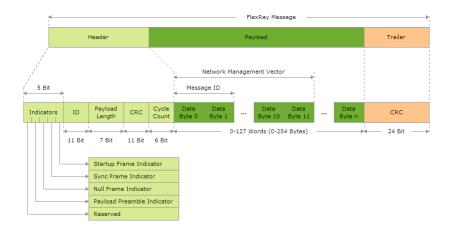

|   |     | 6.2.3  | Framing                                           | 8 |

|   |     |        | 9                                                 | 8 |

|   |     |        | , ,                                               | 9 |

|   |     | 6.2.4  | Synchronization                                   | 0 |

|   |     |        | · ·                                               | 1 |

|   |     |        | 6.2.4.2 Synchronization Method                    | 3 |

|   | 6.3 | Concl  | usion                                             | 7 |

|   |     |        |                                                   |   |

| 7 | Kos | stadin | Kotev: OSEKtime OS - Scheduling 79                | 9 |

|   | 7.1 | Introd | uction                                            | 9 |

|   | 7.2 | OSEK   | time                                              | 9 |

|   |     | 7.2.1  | Architecture of the OSEKtime OS 8                 | 0 |

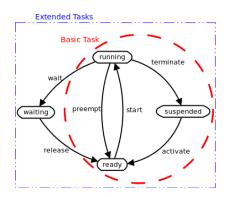

|   |     | 7.2.2  | Task state model                                  | 1 |

|   |     | 7.2.3  | Scheduling Policy                                 | 3 |

|   |     | 7.2.4  | OSEK OS as a subsystem of the OSEKtime 8          | 4 |

|   |     | 7.2.5  | Deadline monitoring                               | 5 |

|   |     | 7.2.6  | Interrupt management                              | 6 |

|   |     | 7.2.7  | Start-up synchronization                          | 7 |

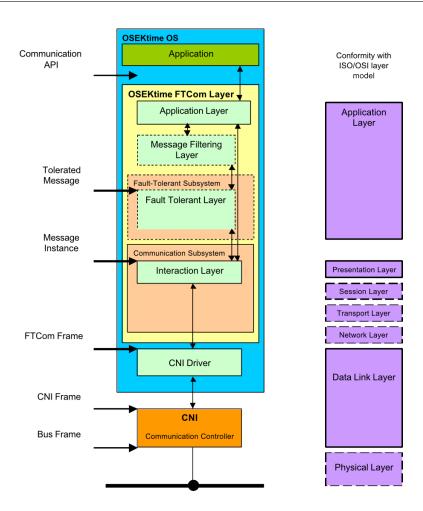

|   | 7.3 | FTCo   | m                                                 | 8 |

|   | 7.4 | Summ   | ary                                               | 0 |

| _ |     |        |                                                   |   |

| 8 | Phi | lipp F | Pickel: Testing vs. Verification and Model Check- |   |

|   | ing | vs. T  | Theorem Proving 93                                | 3 |

|   | 8.1 | Introd | uction and Motivation                             | 3 |

|   | 8.2 | Testin | g vs. Verification                                | 3 |

|   |     | 8.2.1  | Testing                                           | 3 |

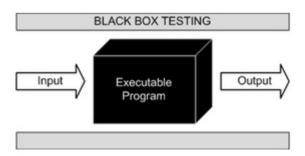

|   |     |        | 8.2.1.1 Black Box Testing 9                       | 4 |

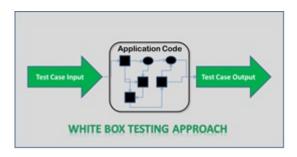

|   |     |        | 8.2.1.2 White Box Testing 9                       | 5 |

|   |     | 8.2.2  | Inspections, Reviews and Walkthroughs 9           | 6 |

|   |     | 8.2.3  | Verification                                      | 6 |

|   |     |        | 8.2.3.1 Runtime Verification                      | 7 |

|   |     |        | 8.2.3.2 Formal Verification 9                     | 7 |

## Contents

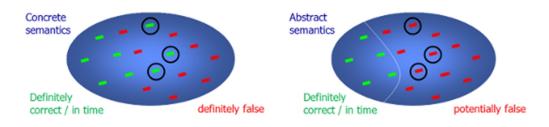

| 8.2.3.3 Abstract Interpretation    | 98  |

|------------------------------------|-----|

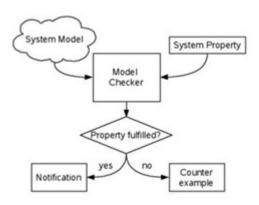

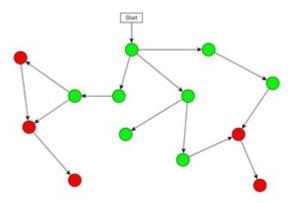

| 8.3.1 Model Checking               | 99  |

| 8.3.1.1 Bounded Model Checking     | 100 |

| 8.3.2 Theorem Proving              | 102 |

| 8.3.3 Advantages and Disadvantages | 102 |

| 8.4 Conclusion                     | 103 |

|                                    |     |

| Bibliography                       | 105 |

## 1 Fan Zhuosi: Introduction to the ES

## 1.1 Introduction

Embedded systems are computer systems that are designed for specific applications. According to the definition from IEEE: "an embedded computer system is a computer system that is part of a larger system and performs some of the requirements of that system; for example, a computer system used in an aircraft or rapid transit system" [Crn]. Embedded systems are unlike a general-purpose computer system, they are always dedicated for a special application, so that the developer could optimize them in order to reduce the size, power consumption and the cost. In recent years, with the development of the embedded technologies, embedded systems have been more and more widely used. From the small mp3 player, microwave oven to the big plane, the devices with embedded systems are all around us. It could be said, embedded systems have already changed our way of life. In this paper, we will give an introduction to the embedded systems.

This paper is structured into four parts: the foundation of embedded systems, the composition of embedded systems, application fields and problems. Chapter 1.2 gives an overview of embedded systems and defines their conception clearly. In this chapter the main differences between an embedded system and a personal computer will be figured out. We will also have a look at their history and figure out what characteristics do they have so that it could be so widely used. In Chapter 1.3, the structure of an embedded system will be given. We will show how an embedded system can be composed and the functionality of their components. In Chapter 1.4, we will discuss its particularly wide range of use. In Chapter 1.5, we will discuss their problems.

## 1.2 The foundation of ES

Embedded system is also known as embedded computer system, just like its name implies, it is a special form of a general computer. In order to understand what exactly an embedded system is, we must give a clear definition of a computer.

"A computer is an electronic device, operating under the control of instructions stored in its own memory. These instructions tell the machine what to do. The computer is capable of accepting data (input), processing data arithmetically and logically, producing output from the processing, and storing the results for future use. Most computers that sit on a desktop are called PC, or personal computers" [Uni00]. Briefly, it is an electronic device for data processing and instruction executing. As we all know, a complete computer system

includes hardware and software. Software is the stuff that manages the funktions of your computer (cf. [Uni00]). It is a set of instructions and data that are needed for running a program. And hardware are the physical pieces or components in the computer (cf. [Uni00]). These physical components constitute an environment or a platform for executing instructions and performing the functions. They are the components that could be touched. The hardware of a computer is majorly composed by the central processor, memory, power, hard drive and peripheral devices. Each component performs its own functions.

Nowadays the well-known desktop and laptop computers are usually with powerful performance. They are able to perform different functions by installing different software. They are not limited to a specific field. But with the development of the computer technologies, computers have been more and more widely used in some specific fields. A lot of dedicated equipments require the use of computer for data handling, automatic process control or other special purposes. In such equipment, the computer is application dedicated, and is a fixed part in the entire device or system (cf. [Rui]). We call it an embedded system. In short, "embedded systems are information processing systems embedded into enclosing products" (cf. [Mar10]).

## 1.2.1 Embedded system vs PC

Embedded systems are always designed for special equipments, so they must be designed to be suitable for those devices. The requirements of size, cost, power consumption and reliability will be taken into consideration. And that makes the embedded systems very different from the general-purpose computer. In the following, we talk about some concrete differences:

## • CPU

A general CPU is designed for the needs of the general-purpose computer. General CPUs have very high computing speed, so that they can complete a task faster or have better performances in multitasking. The general CPU structures are very similar. Embedded systems always use CPUs that are specially designed for embedded applications in the considerations of energy, size and cost. So according to the different embedded applications, the structures of the embedded CPUs should be dedicatedly designed. Some need to be designed to be more reliable, so that they could be used in a machine which works in harsh environments. Some need to be designed as small as possible in order to be packed into some small devices. There is a wide range of embedded CPUs. According to incomplete statistics, there are more than 1000 kinds of embedded CPUs worldwide (cf. [Rui]).

## • OS

It is almost impossible that a general-purpose computer has no operating system. But the situation in embedded systems is quite different. We do not need operations in some particularly easy embedded systems, functions can run directly on the hardware platform (cf. [Rui]). It is not necessary to set an operating system on them. But in other complicate

embedded systems, the support of multi-task may be required, and then we need a dedicated operating system for them. These operating systems are also totally different from the desktop operating systems. We could only do the operations or functions that are in connection with the specific applications. There are no other functions in these operating systems.

## Expensibility

Generally, an embedded system can not be upgraded like a general-purpose computer. We usually can not improve its performance by extending or upgrading hardware. An embedded system is a fixed part in a device. The structure, installation and even interfaces are fixed. They are intergraded in a dedicated computer system. So an embedded system generally does not have expansion capability on its hardware. We also can not achieve another function in an embedded system by installing another software on it. Its software is generally also a fixed part in the device. The functions are dedicated for the equipment demands, so in its relatively long life cycle, we do not need to make changes to its software (cf. [Rui]).

#### • Standardization

PC is the most popular general-purpose computer. Its mainboard, memory, power, external device interface and even the screws, that we need to assemble the chassis, are fully standardized [Rui]. There are hundred brands of main boards or memories. But they all have an uniform standard. This standard specifies their sizes and the form of their interfaces so that these components could be massively produced according to the standard. They are appropriate for every PC. So the PCs could be also completely produced in a large-scale. PC standardization is reflected not only in the hardware but also in the software. Its software has also a high standard such as operating system standard (cf. [Rui]). Windows could be applied in almost each PC. Embedded systems do not have such a standard like PC. Each embedded system is function-specific designed, the design and production of its hardware and software must be in line with the applications. It could be totally different from another one. So it is impossible to develop an unified standard for embedded systems, and it is also the reason that the embedded market could not be monopolized by one or two companies.

#### 1.2.2 Characteristics

The reason why the embedded systems could be so widely used is that they have the following attributes.

## • Low power consumption

"Computational energy efficiency is the key characteristic of execution platform technologies" [Mar10]. Since the embedded systems are usually used in some small devices, the power resources are relatively limited. For example, the electronic watches. The low energy consumption requirement should be considered at first. No one wants to replace the battery for his watch every month.

### Dependable

An embedded system must be reliable and maintainable. "Reliability is the probability that the system will not fail. Maintainability is the probability that a failing system can be repaired in a certain time-frame" [Mar10] The embedded systems are always intergraded into a device. The entire device could not work if the embedded system does not work or breaks down. The assembly and heat-dissipation problems must be considered. As a fixed part in a device, embedded systems must be designed to avoid these problems. Reliability and maintainability are particularly important for them.

#### • Dedicated user interface

"Most embedded systems do not use keyboard or large monitor for their user interface. Instead, there is a dedicated user interface consisting of push button, steering wheels etc" [Mar10]. Users can only control the device, they can not modify the programs. The positive side is that, it is good for the security of the system.

#### • Real-time efficiency

Embedded systems generally have real-time requirements [Rui]. An embedded system is usually used for controlling of procedures. A procedure is a series of processes. Embedded system could set a time frame. A process must be finished in this certain time frame. That is the real-time requirement. It is a very important feature in the assembly line application.

## 1.2.3 The history of ES

From the invention of microcontroller in 1970s to the large-scale use of various kinds of embedded microprocessors, embedded systems have a history of more then forty years.

The first high-volume production of an embedded system is the D-17 automatic navigation control computer system in the Minuteman 1 missile which was launched in 1961. It can reprogram the guidance algorithms, so that the missile could obtain higher accuracy. Another significance of embedded systems is that, it made the price of intergraded chips drop from 1000 dollar to 3 dollar each. Intergraded chip commercial became possible<sup>1</sup>.

In 1976, Intel launched its first single chip 8048. After that in the early 1980s, Intel improved its 8048. The company launched its new single chip 8051. It was the most famous single chip in the world<sup>1</sup>.

In 1990s, the performance of embedded systems has been further improved. The real-time conception appeared. Embedded systems began to support multitask. Many companies began to develop their own embedded systems.

In 2000s, with the development of the embedded technologies, embedded systems had a considerable improvement in reliability, power consumption and performance. They could be packed into a very small device but with high

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/Embedded\_system, accessed on 2013-01-17

performances, you can use it for more than two or three weeks without changing. Ipod is a good example. Its success could prove the importance of a good embedded system.

Nowadays the multi-core technology is coming into our life. It could support multi-task better. It is also the direction of the future technology.

## 1.3 The composition of ES

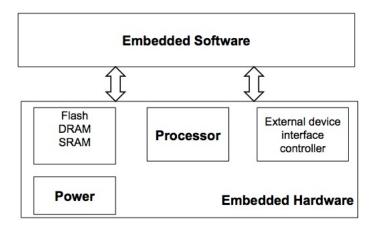

"An embedded system is one that has computer-hardware with software embedded in it as one of its most important components. It is a dedicated computer-based system for an application or product. It may be either an independent system or a part of a larger system" [Kam08]. As we mentioned above, in order to be suitable for those equipments, each embedded system for such applications or products is customized. The size, functionality, performance and structure of those embedded systems have to be modified correspondingly according to the embedded demands. So there might be quite a lot of differences with each other. But in the perspective of computer principles, it should also consist of hardware and software.

### 1.3.1 Embedded hardware

"In terms of hardware aspect, this can mean limitations in processing performance, power consumption, memory, hardware functionality, and so forth" [Noe05]. The hardware part is majorly composed by an embedded processor, memory, communication interface equipment and human-computer interaction device.

## • Embedded processor

It is the most important part in the entire embedded system and also the core member of the hardware part. It controls the operation of the system. There are a wide variety of embedded processors with different function and performance, from the 8-bit microcontroller which is still widely used to the latest 32-bit, 64-bit embedded CPU. With the improvement of processor technology, embedded processors made a great progress in size, power consumption and performance. But all of them have a common characteristic, they must be refining designed. That means they will not leave too much room on the computing speed as a general-purpose CPU. Nowadays the most popular used embedded processor is a microcontroller. "A microcontroller is a single chip, self-contained computer which incorporates all the basic components of a personal computer on a much smaller scale. Microcontrollers are often referred to as single chip devices or single chip computers" [ES002]. They have the advantages of small size, high reliability, low power consumption and cost. So they have a the market share of more than 70 percent (cf. [Rui]).

## • Memory

A memory is used to storage of data and programs. There are many kinds of memories. For example: RAM, ROM and flash memory. "RAM (Random access memory) consists of memory the CPU can both read from and

write to. RAM is used for data memory and allows the CPU to create and modify data as it executes the application program" [ES002]. But the problem is that, when the power goes out, the content in the RAM will get lost. "ROM (read only memory) is typically used for program instructions. The ROM in a microcontroller usually holds the final application program" [ES002]. It can hold the data when the power turns off. But you could not change the content in it any more. The flash memory combines the strengths of the ROM and RAM. It has a fast speed and could keep the data when the power turns off. So it has been widely used in our life.

- Communication interface equipment

Its role is to exchange the data between the devices. For example, USB interface is such an equipment for data exchanging between the devices.

- Human-computer interaction device

It services as a medium of communication between user and computer. It is divided into two major parts: in-put device and out-put device. Users can give an instruction to begin or control a process by using the in put devices such as keyboard and touchscreen. The computer could give the answer through out put devices such as monitor and voice out-put.

#### 1.3.2 Embedded software:

Embedded software: The software part of an embedded system is actually an embedded operating system. An embedded operating system is a special kind of operating system. An operating system manages the hardware of the computer and controls the operation of programs. It provides also an user interface which serves as a bridge for communication between user and computer. The operating system could interpret the instructions that the users give, so that the hardware could understand what they should do in order to achieve the functions. The main principles of the embedded operating systems are similar with a normal operating system. But its functions and operations are customized for the devices. It has generally fewer functions than a normal operating system and has a different user interface.

According to [Shi], the operating system can generally be classified into three categories: order execution operating system, time-sharing operating system and real-time operating system. In an order execution operating system, there could be only one program in the system. This program occupies the whole CPU itself. In the time-sharing operating system, there could be more programs in the system. All the programs share the CPU. In a real-time operating system, there could be also programs in the system. Each program has a priority, only the task with the highest priority could occupy the CPU.

We often use a real-time operating system in an embedded system. A real-time operating system can support multi-tasking, it organizes the sequence of the tasks according to a plan. Each program must be finished in a certain time frame. Users need not to adjust the sequence manually. The programs run automatically. So the operation of the system becomes easier. Because of

the advantages of better support of multi-tasking and the easy operation, so it could be widely used in the embedded system. According to [Mar10], a real-time operating system could be still classified into two categories according to the real-time constraints: hard real-time operating system and soft real-time operating system. A hard real-time operating system means that, if a program could not be finished in a certain time frame, the system will result in a serious consequence. For example, every process in a flow line machine must be finished in a set time, or the product will be scrapped. You can change this set time, but the process must be finished on time. The other real-time operating systems are soft real-time operating system. They are more flexible, they could tolerate some occasional time-out errors. Developers could choose which real-time operating system that is more suitable for the application according to demands.

Figure 1.1 shows the structure of ES briefly.

Figure 1.1: the composition of an embedded system (according to [Rui])

## 1.4 Application fields

Embedded systems have already covered a huge range of applications. We enumerate some concrete application fields in the daily life.

### • Consumer electronic products

Embedded systems have been most widely applied in this area. The products in this field are the most common products in our life. For example, a mp3 player and a mobile phone. The embedded system is the core member in these devices. Programs have been defined in embedded system in advance. The equipment can run the functions when it receives the command. In a mp3 player, it could control the play of music. You can easily push the "next" or "back" button to play a previous or next song or steer the "volume" wheel to control the volume. These operations are actually

the instructions that you give. Embedded system could tell the hardware what to do after executing the instructions. A mobile phone has generally more functions than a mp3 player. Most handy phones have already intergraded mp3 function. So they usually have a more complex embedded system. You may bring two or three such products with you when you go to school or go to work. Another good example is a washing machine. Now the operation of a washing machine has been strongly simplified. You can just easliy choose the function on the control panel what you want to wash, and then the machine could do the program automatically. All these programs are controlled by inner embedded system.

## • Manufacturing equipment

The example is a production line. An embedded system could help it to control the processes. The production of a product could be accurately divided into several steps. An embedded system will control what should be done in which step. More importantly, it could enhance the accuracy of the production process, so that each end product could get the same quality. The application in this field makes the massive manufacture of a product in a short time become possible.

#### Automotive

All the electronic equipments in a car are controlled by embedded systems. The automatic air-conditioning system could adjust the temperature automatically. The media system could achieve the functions of playing music, GPS navigation, rear camera display and so on. More importantly, some system could save your life in the emergencies. For example, the esp system. It could detect which tire loses the grip and then take the appropriate measures to ensure that the car is not out of control. A car is something that is armed by electronic equipments which are controlled by embedded systems.

## • Public management

Embedded systems are usually used in the public management as well. The traffic system could tell you when you can go across the street, when you must wait. The video surveillance system could record and upload the videos automatically. Now these two systems are always intergraded into one combination system to manage the traffic. When something happens, the police could easily find the videos.

## 1.5 Problems

We talked about lots of the advantages of embedded systems. They have also problems. The problems come from two aspects: the side of developer and the side of use. For the developers, they have to design both the hardware and software parts of a device. That makes more difficulty in the development. For the users, they could not upgrade or make changes to the embedded system themselves. If the system gets into trouble, the problem could only be solved

by technical staff. But in general, the advantages of embedded systems far outweigh their disadvantages.

## 1.6 Conclusion

This paper began with the definition of an embedded system. And then introduced the differences between a personal computer and an embedded system so that we could have a concrete conception of embedded systems. It also summarized the characteristics of embedded systems so that they could be widely used. The structure of the embedded systems have been divided into several components. The functions of each component have been defined. In the last two chapters, we presented some application fields of the embedded systems and also problems. This paper explains the importance of the embedded systems. With the development of embedded technologies, whey will be more widely used in the future.

## 2 Johannes Muhr: Cyber-physical Systems

## 2.1 Introduction

In the past decades the information and communication technology (ICT) has developed in an unbelievable velocity. In the middle of the nineties, many people probably didn't know much about the Internet, maybe never heard of it at all. Nowadays, a life without Internet and the correspondending ICTs is unthinkable. In industraial countries, everybody comes in contact with different kinds of ICTs in daily life, as it is meanwhile in nearly ever product or used in services like the energy supply [BBB<sup>+</sup>10]. Thus, Embedded Software was developed further with a similar speed, using technologies of ICTs. Embedded Software exists in small, daily used systems like a washing machine and smartphones, but by now also in larger systems (vehicles) subsist a lot of small embedded systems like in the antilock brake system (ABS) or in the electronic stability program (ESP) [Mar11]. Consequentially the market volume of embedded systems achieved in the year 2010 already an amount of 19 billion [BBB<sup>+</sup>10]. The next aim of the scientists is to create Cyber-physical systems (CPSs), an advancement and connection of Embedded Systems (ES). This work deals with that new topic. Section 2.2 explains the development of CPSs and its basic architecture, Section (2.3) deals with the challenges of CPSs during the process of creation. In the last part, Section 2.4, some modelling techniques and ways that lighten the design process are addressed.

## 2.2 Cyber-physical Systems

In the first part of this work, the question "what do you understand under the term CPS and how has it developed?" is answered. It starts with the development of CPSs, afterwards the term per se and also the structure of these Systems is explained. At the end of this part, CPSs are compared with the traditional Embedded- and Real-Time Systems and the visions and main benefits of CPSs are announced.

## 2.2.1 The development and concept

The term Cyber-physical System (CPS) is a quite new notion in modern sciences. It emerged around 2006 in the National Science Foundation in the United States [LS11].

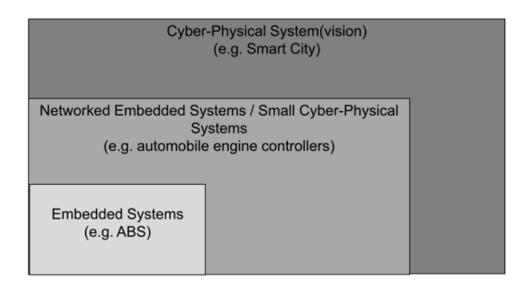

Figure 2.1: Evolution of Cyber-physical Systems

Figure 2.1 ([BGC<sup>+</sup>11]) shows the evolution process of CPSs. The process started with the evolution of small Embedded Systems (ES). Those traditional ESs were small single systems which combine physical processes with computing. But many of these ESs just replace mechanical work. Over time, new techniques and simultaneously better systems have been developed. The result was a networking of some different ESs which communicate with each other. Now, modern systems like automobile engine controllers can't be simply replaced through mechanical devices anymore [BGC<sup>+</sup>11, Wol09].

The question is, whether these networked ESs can be seen as CPSs. That is not easily to be answered, especially as the German BITCOM uses CPS as a synonym for ES [BBB<sup>+</sup>10]. So in the view of the BITCOM, CPSs are just common systems, which are already available. On the other side, the National Science Foundation (NSF) clearly differs between the two terms and says that CPSs are not the "traditional post-hoc embedded/real-time systems and not today's sensor nets" [Gil08]. So, the NSF recognizes in CPSs a larger dimension than it is the fact in the common ESs. To consolidate these facts we say that the networked ESs of today are a kind of "small" CPSs. But the actual meaning of the NSF was different. This concept will be explained in the following section.

Due to the huge scope of the term several definitions are used. The following two examples express the fundamental factors of CPSs.

"Cyber-Physical Systems (CPS) are integrations of computation with physical processes. Embedded computer and networks monitor and control the physical processes, usually with feedback loops where physical processes affect computations and vice versa." [Lee08]

"Cyber-physical systems (CPS) are physical and engineered systems whose operations are monitored, coordinated, controlled and integrated by a computing and communication core." [Sta10]

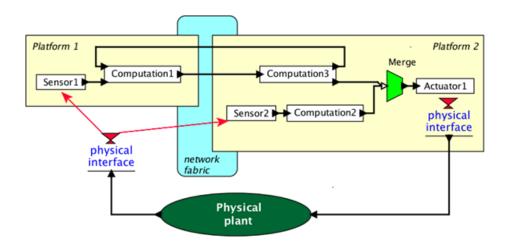

As we can see in these two definitions, the key point of CPSs is the two way interaction between physical laws and computation. In CPSs, these sciences are not united, but rather intersected. Instead of concentrating on single topics of the system, we should focus on the interaction of them. Figure 2.2 ([LS11]) illustrates an abstract example of the structure of CPSs. Especially the interaction of the individual elements from the different components is clearly shown [LS11].

Figure 2.2: Abstract structure of Cyber-physical Systems

There are three main parts in this illustration (Figure 2.2), the first part is the physical plant, which is simply everything that is not realized with computers, it can include various things like mechanical parts and so on. The second part involves one or more computational platforms with components like computers, sensors and actuators. Sensors measure the results of the process and actuators impact on base of the elaborations on the physical plant. The last part is the communication (network fabric), which provides the communication mechanisms for the computers of the different platforms. The ICTs provides different ways to execute the data communication in the network fabric. Together, the network fabric and the computational platforms form the "cyber" in the term Cyber-physical Systems, whereas the physical plant stands for the "physical".

In this example (Figure 2.2), there are two platforms, each platform has one sensor measuring the impact of the physical processes. The platform 2 includes an actuator that controls the physical plant. Computation 1 sends the measured data via the communication network (network fabric) to computation 3.

Each computation element implements a control law giving commands to the actuator, based on the data received from the sensors. So the commands of computation 2 and the consolidated commands of computation 1 and computation 3 are merged and sent to the actuator.

Together, the structure of CPSs is characterised through the complicated interaction and connection of Embedded-, Computational Systems with (worldwide) networks. CPSs can communicate with communication platforms like the Internet with widely distributed systems. To be more generally, CPSs are the intersection and the direct connection between the physical and digital world. Though, the digital world involves various components like the communication medium, computers and so on [Bro10].

#### 2.2.2 Classification

We have seen in the first section (cf. 2.2.1) that it is often difficult to classify the different Systems to their belonging. We learned also something about the special characteristics of CPSs. In this section, CPSs are classified in the overall context and challenges of this classification are introduced and discussed.

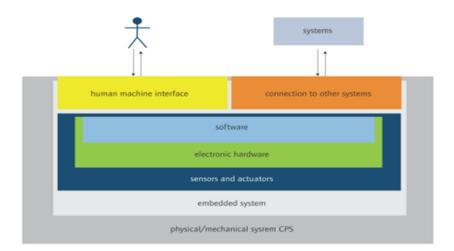

Figure 2.3 ([Bro10]) shows the architecture of CPSs, where we can see that a major part of them is built up on ESs and all the corresponding components like: sensors, actuators, hardware, software and also the interfaces to users and further systems.

Figure 2.3: The Architecture of CPS

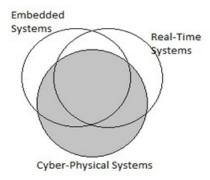

Therefore it is sometimes not easy to conclude if a system is still an ES or already a small CPS. Figure 2.4 illustrates again the large overlap of Embedded-,

Real-Time (RTS)- and CPSs<sup>1</sup>. It is clear that there is an overlap between CPSs and ESs as each CPS needs embedded software to work and integrates computation with physical processes. But the difference to the traditional ESs is that CPSs do not simply replace mechanical work and they have the focus on a multitude of devices. Together, CPSs are more distributed and more interactive with the nature [Bro10, KKI+11, Wol09].

In comparison to the modern ESs, CPSs work and communicate in a very large system, whereas the ESs are within a well-defined system. An example is the mentioned automobile engine controllers (ES, "small" CPS) in a car. An example for a CPS would be a networked intelligent intersection, where a set of cars are communicating with each other. Additionally, the cars can access to detailed information from the infrastructure and the other way round. The task of the whole system (cars, traffic lights, etc.) is to arrange an efficient traffic flow in real time. For example the system must notice if there are a lot of cars waiting in front of a traffic light. Then it should try to dissolve the jam as soon as possible in consultation with the other elements of the system (other cars and traffic lights) [Gil08].

Figure 2.4: Overview of Embedded-, Real-Time- and Cyber-physical Systems

In comparison with Real-Time Systems (RTSs), it is again obvious that CPSs have tasks that must be executed periodically or that they have deadline or latency constraints. But the difference is that in the classical field of RTSs, the system does not interact in the process from itself. So the system monitors the action and may give some signals, but it does not try to solve the problem itself. In the last example with the intelligent intersection (cf. 2.2.2) we have seen that CPSs should try to find its own answer. Examples for classical RTSs are monitoring consoles in hospitals. They supervise certain values and give alarm if a critical limit is reached; still they do not interact in the process and do not help the doctor to reduce the increased magnitudes [LCS<sup>+</sup>88].

<sup>&</sup>lt;sup>1</sup>Figure at the address http://scm-l3.technorati.com/10/02/03/4111/cps-technorati.jpg

#### 2.2.3 Vision and Aims

In this section the focus lies on the actual vision and goals of CPSs. The intension of CPSs is to create a huge network with distributed systems that can interact and communicate with each other and with humans through new modalities. Based on the new abilities of interaction with the physical world, the high functionality and reliability; CPSs will be a key enabler for future technology developments that far exceed the levels of autonomy today [BG11].

That results in the area of automotive as an extensive network between all vehicles and the complete infrastructure, like traffic lights or parking decks. Due to the continuous real-time data exchange (about weather, information about the traffic, etc), the distributed traffic management systems can work as a planning and coordination assistant and react on unforeseen situations like traffic jam. Through an optimal traffic management with an early recognition of threats and barriers, the road safety (less accidents with other cars or passengers) may be increased. Further, through this intelligent planning the road users may save time and money due to the reduction of fuel consumption and the CO2 saving, which is also important for the environment protection.

The grand vision of Cyber-physical System is the Smart City [BGC<sup>+</sup>11], which is a cross domain topic which involves different sectors, like smart mobility, smart health, smart grid, smart factory, smart home and so on. These sectors are all connected with each other and manifest a lot of interdependencies. An example for the combination of smart home and health is a system that recognizes and gives an alarm signal, if a room is (for a defined amount of time) empty and the stove is on. So, the different future scenarios are not isolated from each other, instead-, there are a lot of relationships and dependencies between the distributed subsystems.

## 2.3 Challenges

We have seen that CPSs are very complex and large systems, with a wide range of applications. It includes the mentioned traffic control, safety and advanced automotive systems, avionics, environmental control like the observation of water resources, infrastructure control, communication systems, electric power and so on. Altogether, most applications are safety critical or at least critical in that each system affects other areas [Lee06]. So it is obvious that the design and modelling of these systems is very challenging. Some of the challenges that arise during the design process of CPSs are introduced and discussed in the next sections.

## 2.3.1 Non-functional Challenges

It is very important that CPSs meet the dependability aspects (reliability, maintainability, availability, safety and security) to guarantee a save use of the system. The reliability, so the probability of failing, must be limited to a value near zero, since most systems are critical. As this is not 100% guaranteed, the failing system must be repaired in a minimum time-frame (high maintainability) so that the negative effects through the failure of the system (damage, costs, etc.) are as small as possible. The reliability and maintainability should be high in order to fulfill a high availability. The property of causing any harm through a system failure must be again very low (high safety). The challenge and risk of CPSs is that even small errors can lead to enormous damage and an endangering of human life. For the same reasons, but also in the interest of data protection, it must be guaranteed that the confidential data of the systems stays conversant. In equal measure, the system must be protected from hostile takeovers (high security). This is again a very demanding challenge as the systems are very large and interact with each other; therefore there are a lot of possibilities to influence the process in a malicious way [Mar11].

## 2.3.2 Digital and analog world

An elemental problem of CPSs is the gap between the digital and analog world. While the physical part is based on the classical continuous math, the digital information processing (which involves models for the implementation, pattern for data acquisitions, processes and architecture of the digital systems) is based on discrete logic. But through the interaction of the physics with computation, CPSs must consolidate two (from the origin) very different domains. Models that constrain themselves to only one of the two approaches (digital or analog) are in those cases useless. Therefore, there is a need of an integrated systemand model-layer, which combines the diverse mathematical ways. To join the indivudual models (digital and analog), qualified levels of abstraction have to be found. A model which is able to consolidate the analog and digital domain is called Hybrid-System [HKPV98, Bro10] (cf. Section 2.4.3).

## 2.3.3 Complexity Challenge

A further problem is the environment that interacts with the systems. Physical processes are by nature concurrent, which means that there are parallel processes. An additional difficulty is the fact that these processes cannot be exactly foreseen [Lee06]. Even if a system is engineered reliable and predictable, the nature can still manage to expose the system to an unknown condition. CPSs are working consequently in an uncontrolled environment. As a result, CPSs must be adaptable to failures as the availability can never be absolutely guaranteed [Lee08], although this is very difficult, since a lot of systems are interdependent and need data from each other to execute perfectly.

Further, due to this networked environment and the combination of different disciplines like computer science and electrical engineering, all standard engineering methods become more complicated. Based on the dimension of those systems, different modelling techniques from different branches are used that are not directly compatible and suitable. Divisions of labour and decentralized working are further keywords that complicate the engineering process relevantly [Bro10]. Consider the smart city that was introduced in Section 2.2.3, it is very difficult to arrange the interdependencies and the involved developers in the modeling of the system. These properties and conditions influence the whole engineering process. At the end of this process there is once again a huge challenge. Testing the major network with all the different subsystems seems to be very challenging [Lee08].

## 2.3.4 Lack of Timing

Another challenge of CPSs is the software part. A simple programm with no concurrency can perform on a computer with 100% reliability, but in CPSs there are instead of small programms huge software systems. Keeping this software (or rather the software model) in that complicated dependency consistent is a big challenge. A further problem are the high interconnected sensors and actuators. In CPSs the interaction between sensors and the hardware of actuators (cf. Section 2.2.1) is very important, but this specific behavior is not very well represented in programming languages. The problem is that imperative or sequential programming languages do not match well with the needs of CPSs. Even the simplest program is in the context of CPSs not reliable, as the aspects of the systems behavior are not expressed by the language. It can execute perfectly and match all semantics, but it can still miss real-time constraints, because timing is not in their semantics. But meeting this real-time constraints is essential for CPSs. This is an issue from the very first time in the development process, where the concurrent processes must be known and illustrated in models. This problem becomes more complex and worse if the systems get bigger and bigger, as it is the case with CPSs [DLSV12, Lee08, Mar11].

## 2.4 Modelling techniques

The challenges discussed in the last section (cf. 2.3) show the huge amount of problems that need to be overcome. In the next section, some models and techniques, which help and simplify the modelling process, are explained.

### 2.4.1 Models of Computation

In Section 2.3 it is mentioned several times that a lot of the problems emerge from the heterogeneity and complexity of CPSs and their applications. To relieve that problem in the design process, qualified levels of abstraction have to be found that use modelling techniques with well-defined, expressive and precise semantics. This can be fulfilled with the Model of Computation (MoC), which is a defined set of operations used in computation and their respective costs. There are a variety of such models existing (Turing machine, finite-state machine, random-acess machine and so on), so it is usually not easy to find a suitable model. Especially the heterogeneity of CPSs forces the developer to combine a multiplicity of models.

In the case of CPSs, the MoCs try to illustrate the concurrent composition of actors. An actor is a component that reacts to stimuli at input ports and produces stimuli on output ports. The interaction of the actors is defined by three sets of rules. The first set specifies the constitution of the components, which means having an overview about the whole architecture of the systems from the beginning, knowing which systems are dependent and affect each other. Secondly, you have to specify the concurrency mechanisms. After knowing the interdependencies of the subsystems you have to determine how the systems give semantic to the concurrency. For example, define whether the systems execute simultaneously or if they share a notion of time. The last set of rules defines the semantics of the communication mechanism. Specifying, if the subsystems communicate via synchronous or asynchronous messages or which protocols for the data exchange are used and so on. The challenge in the design process is to identify the actually needed MoCs from the huge amount that is available [DLSV12, LS11, Sav98].

## 2.4.2 Multimodelling

It is already mentioned in this work that interfaces are the key issue for CPSs (cf. Section 2.2.1). Through the magnitude and heterogeneity of CPSs and the resulting work-sharing processes, a lot of different modelling and specification techniques are used during the design process and further actions (various MoCs). The problem is that the semantics of the different MoCs are not directly compatible and comparable. So the main focus should lay on the integration of the multiple models to get the interfaces operating with each other. This is called "multimodelling". Good software architecture for a CPS and their interoperations will only arise from an excellent and errorless understanding of the semantics of interoperation (cf. Section 2.4.1). Further, the deterministic aspects of elaboration must be a very important property of these systems, especially through the huge amount of interfaces to other subsystems. A particular input must always lead to the same output in all dependent systems. Otherwise, the requirements of the non functional challenges (cf. Section 2.3.1) could not be achieved, as the system has no operation mode that leads to a reliable output. Non-determinism is only used if it is needed by the application. Through this kind of modelling, better concurrency mechanisms than with the normally used models and a better interoperation are possible [DLSV12].

## 2.4.3 Hybrid Systems

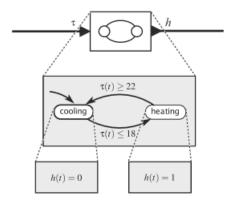

CPSs are the integration of computation, networking and the physical dynamics. Therefore, single models (cf. Section 2.3.2) that address only either to differential equations (continuous dynamics) or to state-machines (discrete dynamics) are in that case inadequate. Hybrid systems try to deal with this problem by providing a bridge between the state-machines and the time based models. The notion stands for a particular composition of continuous and discrete dynamics. In other words, the systems proceeds continuously, but has occasional jumps, corresponding to the state change in an automata. These transitions are caused either by the continuous evolution itself or by external events (stimuli on the input ports). A very trivial example from [LS11] is a thermostat, which has no continuous state variables, no output actions and no set actions (cf. Figure 2.5).

Figure 2.5: A thermostat with continuous-time output

Instead of a discrete input, the system receives a continuous time signal ( $\Pi$ (t)), the temperature at time t. Further, the thermostat has the two states, cooling and heating, whereat each state is associated with a time-based system (a so called state refinement labeled as "h(t)"). In a hybrid system, the current state of the state machine gives the dynamic behavior of the output (h) as a function of the input ( $\Pi$ ). In the example, the system produces a signal whose value is 0 when the heat is off and 1 when the heat is on. Such control signals could directly supervise the thermostat and drive it.

## 2.5 Conclusion

We have seen in this work that CPSs compromise models of physical processes as well as models of the software, computational platforms and networks. For developing CPSs the existing technologies are sufficient. They need new ones that combine the different models of CPSs and overcome the challenges. Although

in the meantime some tools that relieve the design process were developed, it is still a long way to develop dependent and large CPSs, but in foreseeable time physical computing will interact more and more in our life and will revolutionize a lot of areas like transportation systems, manufacturing, process control and power grids. There are already projects existing (for example project simTD in Germany) that explore and prove technologies like the car to car communication (like in the mentioned intelligent intersection (cf. 2.2.2)) and applications for a save and intelligent mobility. Altogether a save application of CPSs will lead to a more efficient and saver life for people all age groups and can also protect the environment [Sta10], as explained in this project <sup>2</sup>.

$<sup>^2</sup>$ www.simtd.de

# 3 Christian Lichtmannegger: Real-time systems

## 3.1 Introduction

Real-time (RT) systems are an important field in embedded systems and embedded systems are an important part of our daily life. This is called ubiquitous computing. It is no surprise when a person has 2 or more computers and if we count the embedded systems too, then people can easily have 10 or more. RT systems make a big part of embedded systems and therefore a big part of our life. A RT system produces a result in a given time interval. Because the aspect of time is mostly excluded in the majority of programming languages, so it is hard to make time itself part of your program. In addition, normal operating systems give a very good average efficiency but a RT task must finish in time, so the scheduling must be changed, to fulfill the timing aspect [Sta96b, YB<sup>+</sup>97]. Only those points show that RT systems can be a very interesting field of research. In this paper, I will examine some fundamental aspects of RT systems and show you some techniques to overcome the scheduling problems.

## 3.2 The basics

There are various definitions of RT systems but I focus on the one proposed by John A. Stankovic [Sta96a]. "Real-time systems are those systems in which the correctness of the systems depends not only on the logical result of computation but also on the time at which the results are produced." We can reduce this quote to two key messages.

**Logical result** That means if the system solves the problem or not

**Time aspect** That means how much time does it take to get the logical result

So we do not only have to focus on solving the problem, but we have also to consider how much time does it take. For instance, because if you sit in a car and have an accident then it is necessary not only that the airbag opens but also that it will open in time. This shows very well that RT systems can be safety critical [BLMSV98]. To get a better understanding of what RT systems are, I will give three examples of them.

Table 3.1 shows three different examples of RT systems. They have some common but also different aspects. All RT systems consist of a controlling part, that is the computer chip and the RT system itself, and a controlled part. That is the environment the computer interacts [Sta96a]. In case of

| Air-traffic control                                | Assembly lines in in-     | Remote conference        |  |

|----------------------------------------------------|---------------------------|--------------------------|--|

|                                                    | dustry                    | application              |  |

| Consist of a controlling and a controlled system   |                           |                          |  |

| Scheduling of processes to meet the RT constraints |                           |                          |  |

| Hard RT constraints                                | Hard and soft RT con-     | Soft RT constraints      |  |

|                                                    | straints                  |                          |  |

| Safety critical system                             | Less safety critical sys- | Not safety critical sys- |  |

|                                                    | tem                       | tem                      |  |

Figure 3.1: Examples of different RT system

the air-traffic control system the environment are the planes and the airports. In case of the assembly line example the environment is defined through the assembly line itself and in the example with the remote conference application the environment are the users of the system and their PCs.

But thats nothing special because this pattern of a controlling and a controlled system is caused by it's definition as an embedded system. Every embedded system consists of this two part. So RT systems are embedded systems by their definition.

The next common point is the importance of scheduling processes. This is exactly the second point given by the definition at the beginning of this article. The time when a result is produced is important. All RT systems have a special scheduling algorithm and I will examine some of them in the following chapter.

Despite those common points this systems have many differences too. Not to mention the different costs of an air-traffic control system and a remote conference application there are fundamental differences like safety criticalness. There is a strong relation between timing constraints and the safety criticalness of a system. You can use this simple thumb rule: The more safety critical the system is the harder are the deadlines of the tasks. Every task has its own deadline but it possible to miss the deadline in some case. If this is possible the deadline is called soft if not the deadline is hard (cf. [BLMSV98]).

In the example of an air traffic control system the deadlines are hard because the pilots need all the information in the right time to react and prevent a disaster. In assembly lines the deadlines are largely soft because if a task can not be executed in time then the system can reduce the speed of the assembly line to give the tasks more time to finish. The problem with that is that if the system often reduces its speed, you can produce less goods and therefore the rate of met to missed deadlines is an important mark of quality of those systems. In a remote conference application you have only soft deadlines because problems are just only annoying, if you hear a bad noise or see some skipped frames on the monitor, for example. But here also the rate of met and missed deadlines plays a role in quality (cf. [Sta96b]).

## 3.2.1 Different types of tasks

It's important to know that in a RT system you have to handle different types of tasks:

**Periodic task** This is the most simple task. Its deadline just repeats itself after a periodic time interval. So this task must be executed every n time units.

**Aperiodic task** This task has to be executed after an event occurs. So its deadline is defined through the time the trigger event occurs.

**Sporadic task** This task is quiet similar to an aperiodic task. The main difference is, that between two activations of a sporadic task a given time interval must have been passed. That means that after the first execution of the task you must wait until this interval passed before you can activate the task a second time.

## 3.3 Scheduling

## 3.3.1 Scheduling: The basics

Schedule is the process of allocating resources to various tasks. The main resources in computation systems are CPU resources and computation time. So you allocate a task to one or more specific CPU units for a specific time. The problem is that, in most cases, we do not exactly know how long it takes to execute a task. So we need a reference value and this is the worst case execution time. Because when you know, that a task takes between n and m time units, the task is definitely finished after m time units. So you can guarantee to have enough time for execution whatever happens. So a task is not only defined by its deadline, like in the above text, but also by its worst case execution time. To make it simpler I assume that a task always takes all the resources of a CPU, so only one task can be executed on the same CPU at the same time.

Scheduling in RT systems must meet two goals:

- 1. Meeting deadlines

- 2. Maximize resource utilization

The first point, that a RT system must meet its deadlines is essential and the key objective. But you have to think about resource utilization too. Those two goals often conflict each others. Because if you have so much resources too meet all deadlines whatever happens, then you normally have a very low resource utilization. This means that you have much unused CPU space and this makes the system more expensive. On the other hand, if you have a very high resource utilization then you have only few unused CPU space and if you have to execute an unexpected task you can not execute it. So you must find a good balance between those two key objectives (cf. [BLMSV98]).

There are two different approaches to meet those objectives. Static and dynamic scheduling.

## 3.3.2 Static scheduling

Static scheduling is to form a feasible schedule before runtime. That means that all the computation effort for scheduling is done before runtime and so less computation resources are needed during runtime. That makes the resulting system much cheaper.

## 3.3.2.1 Round Robin/Static cyclic scheduling

The most basic algorithm is called Round Robin. At the beginning there is a task pool and we just form a cycle from all those tasks. So we have a cycle with every single task in it. During runtime the tasks of the cycle will be checked if they can be executed. That means that there are enough resources free to execute it. If a task can be executed then it will be started immediately. Else the next task will be checked. This algorithm does not care about deadlines and the only good thing about it is that every task is checked once in a cycle but it could happen that important tasks must wait very long until execution (cf. [BLMSV98]).

| Pro                                                                                          | Contra                         |

|----------------------------------------------------------------------------------------------|--------------------------------|

| <ul> <li>Very low memory allocation</li> <li>Every task is checked during a cycle</li> </ul> | Many deadlines could be missed |

|                                                                                              |                                |

A little improvement of the standard Round Robin approach is to duplicate important tasks, so they appear more often in the cycle. This little change seems to reduce the missing deadlines problem significantly but it also increases the cycle length. The result is although important tasks are checked and executed more often the "normal" tasks lack of execution. In addition it takes longer to go through the cycle so the execution problem is increasing too.

| Pro                                              | Contra                                              |

|--------------------------------------------------|-----------------------------------------------------|

| • Very low memory allocation                     | • We can not predict that all deadlines will be met |

| • Increased number of checks for important tasks |                                                     |

Figure 3.2: Cyclic algorithm every LCM

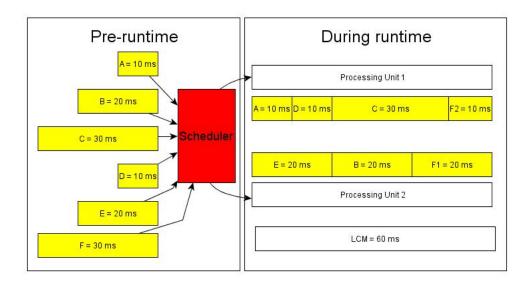

## 3.3.2.2 Cyclic static table driven algorithm

A very efficient algorithm is a cyclic algorithm which repeats every least common multiply (LCM) of the task length. If there are tasks that take 10, 20 and 30 ms of worst case execution time, then the LCM of those tasks is 60 ms. So the scheduler forms a cycle length of 60 ms. Now the scheduler looks at the deadlines of the tasks and tries all permutations of those tasks, so they are all finished in time. If the scheduler finds a proper schedule, then the work is done. This cycle is repeated continuously during execution time of the system. An example of this technique is shown in Figure 3.2.

If the scheduler can not find a feasible schedule then more CPU resources must be added. In case of a very long task, the scheduler can split this task into independent subtasks, to get a better usage of the resources. Those subtasks can be executed on their own and at the end of computation the results are put together to form the final result of the task. This is only possible if a splitter tasks does not need information from another splitter task to continue. It could happen that there is some unused computation time at the end of the cycle and if that is the case it could be possible to reduce the number of CPUs to get a better capacity utilization.

Because in worst case the scheduler must check all permutations of tasks to find a feasible schedule and additionally he can split up tasks and make even more tasks, the computation effort for creating a schedule is growing exponentially. The good thing is that all that effort is done before runtime. That results in less wasted computation resources during runtime and so the system is much cheaper then one with dynamic scheduling. Because during one cycle, no deadline is missed and the cycle repeats in a static way it is easy to predict, that no deadline will be missed. So it's perfect for safety critical issues (cf. [BLMSV98]).

| Pro                                                                                                                                                  | Contra                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Very predictable</li> <li>Splitting of tasks increase<br/>feasibility of schedules</li> <li>Good for safety critical<br/>systems</li> </ul> | <ul> <li>Very high computation effort before runtime</li> <li>Splitting of tasks increases the effort even more</li> </ul> |

### 3.3.2.3 Analysis

So in fact good static algorithms are very predictable. So all deadlines will be achieved and they are mostly used in safety critical systems. Because we can guarantee that the system will not miss a deadline. Another good point is that all the computation effort is done pre-runtime and so the resulting system needs less computation resources.

A problem with static algorithms is that it is hard to implement aperiodic tasks and user interaction. The predictability of such a system is caused by the knowledge when a task arrives. If there is an aperiodic task, you do not know when it will start and so you do not know the exact deadlines pre-runtime. It is likely the same with user interactions. It would be possible to make an extra slot just for those unpredictable tasks but if you have an overload of tasks, so you can not execute all of them in time then a static system fails. Another problem I totally ignored in this article so far, is that tasks could fail. It could happen that through a programming mistake or just a bit switch, the task fails and the result of the computation is useless. To overcome these problems dynamic algorithms were created.

## 3.3.3 Dynamic scheduling

The main difference of dynamic by comparison to static scheduling is that the creation of a feasible schedule is done during runtime. That means that CPU resources are needed to create the schedule. So the chip makes continuously feasibility checks. That means extensive simulations and requires the use of heuristic functions to keep the effort acceptable. Another difference to static approaches is the use of a dynamic priority. So every task has a worst case execution time, a deadline and a priority. If there is an overload, that means that there are so many tasks that not all of them can be executed punctual, then a task with a higher priority is privileged. The concept a priority can be used in static techniques too, but in dynamic scheduling algorithm the priority can change. So it is more flexible. The problem with dynamic algorithms is that most of them are very complex and so I will only show very simple and basic ones. A more complex and efficient algorithm is described in (cf. [MM98]).

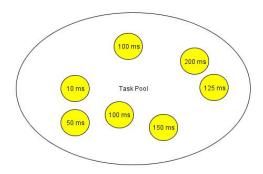

Figure 3.3: Task Pool

# 3.3.3.1 Least laxity first (LLF)/Dynamic earliest deadline first

Two basic algorithms are LLF and DEDF. They are both priority driven algorithm and their priority is calculated very simple.

LLF has the laxity as priority. Laxity is the amount of time a task can wait before starting the execution, so it will still meet its deadline. At first there is a task pool and the scheduler creates a priority queue with the task with least laxity first. Then the tasks are assigned to CPU resources one after another. If there are multiple CPUs then it is possible to execute more tasks at a time. The change of priority is pretty self explaining, because as time proceeds the laxity of all tasks decreases. If there is another task, then it will be added to the queue properly.

Figure 3.4: The resulting schedule

DEDF is pretty similar to LLF, the only difference is the priority here is just the time until the deadline arrives. That reduces the calculation effort for priority but it is almost only used in systems where all tasks have the same execution time. Because then the computation time is irrelevant for the priority (cf. [BLMSV98]).

#### 3.3.3.2 The problem with overloads

I already mentioned in the introduction to dynamic algorithm, that an overload is when there are so many tasks that some of then cannot be executed in time. Then the algorithm has to differ between tasks that are worth to execute and those that can be discarded and execute later. That means that safety critical tasks like opening an airbag has a high value and controlling the air conditioner for example has a low value. Or the length of the execution time reduces

value, or soft real time constraints reduce value, while hard deadlines increase it (cf. [BLMSV98]).

#### 3.3.3.3 Fault tolerance

Another big advantage of dynamic systems is that they are fault tolerant. It could happen that through a simple bit switch or a programming bug, the task fails and the result is useless. The key idea behind fault tolerant systems is that you have two tasks, to solve the same problem

**Primary task** This task is scheduled that it will meet the soft deadline of the task or so that a secondary task can be executed before the hard deadline arrives. This task is normally sufficient.

**Secondary task** This task is like a backup, it is scheduled directly after the primary task. This task is only executed if the primary task fails.

That means that if no error occurs the secondary task is discarded and if there is an error then the second task solves the problem in time. It is also possible to use more then one backup task. But this means that there is a huge waste of resources, because if the secondary task is discarded in most cases then this time is lost for other task. To solve this problem it seems logical to use resource reclaiming too (cf. [BLMSV98]).

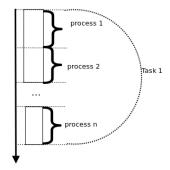

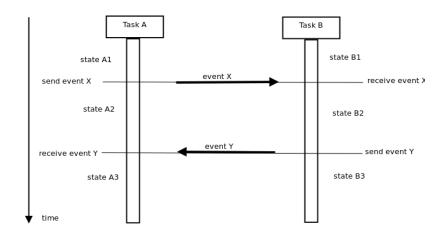

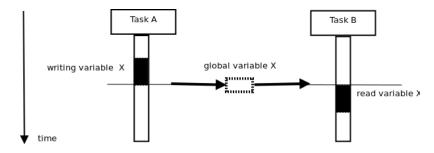

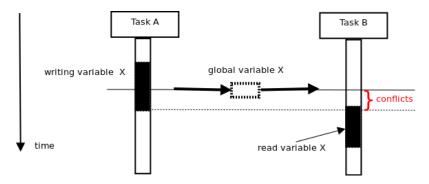

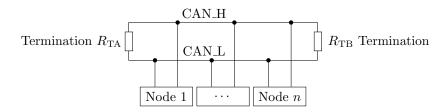

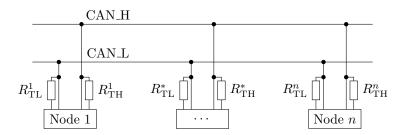

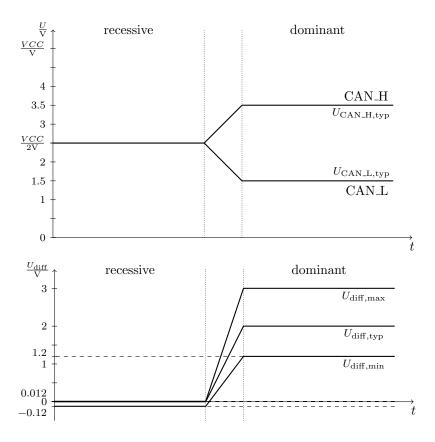

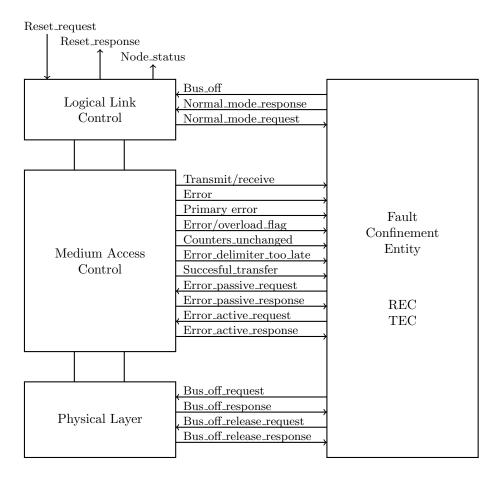

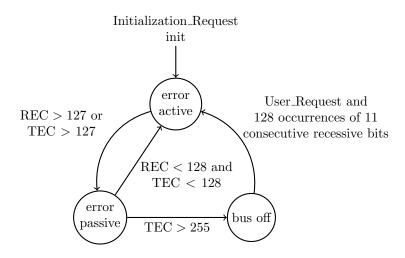

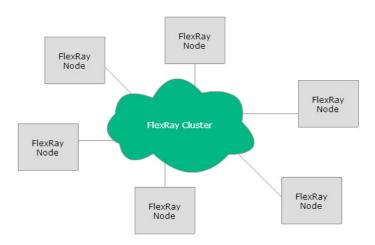

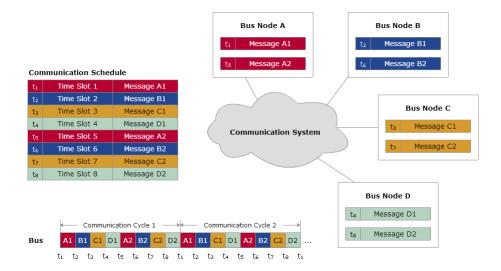

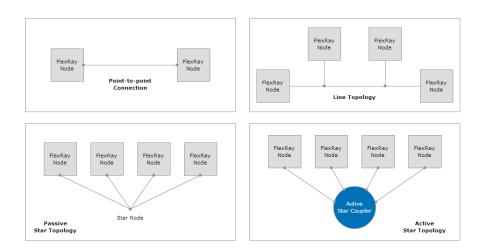

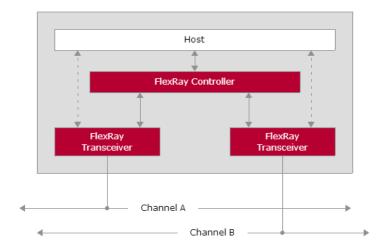

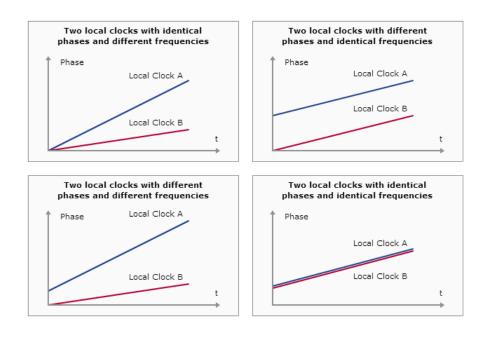

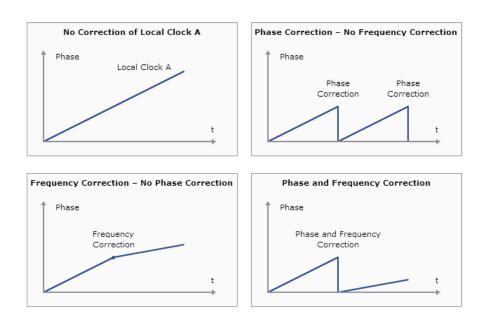

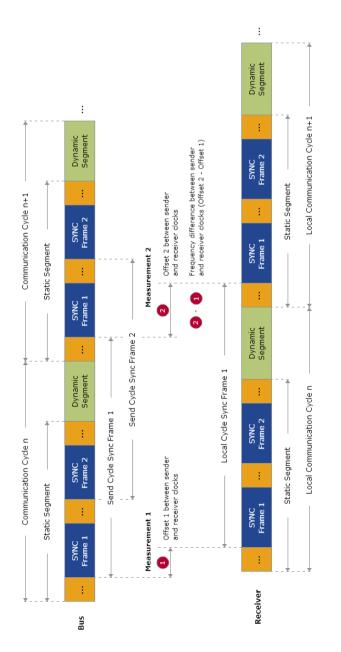

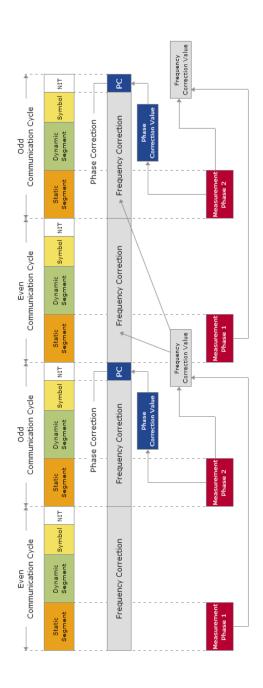

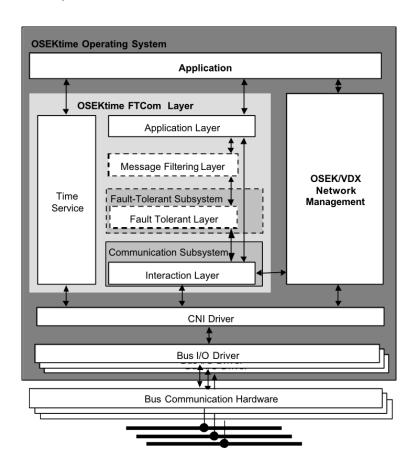

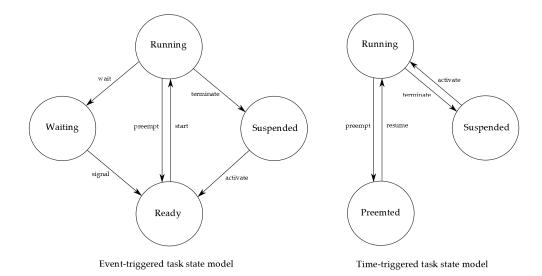

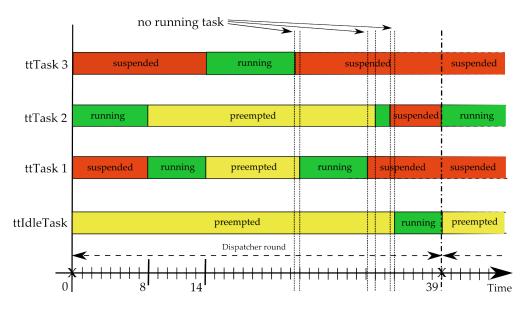

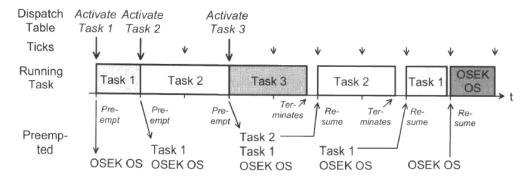

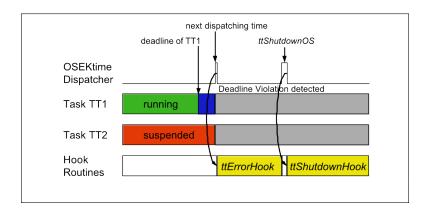

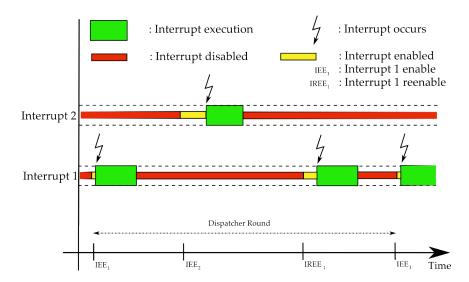

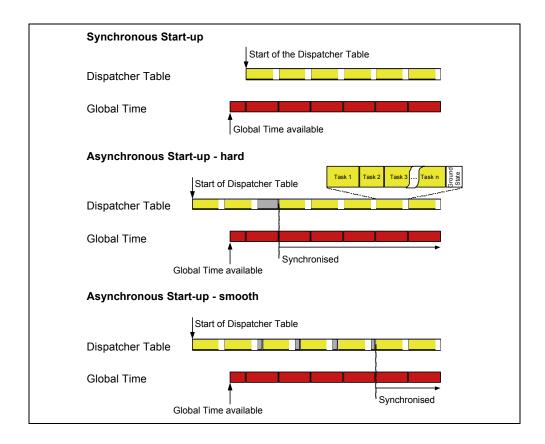

#### 3.3.3.4 Resource reclaiming