# TECHNISCHE UNIVERSITÄT MÜNCHEN

### Lehrstuhl für Rechnertechnik und Rechnerorganisation / Parallelrechnerarchitektur

### Advanced Optimization Techniques for Sparse Grids on Modern Heterogeneous Systems

Alin Florindor Muraraşu

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. M. Bichler

Prüfer der Dissertation:

1. Univ.-Prof. Dr. A. Bode

2. Univ.-Prof. Dr. H.-J. Bungartz

Die Dissertation wurde am 25.03.2013 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 25.05.2013 angenommen.

### Abstract

GPU accelerated systems are heterogeneous systems characterized by a peak performance in the order of TFlop/s obtained using a large number of cores and wide vector units. Moreover, GPUs provide an advantageous ratio between performance and power consumption. However, reaching high efficiency on GPUs is often a difficult task whose successful completion requires advanced optimization techniques. In order to fit an application to GPUs, redesigning data structures and algorithms is often necessary so that they consume less memory and become more vector friendly. For extra performance, an empirical optimization method is required in order to cope with non-trivial interactions between optimization parameters characteristic to GPU programs. On heterogeneous systems, another key problem is the distribution of the computational work among the different processors. This thesis proposes solutions to these challenges in the context of the sparse grid technique, a numerical technique that addresses the curse of dimensionality problem arising in high-dimensional settings such as computational steering. The performance results presented here validate a set of advanced optimization techniques that allow for efficiently porting sparse grid algorithms to GPUs, for improving the performance using an empirical optimization method, and for increasing the utilization of the system using load balancing.

### Acknowledgements

Many people contributed to the success of this work. First of all, I would like to thank my Doktorvater, Prof. Dr. Arndt Bode, for his help, advice, and especially for offering me the chance to work in a very supportive research environment at the Lehrstuhl für Rechnertechnik and Rechnerorganisation (LRR). I would like to thank my mentor, Josef Weidendorfer, for his help not only on the technical side but on all research related aspects. I am thankful to all the members of LRR (too many to be named individually) who contributed to a four year experience that made me a better researcher and more importantly a better person.

I would like to thank my collaborators from Prof. Dr. Hans Bungartz's group, Gerrit Buse, Dirk Pflüger, Daniel Butnaru, Tobias Weinzierl, people on whose help I could always count. I learned a lot from them and for this I will always be grateful.

Last but not least, I am very thankful to my family, Georgiana, Lenuţa, Oana, and Florin, for providing me with the comfort necessary to complete this four year effort.

## Contents

| Α            | Abstract III       |                                         |           |

|--------------|--------------------|-----------------------------------------|-----------|

| $\mathbf{A}$ | Acknowledgements V |                                         |           |

| 1            | Intr               | roduction                               | 1         |

|              | 1.1                | Motivation                              | 1         |

|              | 1.2                | Scientific Contribution                 | 4         |

|              | 1.3                | The Structure of the Thesis             | 6         |

| <b>2</b>     | AC                 | Complex Hardware and Software Landscape | 9         |

|              | 2.1                | The Power Wall and the ILP Wall         | 9         |

|              | 2.2                | Accelerators                            | 11        |

|              |                    | 2.2.1 General View                      | 12        |

|              |                    | 2.2.2 A Closer Look at GPUs             | 13        |

|              |                    | 2.2.3 Trends                            | 14        |

|              | 2.3                | Programming Models                      | 15        |

|              |                    | 2.3.1 The OpenMP Programming Model      | 15        |

|              |                    | 2.3.2 The CUDA Programming Model        | 17        |

|              |                    | 2.3.3 The OpenCL Programming Model      | 19        |

|              | 2.4                | Examples of GPU Applications            | 20        |

|              | 2.5                | Challenges                              | 22        |

|              | 2.6                | Summary                                 | 24        |

| 3            | Cor                | mputational Steering Using Sparse Grids | <b>25</b> |

|              | 3.1                | A Computational Steering Scenario       | 25        |

|              | 3.2                | Related Work                            | 27        |

|              | 3.3                | The Sparse Grid Technique               | 28        |

|              |                    | 3.3.1 The Construction of Sparse Grids  | 28        |

|   |                          | 3.3.2                                                                                                                | Computing the Hierarchical Coefficients                                                                                     | 31                                                                                                                                             |

|---|--------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                          | 3.3.3                                                                                                                | Evaluating the Sparse Grid Approximation                                                                                    | 32                                                                                                                                             |

|   | 3.4                      | Tradit                                                                                                               | ional Data Structures for Sparse Grids                                                                                      | 33                                                                                                                                             |

|   | 3.5                      | A Me                                                                                                                 | mory Efficient Data Structure                                                                                               | 34                                                                                                                                             |

|   |                          | 3.5.1                                                                                                                | The $gp2idx$ Bijective Mapping $\ldots \ldots \ldots$ | 35                                                                                                                                             |

|   |                          | 3.5.2                                                                                                                | Dynamic Programming Algorithms                                                                                              | 37                                                                                                                                             |

|   |                          | 3.5.3                                                                                                                | Extension for Non-zero Boundary Sparse Grids                                                                                | 39                                                                                                                                             |

|   |                          | 3.5.4                                                                                                                | The Case of Regular Sparse Grids                                                                                            | 40                                                                                                                                             |

|   | 3.6                      | Non-re                                                                                                               | ecursive Sparse Grid Algorithms                                                                                             | 40                                                                                                                                             |

|   |                          | 3.6.1                                                                                                                | Non-recursive Hierarchization                                                                                               | 41                                                                                                                                             |

|   |                          | 3.6.2                                                                                                                | Non-recursive Interpolation                                                                                                 | 42                                                                                                                                             |

|   | 3.7                      | fastsg,                                                                                                              | a Lightweight Sparse Grid Library                                                                                           | 43                                                                                                                                             |

|   | 3.8                      | Specia                                                                                                               | l Features of fastsg                                                                                                        | 45                                                                                                                                             |

|   |                          | 3.8.1                                                                                                                | Input Specialized Algorithms for Interpolation                                                                              | 45                                                                                                                                             |

|   |                          | 3.8.2                                                                                                                | Sparse Grids of Vectors                                                                                                     | 49                                                                                                                                             |

|   | 3.9                      | Repre                                                                                                                | sentative Computational Kernels                                                                                             | 50                                                                                                                                             |

|   | 3.10                     | Summ                                                                                                                 | ary                                                                                                                         | 50                                                                                                                                             |

|   |                          |                                                                                                                      |                                                                                                                             |                                                                                                                                                |

| 4 | Spa                      | rse Gr                                                                                                               | ids on Heterogeneous Systems                                                                                                | 53                                                                                                                                             |

| 4 | -                        |                                                                                                                      | ids on Heterogeneous Systems                                                                                                | <b>53</b><br>53                                                                                                                                |

| 4 | <b>Spa</b><br>4.1<br>4.2 | Introd                                                                                                               | luction                                                                                                                     | 53                                                                                                                                             |

| 4 | 4.1                      | Introd<br>Relate                                                                                                     | ed work                                                                                                                     |                                                                                                                                                |

| 4 | 4.1<br>4.2               | Introd<br>Relate                                                                                                     | uction                                                                                                                      | 53<br>55                                                                                                                                       |

| 4 | 4.1<br>4.2               | Introd<br>Relate<br>Optim                                                                                            | Juction                                                                                                                     | 53<br>55<br>56<br>56                                                                                                                           |

| 4 | 4.1<br>4.2               | Introd<br>Relate<br>Optim<br>4.3.1                                                                                   | uction                                                                                                                      | 53<br>55<br>56                                                                                                                                 |

| 4 | 4.1<br>4.2               | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3                                                                 | auction                                                                                                                     | 53<br>55<br>56<br>56<br>61                                                                                                                     |

| 4 | 4.1<br>4.2<br>4.3        | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3                                                                 | Juction                                                                                                                     | 53<br>55<br>56<br>61<br>63                                                                                                                     |

| 4 | 4.1<br>4.2<br>4.3        | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim                                                        | Juction                                                                                                                     | 53<br>55<br>56<br>61<br>63<br>65                                                                                                               |

| 4 | 4.1<br>4.2<br>4.3        | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1                                               | Juction                                                                                                                     | <ol> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>65</li> </ol>                                                 |

| 4 | 4.1<br>4.2<br>4.3        | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1<br>4.4.2<br>4.4.3                             | Juction                                                                                                                     | <ul> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>65</li> <li>66</li> </ul>                                     |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1<br>4.4.2<br>4.4.3                             | Juction                                                                                                                     | <ul> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>66</li> <li>68</li> </ul>                                     |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1<br>4.4.2<br>4.4.3<br>Evalua                   | auction                                                                                                                     | <ul> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>66</li> <li>68</li> <li>69</li> </ul>                         |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1<br>4.4.2<br>4.4.3<br>Evalua<br>4.5.1          | Juction                                                                                                                     | <ul> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>69</li> </ul>             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introd<br>Relate<br>Optim<br>4.3.1<br>4.3.2<br>4.3.3<br>Optim<br>4.4.1<br>4.4.2<br>4.4.3<br>Evalua<br>4.5.1<br>4.5.2 | Juction                                                                                                                     | <ul> <li>53</li> <li>55</li> <li>56</li> <li>61</li> <li>63</li> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>69</li> <li>69</li> </ul> |

| <b>5</b> | An                                            | Empirical Optimization Method for GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75                                                                                                                                                                                  |

|----------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75                                                                                                                                                                                  |

|          | 5.2                                           | Existing Approaches for Auto-tuning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                                                                                                                                                  |

|          | 5.3                                           | Auto-tuning Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                                                                                                                                                  |

|          |                                               | 5.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79                                                                                                                                                                                  |

|          |                                               | 5.3.2 Search Space Pruning Using Partitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79                                                                                                                                                                                  |

|          |                                               | 5.3.3 Representative Execution Sampling by Reducing Input Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                                                                                  |

|          | 5.4                                           | Auto-tuning of GPU Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81                                                                                                                                                                                  |

|          |                                               | 5.4.1 Input Reduction for GPU Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                                                                                                                                                                                  |

|          |                                               | 5.4.2 Optimization Parameters for GPU Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87                                                                                                                                                                                  |

|          | 5.5                                           | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91                                                                                                                                                                                  |

|          |                                               | 5.5.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91                                                                                                                                                                                  |

|          |                                               | 5.5.2 Sparse Grid Interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                                                                                                                                  |

|          |                                               | 5.5.3 Sparse Vector - Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                                                                                                                                                 |

|          | 5.6                                           | Other Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104                                                                                                                                                                                 |

|          | 5.7                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105                                                                                                                                                                                 |

| 6        | Loa                                           | d Balancing on Heterogeneous Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 107                                                                                                                                                                                 |

|          | 6.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107                                                                                                                                                                                 |

|          |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -01                                                                                                                                                                                 |

|          | 6.2                                           | Existing Load Balancing Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                     |

|          | $6.2 \\ 6.3$                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109                                                                                                                                                                                 |

|          |                                               | Existing Load Balancing Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109<br>110                                                                                                                                                                          |

|          |                                               | Existing Load Balancing Solutions    1      Considerations    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109<br>110<br>110                                                                                                                                                                   |

|          |                                               | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109<br>110<br>110<br>111                                                                                                                                                            |

|          | 6.3                                           | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1                                                                                                                                                                                                                                                                                                                                                                                            | 109<br>110<br>110<br>111<br>111                                                                                                                                                     |

|          | 6.3                                           | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1                                                                                                                                                                                                                                                                                                                            | 109<br>110<br>110<br>111<br>113<br>113                                                                                                                                              |

|          | 6.3                                           | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1         6.4.1       Dynamic Task Based Scheduling       1                                                                                                                                                                                                                                                                  | 109<br>110<br>111<br>111<br>113<br>113<br>115                                                                                                                                       |

|          | 6.3                                           | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1         6.4.1       Dynamic Task Based Scheduling       1         6.4.2       Scheduling Deterministic Tasks       1                                                                                                                                                                                                       | 109<br>110<br>111<br>113<br>113<br>113<br>115<br>116                                                                                                                                |

|          | <ul><li>6.3</li><li>6.4</li></ul>             | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1         6.4.1       Dynamic Task Based Scheduling       1         6.4.2       Scheduling Deterministic Tasks       1         6.4.3       The Grain Size Problem       1                                                                                                                                                    | 109<br>110<br>1110<br>1111<br>113<br>113<br>115<br>116<br>118                                                                                                                       |

|          | <ul><li>6.3</li><li>6.4</li></ul>             | Existing Load Balancing Solutions       1         Considerations       1         6.3.1 Multi-versioning       1         6.3.2 Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1         6.4.1 Dynamic Task Based Scheduling       1         6.4.2 Scheduling Deterministic Tasks       1         6.4.3 The Grain Size Problem       1         Scheduling Data Parallelism on GPU Based Systems       1                                                                                                                 | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>118</li> </ol>                                                     |

|          | <ul><li>6.3</li><li>6.4</li></ul>             | Existing Load Balancing Solutions       1         Considerations       1         6.3.1       Multi-versioning       1         6.3.2       Assigning Work to Processors: to-one and to-all       1         Task Based Scheduling for Heterogeneous Systems       1         6.4.1       Dynamic Task Based Scheduling       1         6.4.2       Scheduling Deterministic Tasks       1         6.4.3       The Grain Size Problem       1         Scheduling Data Parallelism on GPU Based Systems       1         6.5.1       Heterogeneous Dynamic Scheduling for Data Parallelism       1 | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>118</li> <li>120</li> </ol>                                        |

|          | <ul><li>6.3</li><li>6.4</li></ul>             | Existing Load Balancing Solutions1Considerations16.3.1 Multi-versioning16.3.2 Assigning Work to Processors: to-one and to-all1Task Based Scheduling for Heterogeneous Systems16.4.1 Dynamic Task Based Scheduling16.4.2 Scheduling Deterministic Tasks16.4.3 The Grain Size Problem1Scheduling Data Parallelism on GPU Based Systems16.5.1 Heterogeneous Static Scheduling for Data Parallelism16.5.2 Heterogeneous Static Scheduling for Data Parallelism1                                                                                                                                  | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>118</li> <li>120</li> <li>123</li> </ol>                           |

|          | <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Existing Load Balancing Solutions1Considerations16.3.1 Multi-versioning16.3.2 Assigning Work to Processors: to-one and to-all1Task Based Scheduling for Heterogeneous Systems16.4.1 Dynamic Task Based Scheduling16.4.2 Scheduling Deterministic Tasks16.4.3 The Grain Size Problem1Scheduling Data Parallelism on GPU Based Systems16.5.1 Heterogeneous Static Scheduling for Data Parallelism16.5.3 Comparison1                                                                                                                                                                            | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>1120</li> <li>123</li> <li>124</li> </ol>                          |

|          | <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Existing Load Balancing Solutions1Considerations16.3.1 Multi-versioning16.3.2 Assigning Work to Processors: to-one and to-all1Task Based Scheduling for Heterogeneous Systems16.4.1 Dynamic Task Based Scheduling16.4.2 Scheduling Deterministic Tasks16.4.3 The Grain Size Problem1Scheduling Data Parallelism on GPU Based Systems16.5.1 Heterogeneous Static Scheduling for Data Parallelism16.5.3 Comparison1Evaluation1                                                                                                                                                                 | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>120</li> <li>123</li> <li>124</li> <li>124</li> </ol>              |

|          | <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Existing Load Balancing Solutions1Considerations16.3.1 Multi-versioning16.3.2 Assigning Work to Processors: to-one and to-all1Task Based Scheduling for Heterogeneous Systems16.4.1 Dynamic Task Based Scheduling16.4.2 Scheduling Deterministic Tasks16.4.3 The Grain Size Problem1Scheduling Data Parallelism on GPU Based Systems16.5.1 Heterogeneous Static Scheduling for Data Parallelism16.5.3 Comparison16.6.1 Experimental Setup1                                                                                                                                                   | <ol> <li>109</li> <li>110</li> <li>111</li> <li>113</li> <li>113</li> <li>115</li> <li>116</li> <li>118</li> <li>120</li> <li>123</li> <li>124</li> <li>124</li> <li>125</li> </ol> |

|    | 6.7   | Other Examples                                                                                                                                    |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 6.8   | Summary                                                                                                                                           |

| 7  | Con   | clusion and Future Work 13                                                                                                                        |

|    | 7.1   | Sparse Grids on Heterogeneous Systems                                                                                                             |

|    | 7.2   | Optimization Strategy                                                                                                                             |

|    | 7.3   | Summary of Performance Results                                                                                                                    |

|    | 7.4   | Future Work                                                                                                                                       |

|    |       | 7.4.1 Optimization Techniques $\dots \dots \dots$ |

|    |       | 7.4.2 Enhanced Sparse Grid Functionality                                                                                                          |

| Bi | bliog | raphy 143                                                                                                                                         |

## List of Tables

| 3.1 | Triple-layer interface exposed by <i>fastsg</i> . Only the most important routines are                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | shown                                                                                                                                                                              |

| 5.1 | CUDA parameters with descriptions and default values for an Nvidia Fermi GPU. 84                                                                                                   |

| 5.2 | Best values for $bs$ and $pt$ resulting from auto-tuning. The best value found for                                                                                                 |

|     | wu is $n$ . The same values are obtained on both sysA and sysB                                                                                                                     |

| 5.3 | Speedup of auto-tuning optimizations relative to auto-tuning time                                                                                                                  |

| 5.4 | The best values for $bs$ and $pt$ resulting from auto-tuning on sysA and sysB. The                                                                                                 |

|     | best value for $wu$ is $n$ on both systems. $\ldots \ldots \ldots$ |

| 5.5 | Impact of auto-tuning optimizations on auto-tuning time. Speedup is here rela-                                                                                                     |

|     | tive to the duration of auto-tuning without optimizations                                                                                                                          |

| 6.1 | The best grain sizes for the GPU version of $sginterp$ for different values of $d$ 129                                                                                             |

# List of Figures

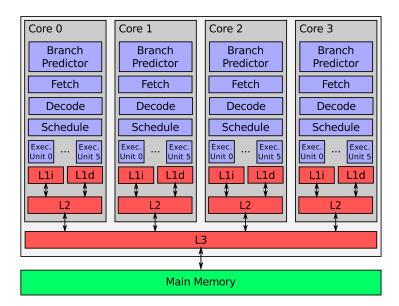

| 2.1 | Simplified view on the architecture of a 4-core Nehalem CPU. The cache hierarchy                                          |    |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

|     | has 3 levels: L1 (64 KB), L2 (256 KB), and L3 (8 MB). The branch predictor                                                |    |

|     | provides speculative execution. The out-of-order engine includes the schedule                                             |    |

|     | unit and 6 different execution units.                                                                                     | 11 |

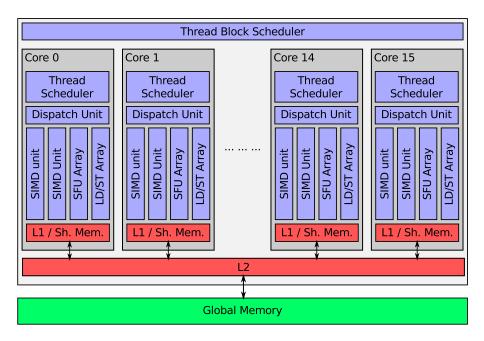

| 2.2 | Simplified architecture of a 16-core Nvidia Fermi GPU. The GPU contains a                                                 |    |

|     | fully coherent 2-level cache hierarchy: L1 (16 or 48 KB) and L2 (768 KB). The                                             |    |

|     | SIMD units contain 16 lanes each. The thread block scheduler assigns thread                                               |    |

|     | blocks, e.g. groups of 256 threads, to cores. The thread scheduler interleaves the                                        |    |

|     | execution of thread warps, i.e. groups of 32 threads.                                                                     | 13 |

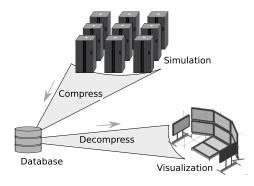

| 3.1 | Main computational steering scenario. Compressed simulation data is stored in                                             |    |

|     | a database. Data is then decompressed in real-time for visualization                                                      | 26 |

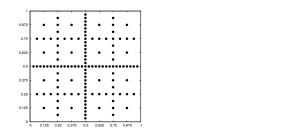

| 3.2 | 2d zero boundary sparse grids.                                                                                            | 29 |

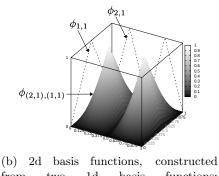

| 3.3 | Hierarchical basis functions                                                                                              | 30 |

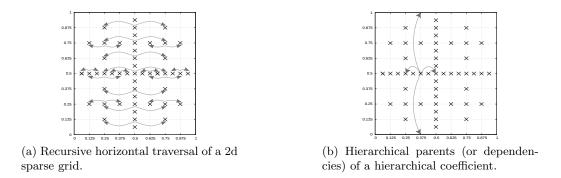

| 3.4 | Traversal and data dependencies in 2d sparse grid hierarchization. $\ldots$ $\ldots$ $\ldots$                             | 32 |

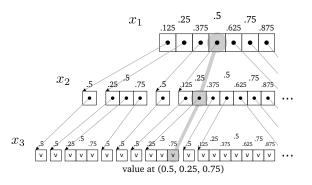

| 3.5 | The trie data structure for a 3d sparse grid of level 3. The grid points are                                              |    |

|     | represented using coordinates. The arrays are linearized binary trees. Each level                                         |    |

|     | of the tree corresponds to one dimension. The access to the grid point given by                                           |    |

|     | $\underline{l} = (1, 2, 2)$ and $\underline{i} = (1, 1, 3)$ or equivalent coordinates $(0.5, 0.25, 0.75)$ is highlighted. | 34 |

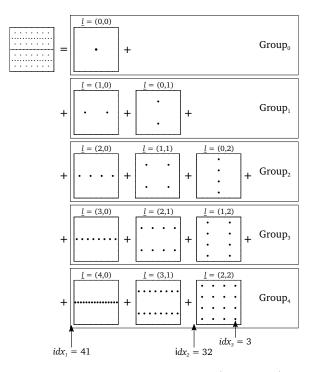

| 3.6 | Decomposition of a 2d truncated sparse grid (Fig. $3.2b$ ) into <i>block</i> structures.                                  |    |

|     | The point (0.875, 0.125) corresponding to $\underline{l} = (2, 2)$ and $\underline{i} = (7, 1)$ maps to index             |    |

|     | 76 (= $41 + 32 + 3$ ) in the linear representation of the sparse grid                                                     | 36 |

| 3.7 | 3d sparse grid with non-zero boundary. The boundary of a 3d sparse grid is                                                |    |

|     | composed of lower-dimensional sparse grids with zero boundary                                                             | 39 |

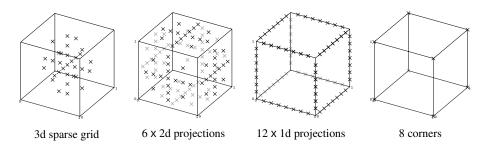

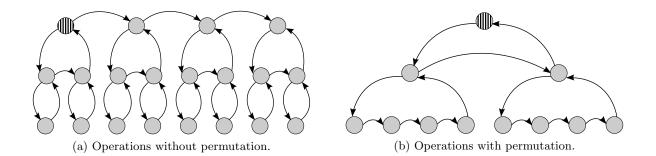

| 3.8 | The positive effect of permutation on computing the Cartesian product                                                     | 49 |

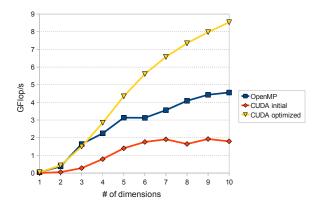

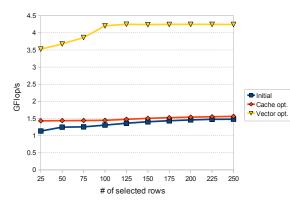

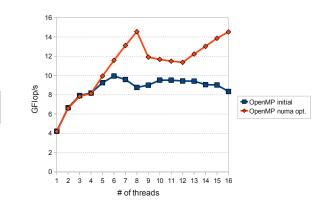

| 4.1 | Performance of sparse grid hierarchization, <i>sghierarch</i> , on a heterogeneous system.                                | 70 |

| 4.2 | Performance of sparse grid interpolation, <i>sginterp</i> , on a heterogeneous system                                     | 72 |

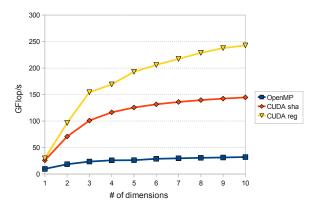

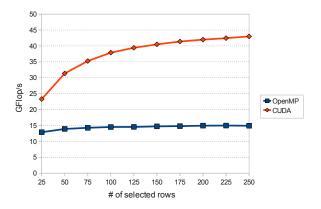

| 4.3  | Performance of <i>spvm</i> on a heterogeneous system                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

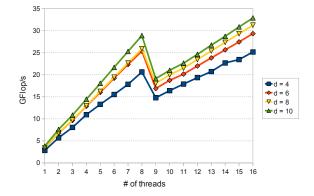

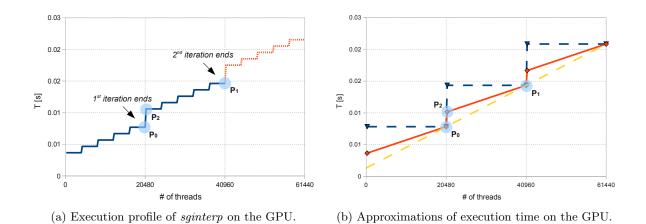

| 5.1  | Execution profile of <i>sginterp</i> for different number of threads                                                                                                 |

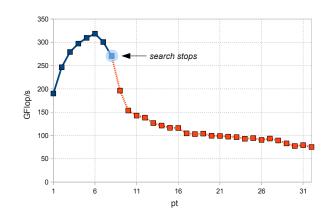

| 5.2  | Search algorithm. It stops when two successive values for $pt$ decrease the perfor-                                                                                  |

| 5.3  | mance                                                                                                                                                                |

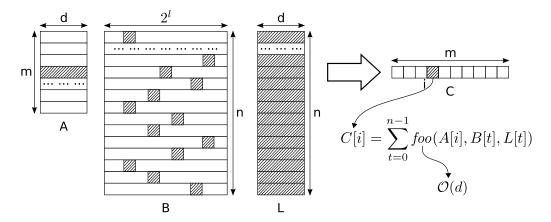

|      | matrices A, B, and L. foo is $\mathcal{O}(d)$ and accesses one value from a B's row and                                                                              |

| 5.4  | one row from $L$                                                                                                                                                     |

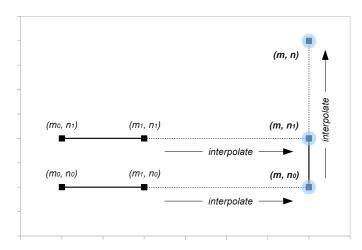

|      | $(m_0, n_1), (m_1, n_0), \text{ and } (m_1, n_1).$                                                                                                                   |

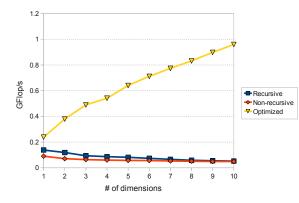

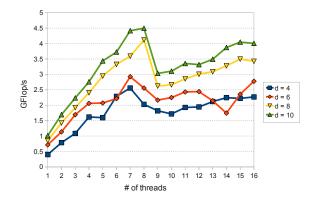

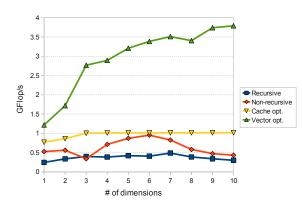

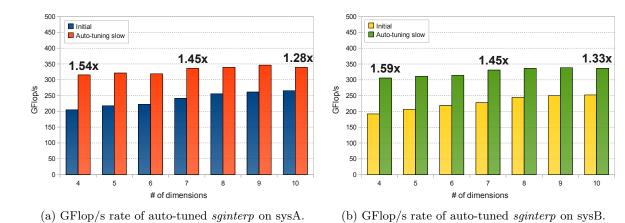

| 5.5  | Performance of <i>sginterp</i> after auto-tuning on sysA and sysB                                                                                                    |

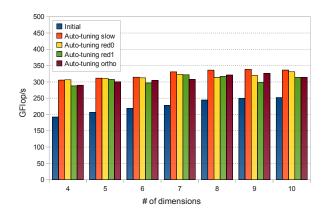

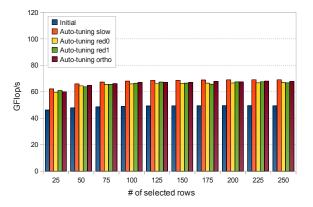

| 5.6  | Impact of auto-tuning optimizations on the performance of <i>sginterp</i> on sysA 99                                                                                 |

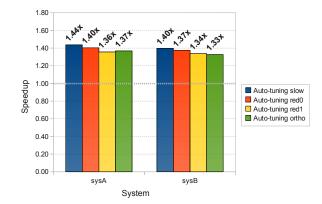

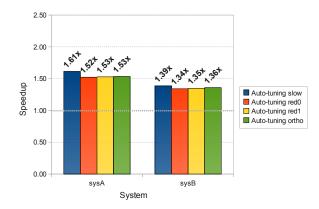

| 5.7  | Impact of the optimizations on auto-tuning on sysA and sysB. The speedup is calculated relative to the GFlop/s rate measured for the initial <i>sginterp</i> without |

|      | auto-tuning                                                                                                                                                          |

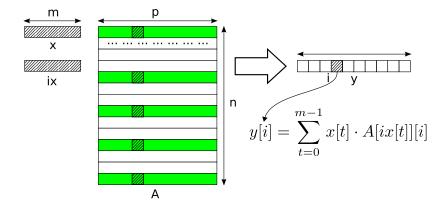

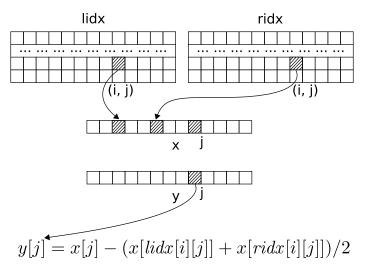

| 5.8  | Computation done in <i>spvm</i> . It shows how the output vector $y$ results from $x$ and                                                                            |

|      | A. Only the green rows are used and are selected through the integer vector $ix$ . 101                                                                               |

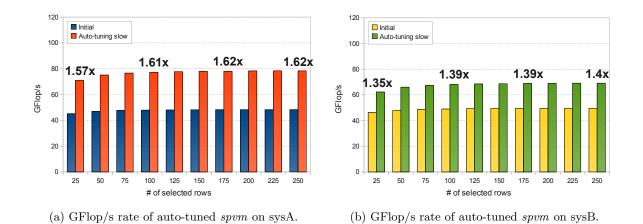

| 5.9  | Performance of auto-tuned version of <i>spvm</i>                                                                                                                     |

| 5.10 | Impact of auto-tuning optimizations on the performance of $spvm$ on sysA 103                                                                                         |

| 5.11 | Impact of auto-tuning optimizations on performance. The speedup is relative to                                                                                       |

|      | the GFlop/s rate                                                                                                                                                     |

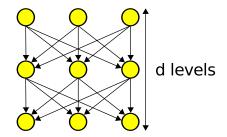

| 6.1  | Simplification of <i>sghierarch</i> . It shows how the vector $y$ is computed in iteration                                                                           |

|      | i, where $i$ is from 1 to $d$ . The marked components are used for the calculation of                                                                                |

|      | y[j]                                                                                                                                                                 |

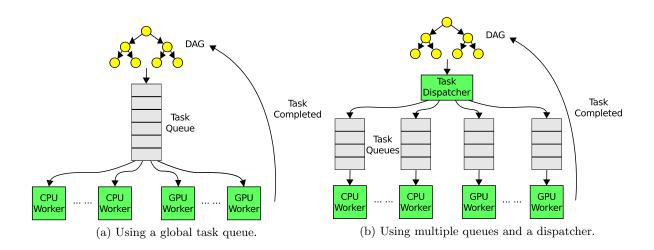

| 6.2  | Dynamic load balancing schemes                                                                                                                                       |

| 6.3  | The constraints influencing the selection of the optimal grain size. $\ldots$ $\ldots$ $117$                                                                         |

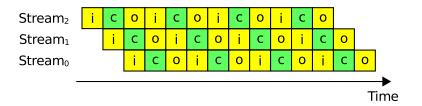

| 6.4  | The benefits of using 3 streams in the GPU worker thread. $i\ /\ o$ means data                                                                                       |

|      | copy to / from the GPU. $c$ refers to computation done by the GPU. $\ldots$ 121                                                                                      |

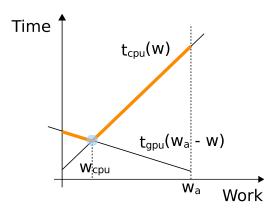

| 6.5  | Static load balancing resulting from the intersection of two linear functions 122 $$                                                                                 |

| 6.6  | The dependency task graph for <i>sghierarch</i>                                                                                                                      |

| 6.7  | The to-one map for sghierarch. It contains the ratio between the GFlop/s on                                                                                          |

|      | GPU and on CPU. For the highlighted cells, the GPU is at least $0.95x$ slower                                                                                        |

|      | than the CPU                                                                                                                                                         |

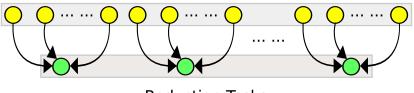

| 6.8  | The task graph for $\mathit{sginterp}.$ This decomposition is also applicable to $\mathit{spvm}.$ 126                                                                |

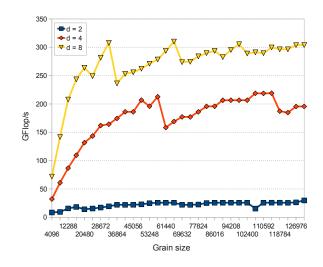

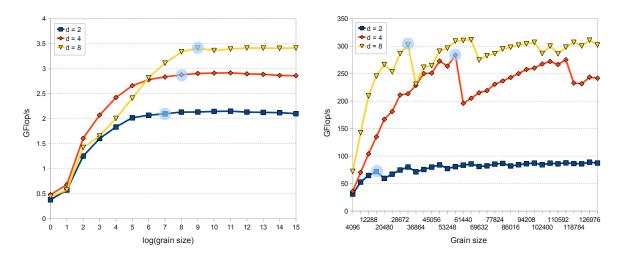

| 6.9  | GFlop/s rate obained using StarPU as a function of grain size                                                                                                        |

| 6.10 | GFlop/s rate as a function of grain size                                             |

|------|--------------------------------------------------------------------------------------|

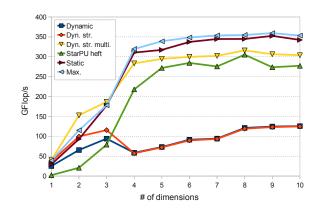

| 6.11 | Load balancing of <i>sginterp</i>                                                    |

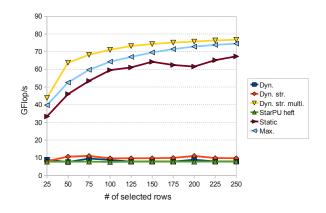

| 6.12 | Load balancing of <i>spvm</i>                                                        |

|      |                                                                                      |

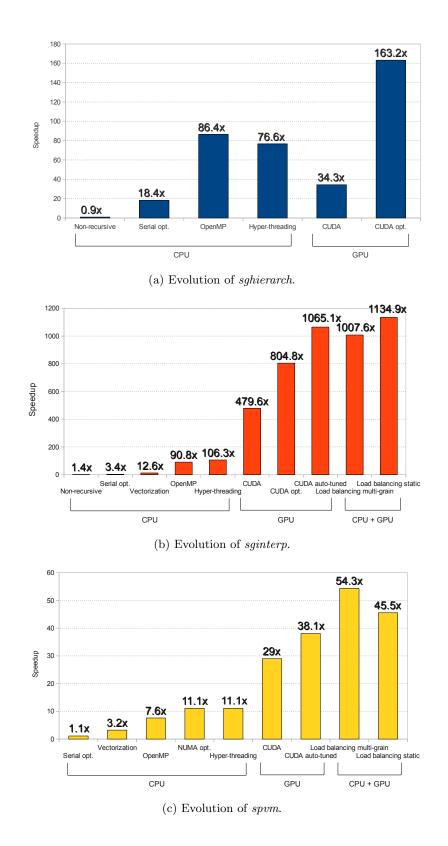

| 7.1  | Impact of optimizations on the performance of the sparse grid kernels. The           |

|      | speedup numbers are computed relative to the initial serial versions of the kernels. |

|      | Tested system: dual-socket, 4 cores / socket, multithreaded Intel Nehalem (CPU),     |

|      | Nvidia Quadro 6000 (GPU)                                                             |

### Chapter 1

## Introduction

This chapter presents the motivation for the use of Graphics Processing Unit (GPU) based heterogeneous systems for accelerating parallel applications. An overview of the advanced optimization techniques proposed in this thesis is provided, including an empirical optimization method and load balancing. The chapter introduces the application used for validating the optimizations, namely a computational steering application in which high-dimensional simulation data is efficiently handled using the sparse grid technique. At the end of the chapter, the contributions of the thesis are summarized and the structure of the thesis is presented.

### 1.1 Motivation

Heterogeneous systems are very popular nowadays because they allow for higher processing speeds to be achieved without sacrificing power efficiency. Their main disadvantage is that heterogeneous systems are difficult to program efficiently. Often, advanced optimization techniques are required in order to achieve a high level of performance. Such techniques are proposed in this thesis and are validated using routines critical for the performance of a computational steering application. Since this application deals with high-dimensional simulation data that needs to be visualized in real-time, the main requirement is to fully exploit the computational power of GPU based heterogeneous systems. The thesis has two main directions: The first refers to understanding and addressing some of the most important challenges of heterogeneous computing, while the second is more application specific as it refers to the computational steering application which has to be parallelized and optimized for modern hardware.

Faced with the power wall, processor architects adopted the multi-core solution in which the computational speed of the hardware increases by replicating the execution engines (cores) within a CPU. This allows for the power consumption to remain at an acceptable level. However, the trade-off is that programmers now have to parallelize their applications. Even more performance and a higher Flop/s (Floating Point Operations per Second) / Watt ratio can be obtained using general purpose accelerators, e.g. GPUs, which can generally be described as many-core processors containing a set of so-called wimpy cores, i.e. simple in-order execution engines that do not include speculative logic for branch prediction, cache prefetching, etc. A notable property of accelerators is that they cannot operate independently from CPUs whose main responsibility in this context is to offload tasks to accelerators. Often, the transistor budget of accelerators is allocated to wide vector units. Multithreading is a rather inexpensive technique which can provide accelerators with the means to hide the latency of the instruction pipeline by interleaving the execution of a large number of threads per core. Given their large number of cores and wide vector units, accelerators are not suitable for all classes of applications, especially for those that are not vectorizable or do not contain enough data parallelism. Nevertheless, there are many applications from computer graphics and scientific computing that harness the strengths of accelerators, thus explaining their success.

Nowadays, a typical heterogeneous system contains CPUs and GPUs. CPUs can be seen as latency oriented processors [1] in the sense that they are optimized for efficiently executing a serial stream of instructions. They incorporate large caches and implement techniques for branch prediction and data prefetching. Additionally, CPUs contain complex logic (out-of-order) for automatically extracting the Instruction Level Parallelism (ILP) from a sequence of instructions. In contrast to CPUs, GPUs are throughput oriented [1] or massively parallel processors, making them a perfect fit for data parallel computations. In terms of peak performance, GPUs are generally up to two orders of magnitude faster than one CPU core. GPUs typically contain more cores than CPUs, have wider vector units, and operate at a lower clock frequency. A GPU has its dedicated memory which has approximately one order of magnitude more bandwidth than the memory of the CPU but its size is rather small, e.g. up to 6 GB. The GPU memory is separated from the CPU memory by a PCI Express (PCIe) bus whose bandwidth is lower than the bandwidth of both the CPU memory and the GPU memory. In this respect, a GPU based heterogeneous system can be considered a distributed memory system.

Understanding the challenges of GPUs is of high importance when porting applications to GPUs. Most importantly, their vector nature imposes restrictions on applications. Vector based architectures are characterized by the fact that the same operation is executed simultaneously on multiple chunks of data, a processing model referred to as Single Instruction Multiple Data (SIMD). Such an execution puts constraints on the placement of the data in memory, i.e. the data must be aligned and the chunks must be consecutive words in memory. Moreover, the control flow is another crucial element determining the efficiency of a vector processor. In the presence of branches, undesired situations might occur in which different operations must be executed on different data chunks. However, this violates the SIMD requirements and cannot be executed at once by a vector unit, meaning that the different vector operations are serialized and during the execution of each operation, only a subset of the lanes of the vector unit is actually utilized. In such a scenario, the obtained performance is suboptimal. From here, one can imagine that complex data structures and recursive algorithms that are control flow dependent, cannot be paired efficiently with GPUs. Therefore, it is essential to analyze whether such data structures and algorithms can be replaced with more GPU friendly versions.

Memory consumption can also become a challenge on a GPU taking into account that the GPU memory is a scarce resource. Thus, it is important that the data structures copied to the GPU have a small memory footprint. Although the GPU memory is faster than the CPU memory, the PCIe bus acts as a severe performance bottleneck for applications characterized by a low ratio between GPU computation and PCIe communication.

Most GPU programs expose parameters whose values control the optimizations applied to the code or influence the performance behavior, e.g. parameters that control multithreading, locality, and parallelism granularity. The objective is to find the values for the optimization parameters that maximize the performance. However, complex interactions between parameters cannot be addressed effectively using theoretical methods, e.g. performance models. In this context, an empirical optimization method, or search based auto-tuning, tries to find the optimal values for the parameters by evaluating the performance for different combinations of values assigned to the optimization parameters. In the absence of auto-tuning, a programmer is often required to fully understand non-trivial characteristics of the GPU in order to determine the best values of the parameters. Furthermore, hardware details are not always available. The alternative is to use auto-tuning which employs search algorithms for exploring the optimization space in order to improve the performance.

Load balancing is another key problem on heterogeneous systems. It refers to finding the most efficient mapping between a parallel computation and the heterogeneous processors. In general, load balancing on heterogeneous systems is accomplished by (over)decomposing the computational work into many small tasks which are dynamically assigned to the CPU and the GPU for execution. The main requirement is that algorithms must have multiple implementations, i.e. a version for the CPU and one for the GPU. When a task is assigned to a processor, the version corresponding to that processor's type is invoked. Task based load balancing is affected by scheduling overheads and the grain (or task) size problem, i.e. determining the optimal grain size that generates sufficient parallelism without amplifying the effect of overheads,

and makes the best use of the CPU and the GPU. Besides task based schemes, for computations that are data parallel, another load balancing scheme can be applied based on dividing the work into two chunks, one for the CPU and another one for the GPU. The condition is that the chunks must ensure that the CPU and the GPU finish processing at the same time. Such a scheme can be referred to as static load balancing. Its main benefit is that it does not suffer from the grain size problem. However, the disadvantage is that it is less adaptive, i.e. the initial work distribution cannot be modified. Adaptivity is important for input dependent programs and on non-dedicated systems where it is common that multiple running applications interfere with each other.

All the techniques mentioned above, i.e. redesigning data structures and algorithms, autotuning, and load balancing, are applied to the sparse grid technique [2], a numerical technique used for building numerical approximations of high-dimensional functions. Sparse grids address the curse of dimensionality problem, i.e. the number of grid points required by the representation of a function using a full grid depends exponentially on the number of dimensions. If a function is sufficiently smooth, then the sparse grid approximation offers an accuracy close to the one obtained using full grids but with considerably less points. Consequently, the sparse grid technique provides lossy compression functionality. In a computational steering application, sparse grids are used to compress high-dimensional simulation data. The compressed data is stored in a database and is later decompressed for visualization at interactive rates.

Both the compression and the decompression are obtained through recursive sparse grid algorithms. Moreover, complex key-value based data structures, e.g. hash tables and trees, are the typical solutions used for storing the sparse grid points and their corresponding values. Hence, in its initial form, the sparse grid technique is highly incompatible with GPUs. However, this thesis shows that by redesigning the data structures and the algorithms, an efficient implementation of sparse grids for GPU based heterogeneous systems can be achieved.

### **1.2** Scientific Contribution

There are three major contributions of this thesis:

- the porting of the sparse grid technique to GPUs (Chapter 4); the GPU implementation is based on a data structure characterized by minimal memory footprint (Chapter 3)

- an auto-tuning method for GPU programs (Chapter 5)

- load balancing schemes for data parallelism on heterogeneous systems (Chapter 6).

The first major contribution includes a data structure for sparse grids based on a bijective mapping. The data structure is at the core of the first GPU implementation of the sparse grid technique, developed as part of this thesis. The bijection eliminates the need to store the coordinates of grid points, meaning that the sparse grid is stored as a sequence of values ordered in a special way so that the index of every value can be transformed using the bijection into a multi-dimensional point of the grid and vice versa. The consequence is that the memory footprint of sparse grids is minimal. This property is especially beneficial in the context of GPUs because of their limited amount of memory, e.g. up to 6 GB. Using the bijection based data structure, bigger problems can be solved on the GPU. In addition to the data structure, redesigned non-recursive sparse grid algorithms are proposed together with a comprehensive set of CPU and GPU optimizations that improve locality and make better use of vector units. Furthermore, input specialized algorithms for sparse grids are proposed that exploit common patterns found in the input data. Although the bijection and the non-recursive algorithms especially address the constraints of GPUs, i.e. reduced memory and unsupported (or inefficient) recursion, they are also advantageous for CPUs.

Second, a **search based auto-tuning solution** is proposed for improving the GPU optimized implementations of the sparse grid algorithms. The cost of auto-tuning comes in the form of the time spent in searching for the optimal performance. Moreover, auto-tuning often deals with high-dimensional and highly unstructured search spaces which are difficult to explore efficiently. This thesis proposes a set of optimization parameters that are exported by the optimized GPU routines of the sparse grid technique. The parameters and their ranges are provided as input to a search engine whose responsibility is to find the values of the parameters that result in the best performance. In the context of auto-tuning, a contribution is represented by **search partitions**, i.e. a partition groups together interdependent optimization parameters and every partition is orthogonal to all the other partitions. In general, this results in a pruning of the search space and does not miss the optimum provided that correct assumptions are made regarding the dependent (or independent) parameters. In order to accelerate the auto-tuning process, an **input reduction technique** is proposed that reduces the size of the input data while ensuring that the global behavior for the initial data is captured. Auto-tuning is then used to optimize the GPU routines using the reduced data, thus executing in less time.