#### TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Entwurfsautomatisierung

## On the Sizing of Analog Integrated Circuits towards Lifetime Robustness

#### Xin Pan

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

| Vorsitzender:              |    | UnivProf. Dr. sc. techn. Andreas Herkersdorf     |

|----------------------------|----|--------------------------------------------------|

| Prüfer der Dissertation: 1 | 1. | PrivDoz. DrIng. Helmut Gräb                      |

| 2                          | 2. | UnivProf. Dr. rer. nat. Doris Schmitt-Landsiedel |

Die Dissertation wurde am 31.10.2012 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 22.05.2013 angenommen.

A paperback version of this thesis was published by Verlag Dr. Hut, Munich, in 2013. ISBN 978-3-8439-1198-6.

#### Acknowledgements

From March 2008 to October 2012, I worked as a research assistant at the analog CAD group of Institute for Electronic Design Automation, Technische Universitaet Muenchen. During this period, I had the opportunity to work with many nice people, colleagues and friends, with wonderful ideas and personalities. I would like to express my deep gratitude to them, without whom my doctoral research would not be successful.

Firstly I would like to thank Professor Ulf Schlichtmann for giving me the chance to work at the institute, as well as for his warm help during my Master study at the university. Thanks to the Master program, I had the opportunity to come to Germany and studied my favorite subjects, with contacts to many nice colleagues around several institutes already during that period.

My special thanks go to my doctoral research supervisor, PD Dr.-Ing. Helmut Graeb. He opened the gate of analog CAD to me with interesting topics and emerging physical effects of semiconductor technologies. I remember every moment we discussed ideas, checked formulas, shared progress and chatted for fun. He always motivated me to proceed in my research with warm encouragement and constructive feedbacks which I appreciate very much. I thank him also for the time and efforts in proofreading all my publications, thesis and presentation slides.

I would like to thank all of the colleagues at the institute, especially the members of the analog group, namely Dr. Daniel Mueller, Dr. Tobias Massier, Husni Habal, Michael Eick, Michael Pehl, Michael Zwerger and Aurélien Tchegho. The fruitful discussions during the study and research, valuable feedbacks on presentations and results, as well as the colorful events organized by them will be the most cherished piece of memories in my life.

Last but not least, I would like to express my deep gratitude to my parents Gang and Baozhen for their continuous and invaluable encouragement. Sincerely, I thank my wife Chang for her very kind understanding and solid supports all the time, and my lovely baby Keyun for bringing us the endless happiness.

Many thanks to you all.

Munich, October 2012 Xin Pan

# Contents

| 1 | Intro | oduction                                                                | 1  |  |  |  |  |

|---|-------|-------------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1   | Motivation                                                              | 1  |  |  |  |  |

|   | 1.2   | Analog Design                                                           | 3  |  |  |  |  |

|   |       | 1.2.1 Typical Flow of Analog Integrated Circuit Design                  | 3  |  |  |  |  |

|   |       | 1.2.2 Discussions and Challenges                                        | 5  |  |  |  |  |

|   | 1.3   | Contributions of this Thesis                                            | 6  |  |  |  |  |

|   |       | 1.3.1 Study on Joint Effects of Process Variations and Transistor Aging | 6  |  |  |  |  |

|   |       | 1.3.2 Design Flow for Lifetime Robustness Optimization                  | 7  |  |  |  |  |

|   |       | 1.3.3 Analytical Modeling for Aged Yield Prediction                     | 7  |  |  |  |  |

|   | 1.4   | Previous Publications                                                   | 8  |  |  |  |  |

|   | 1.5   | Organization of this Thesis                                             | 8  |  |  |  |  |

|   | 1.6   | Summary                                                                 | 8  |  |  |  |  |

| 2 | Reli  | ability Issues                                                          | 11 |  |  |  |  |

|   | 2.1   |                                                                         | 11 |  |  |  |  |

|   | 2.2   |                                                                         |    |  |  |  |  |

|   |       | 2.2.1 Reliability Function $R(t)$ and Failure Rate $z(t)$               | 12 |  |  |  |  |

|   |       | 2.2.2 Negative Bias Temperature Instability                             | 15 |  |  |  |  |

|   |       | 2.2.3 Hot Carrier Injection                                             | 18 |  |  |  |  |

|   |       | 2.2.4 Time-Dependent Dielectric Breakdown                               | 19 |  |  |  |  |

|   |       | 2.2.5 Electromigration                                                  | 19 |  |  |  |  |

|   | 2.3   | State of the Art                                                        | 20 |  |  |  |  |

|   |       | 2.3.1 Reliability Simulation                                            | 20 |  |  |  |  |

|   |       | 2.3.2 Solutions towards Transistor Aging                                | 21 |  |  |  |  |

|   |       |                                                                         | 23 |  |  |  |  |

|   |       | 2.3.3.1 Statistical Methods                                             | 23 |  |  |  |  |

|   |       | 2.3.3.2 Deterministic Methods                                           | 25 |  |  |  |  |

|   |       | 2.3.4 Joint Effects of Transistor Aging and Process Variations          | 27 |  |  |  |  |

|   | 2.4   | Summary                                                                 | 29 |  |  |  |  |

| 3 | Prol  | blem Formulation                                                        | 31 |  |  |  |  |

|   | 3.1   | Age and Lifetime                                                        | 31 |  |  |  |  |

|   | 3.2 | Param   | neters                                                   | 32 |  |  |  |

|---|-----|---------|----------------------------------------------------------|----|--|--|--|

|   |     | 3.2.1   | Design Parameters                                        | 32 |  |  |  |

|   |     | 3.2.2   | Statistical Parameters with Aging                        | 33 |  |  |  |

|   |     | 3.2.3   | Operating Parameters                                     | 35 |  |  |  |

|   | 3.3 | Perfor  | mances with Aging                                        | 36 |  |  |  |

|   | 3.4 |         | Yield and Aged Yield                                     | 37 |  |  |  |

|   |     | 3.4.1   | Definition                                               | 37 |  |  |  |

|   |     | 3.4.2   | Statistical Analysis Method                              | 40 |  |  |  |

|   | 3.5 | Sizing  | Rules with Aging                                         | 43 |  |  |  |

|   | 3.6 |         | hary                                                     | 45 |  |  |  |

| 4 | Age | d Yield | d Optimization with Fresh and Aged Sizing Rules          | 47 |  |  |  |

|   | 4.1 |         | -Case Distance                                           | 47 |  |  |  |

|   |     | 4.1.1   | Yield Analysis and Worst-Case Analysis                   | 47 |  |  |  |

|   |     | 4.1.2   | Yield Estimation Based on Worst-Case Distance            | 50 |  |  |  |

|   |     | 4.1.3   | Problem Formulation towards Worst-Case Distance Based    |    |  |  |  |

|   |     |         | Yield Estimation                                         | 54 |  |  |  |

|   |     | 4.1.4   | Solution using Lagrangian Functions                      | 56 |  |  |  |

|   | 4.2 | Aged    | Worse-Case Distance and Aged Yield                       | 59 |  |  |  |

|   | 4.3 |         |                                                          |    |  |  |  |

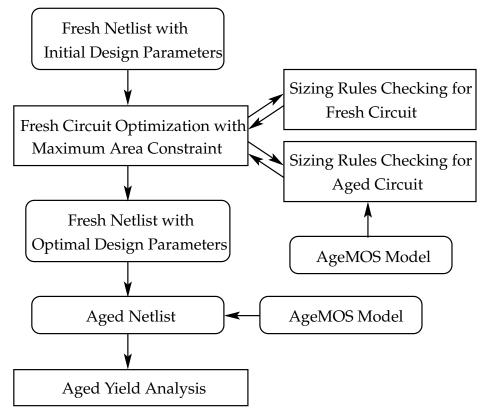

|   |     | 4.3.1   | Simulation Flow of the Aged Circuit                      | 61 |  |  |  |

|   |     | 4.3.2   | Fresh and Aged Sizing Rules of a Circuit                 | 65 |  |  |  |

|   |     | 4.3.3   | Circuit Layout Area Estimation                           | 65 |  |  |  |

|   |     | 4.3.4   | Optimization of Fresh Circuit with Fresh and Aged Sizing |    |  |  |  |

|   |     |         | Rules Checking and Maximum Area Constraints              | 66 |  |  |  |

|   |     | 4.3.5   | Aged Yield Analysis                                      | 70 |  |  |  |

|   | 4.4 | Summ    | nary                                                     | 71 |  |  |  |

| 5 | Age | d Yield | d Prediction                                             | 73 |  |  |  |

|   | 5.1 | Aged    | Worst-Case Distance Prediction Model                     | 75 |  |  |  |

|   |     | 5.1.1   | Idea                                                     | 75 |  |  |  |

|   |     | 5.1.2   | Linear Performance Model at $t_1$                        | 75 |  |  |  |

|   |     | 5.1.3   | Mapping from $t_0$ to $t_1$                              | 77 |  |  |  |

|   |     | 5.1.4   | Prediction of $\beta_{w,U}(t_1)$                         | 77 |  |  |  |

|   |     | 5.1.5   | Second Order Sensitivity Term                            | 79 |  |  |  |

|   | 5.2 | Algor   | ithm for the Aged Yield Prediction                       | 80 |  |  |  |

|   | 5.3 | Summ    | nary                                                     | 81 |  |  |  |

| 6 | Ехр | erimen  | ntal Results                                             | 83 |  |  |  |

|   | 6.1 | Miller  | Operational Amplifier                                    | 83 |  |  |  |

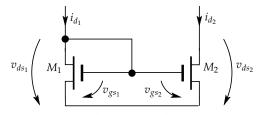

|                    |              | <ul><li>6.1.1</li><li>6.1.2</li><li>6.1.3</li><li>6.1.4</li></ul> | Circuit TopologyCircuit Performances and their SpecificationsResults on Aged Yield OptimizationResults on Aged Yield Prediction | <br> | • |    | 83<br>84<br>87<br>90     |

|--------------------|--------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|---|----|--------------------------|

|                    | 6.2          |                                                                   | ed Cascode Operational Amplifier                                                                                                |      |   |    | 92                       |

|                    |              | 6.2.1                                                             | Results on Aged Yield Optimization                                                                                              |      | • | •  | 92                       |

|                    |              | 6.2.2                                                             | Results on Aged Yield Prediction                                                                                                |      |   | •  | 94                       |

|                    | 6.3          | Sumn                                                              | nary                                                                                                                            |      | • | •  | 96                       |

| 7                  | 7 Conclusion |                                                                   |                                                                                                                                 |      |   | 97 |                          |

| Bibliography       |              |                                                                   |                                                                                                                                 |      |   |    | 99                       |

| List of Figures    |              |                                                                   |                                                                                                                                 |      |   | •  | <b>111</b><br>111<br>113 |

| Abstract in German |              |                                                                   | erman                                                                                                                           |      |   |    | 115                      |

# Chapter 1

# Introduction

## **1.1 Motivation**

Entering the 2010's, a huge progress in the electrical engineering and information technology changes our daily life in various ways. For example, the traditional cell phone has been gradually replaced by the smartphones and multi-function cell phones [wikb], which are capable of running various applications based on their mobile operating platforms. They integrate together various functions such as digital camera and video recorder, GPS receiver, accelerometer, wireless internet connections and so on. The spread of the tablet personal computer (Tablet PC) [wikc] also gives people a totally different view about how a computer can be used and played on one single touchscreen which serves as both input and output devices . Another example is in the automotive industry [eet]. A typical modern car responds to driver's commands and environmental conditions in a way which is much smarter, faster and safer than ever before. More and more functions of the car are assisted automatically by microcontrollers in real time, such as driving, controlling, safety functions, navigation and entertainment systems, etc.

One of the key enabler of all these advances is the continuous development and improvement in the Integrated Circuits (IC) industry. After the first practical IC was invented simultaneously by Jack Kilby at Texas Instruments [Kil] and Robert Norton Noyce at Intel [Noy] in 1959, the idea of manufacturing various circuit components on a small piece of semiconductor material was intensively explored and further developed. From 1960's until today, the number of transistors in an integrated circuit follows the Moore's law, which states that such number doubles every two years [Moo75] (although initially it was stated as every year in [Moo65]). Thanks to the numerous innovations since then (such as the invention of the Complementary

#### 1 Introduction

Metal-Oxide Semiconductor (CMOS) process by Frank Wanlass in 1963 [Wan], the invention of the excimer laser photolithography by K. Jain at IBM in 1982 [JWL82], and so on), the capability of integrating an increasing number of transistors on a single chip is greatly enhanced. The trend described by the Moore's law has been followed quite well by now and is expected to be valid in the near future. [Sch97]

Today, what a complex system did in the past has been integrated onto a single chip, consisting of several billions of components. Such chip can provide much more functionality than ever before, combining logic functions, memory, analog and mixed-signal applications. Such improvement means increased circuit complexity and enhanced circuit performance features, computational capability, data storage and the power consumption. With the help of the continuous improvement and progress in photolithography, the corresponding minimum feature sizes in chip manufacturing process has shrunk from 500 nanometer in 1990's to 45 nanometers and below in 2010's, as summarized and predicted by the International Technology Roadmap for Semiconductors (ITRS) Report 2009 [I.T].

However, despite the bright future seen by the above mentioned integration, many side effects and challenges arise due to the continuous shrinking of the semiconductor technology. The ITRS Report 2009 summarizes the challenges faced in the semiconductor industry in the near future and in the long term for logic device, memory device, RF, analog and mixed-signal circuitry, as well as for the new materials and manufacturing process [I.T].

Among the challenges arising from the development of the integrated circuits, the effects of manufacturing process variations and operational lifetime circuit reliability are becoming significant. Different from many other challenges, these effects can be and should be considered early during design phase by the designers, thus the designed circuits are well tolerant of such known effects. Especially for those safety-critical application areas, such as automotive and aviation industry, safety controller, or computational capability-sensitive fields, such as high performance computers, where deviations from specifications are not acceptable.

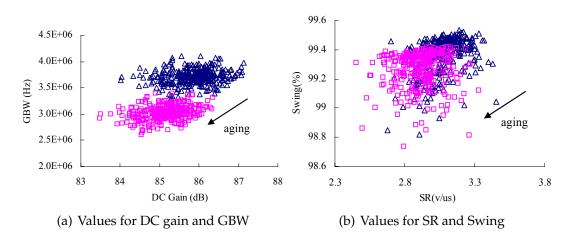

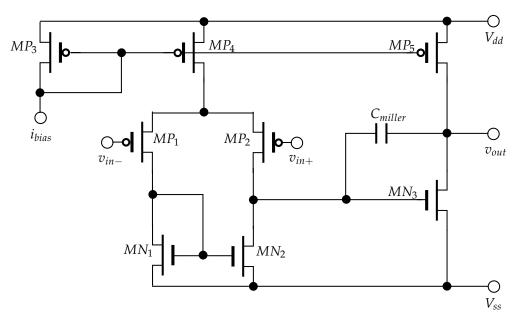

An example of the joint effects on a typical analog circuit block is illustrated in Figure 1.1, where 300 Monte-Carlo simulations are run on a fresh and 5-year-old Miller operational amplifier with a 180nm industrial technology. Values of DC Gain and Gain-Bandwidth Product (GBW) are shown in Figure 1.1(a), and values of slew rate (SR) and output voltage swing (Swing) are shown in Figure 1.1(b). The clouds of performance distributions, as shown in the figures, are the result of manufacturing process variations. They deviate from their nominal values due to the imperfectness during the manufacturing process. The shifts of the performance distributions in 5 years, on the other hand, result from drifts of transistor parameters, such as  $V_{th}$ , due

**Figure 1.1:** Shift of the performance distributions from 300 Monte-Carlo simulation samples on a fresh (triangles) and 5-year-old (squares) Miller operational amplifier.

to negative-bias-temperature-instability and hot carrier injection during circuit operations. As can be clearly seen in the figures, both performance distributions move towards negative directions. Certain samples of the circuits thus may fall out of the possible performance specifications during operational time, resulting in an early wear-out, or in other words, a shorter lifetime than expected.

As a result, the tolerance design of integrated circuits considering manufacturing process variations and lifetime circuit reliability have been the major concern for the integrated circuit designers as well as for the manufacturers since the last decades until today. The physical roots and behaviors of these effects will be detailed in the next chapter.

## 1.2 Analog Design

#### 1.2.1 Typical Flow of Analog Integrated Circuit Design

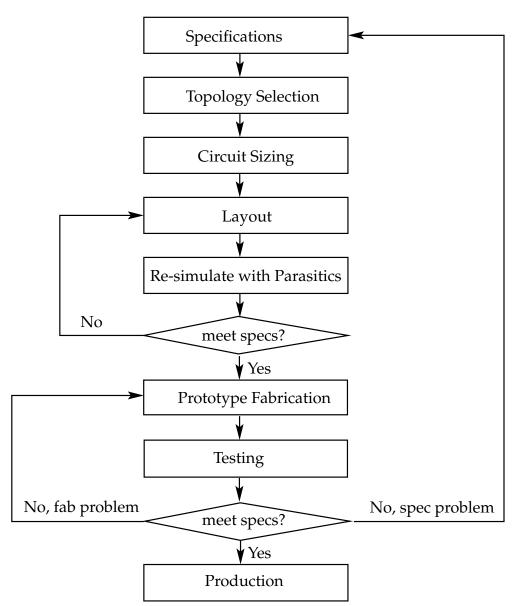

In the context of this thesis, the focus is on the methodology of design and analysis of the analog part of the integrated circuits. A typical analog integrated circuit design flow, consisting of several steps and loops [Bak08], can be summarized in Figure 1.2.

The input of the flow are the specifications. They describe the functionalities of the circuit, as well as the information from the manufacturing technology needed for the

Figure 1.2: Typical design flow of analog integrated circuits [Bak08]

design. The functionalities specify the operational range of the circuit such as temperature, supply voltage, and the output requirements such as gain, power, speed of the circuit block. They are the targets that the produced circuit must meet. The information from the manufacturing technology on the other hand include manufacturing process statistics, technology constraints like minimal size and space in physical dimensions. The next step is the topology selection, which remains one of the most creative task for a circuit designer who has to select the appropriate device types and connections to achieve the specifications. This selection is mostly based on the experience of the designer.

Then, for the selected circuit topology, the device parameters, such as transistor dimensions, values of resistors and capacitors, and so on, have to be tuned properly in order to meet the specifications and to increase the robustness over variations in the manufacturing process and the operational environment. This step is called circuit sizing. This step is performed in a looped manner such that the designer must check the simulation results after they make adjustments to certain device parameters.

The steps until now are also referred to as the frontend of the analog design process. Then, the next steps belong to the backend part.

If all of the pre-defined specifications are fulfilled, now it comes to the step of layout, generally performed by layout designers. The placement and interconnections of each device on the chip over different layers are determined at this step. Once the layout is done, parasitic parameters such as strap capacitance and leakage can be extracted and calculated. Re-simulations with these parasitics are necessary. This step is repeated until all specification are met considering layout parasitics.

The next tasks are moved onto fabrication. At first, prototype chips are fabricated and tested. Then any encountered fab problem is fixed. If at this stage the performance of fabricated chip cannot meet the requirements and it is not a fab problem, a redesign from the first step has to be performed, which is obvious a huge waste of time and investment.

Finally, when the chip meets all the specifications, it is ready for production.

## 1.2.2 Discussions and Challenges

One observation from the above typical analog integrated circuit design flow is that the designed circuit performances are subject to many influential factors, especially the influences due to the uncertainties during circuit operation in real-time, as well as the imperfectness during the manufacturing process.

Although beyond designers' control, those influential factors must be well considered by designers during the design step. The circuit must meet the specifications under the maximal tolerance region of uncertainties from operational conditions and process variations, otherwise several redesign loops are needed, as can be seen in Figure 1.2. Such redesign loops should be kept as few as possible, since they result in an increase of overall costs and decrease of the time to market.

One typical solution for designers to meet those requirements is to separate their design/sizing process into several steps, such as nominal design and design centering. During the nominal design step, no tolerance region is considered. It is mainly used for the architecture investigation, served as the starting point for the design centering as well. During design centering, the tolerance region of process variations and operational conditions are considered. Certain mathematical models are built up for different uncertainty sources. The designers then refine their design with consideration of the uncertainties by the help of those mathematical models, in order to make sure that their circuit can meet all the specifications under all circumstances.

Another observation from the analog design flow is that, in contrast to the digital part, the above analog design flow is mostly done manually. The analog design automation is generally available only for the circuit simulation step.

From the design of the circuit to the circuit layout, most of the steps in the analog circuit design flow still require experience from designers and layout engineers. As the circuit complexity grows and many challenges arise as discussed in Section 1.1, it is pointed out by numerous studies that the analog parts of the chip design are most frequently at fault when chips fail at first silicon [BC10]. It means a huge re-design cost, if the initial design cannot meet specifications considering possible side effects and challenges. Thus new methodologies for analog design automation are needed considering effects such as process variations and lifetime parameter degradations.

## **1.3 Contributions of this Thesis**

## 1.3.1 Study on Joint Effects of Process Variations and Transistor Aging

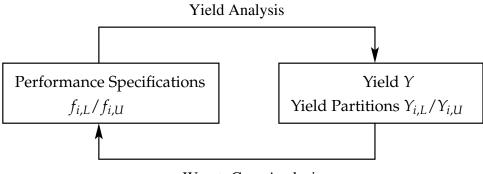

This thesis studies deeply the joint effects of manufacturing process variations and transistor aging. The state-of-the-art methods for design centering considering process variations, and solutions towards transistor aging are studied thoroughly. The physical modeling and behavior as well as the impact of various transistor aging issues are focused. The general problem of the joint effects is formulated analytically as optimization problems.

## 1.3.2 Design Flow for Lifetime Robustness Optimization

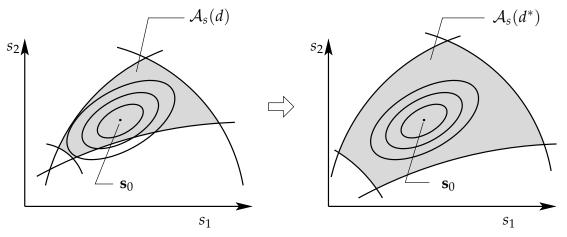

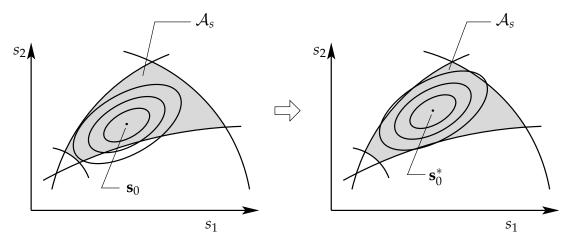

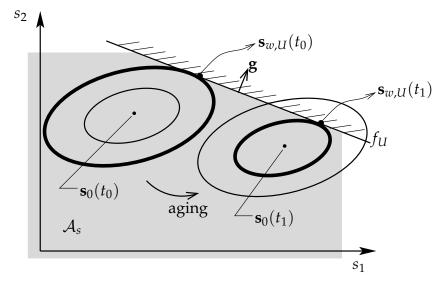

This thesis extends the formulations and applications of the so-called worst-case distance, which is a measure of the design robustness over process variations and operating conditions, into reliability modeling and optimization considering transistor aging over lifetime. The aged worst-case distance in lifetime can be used to study the aged yield value.

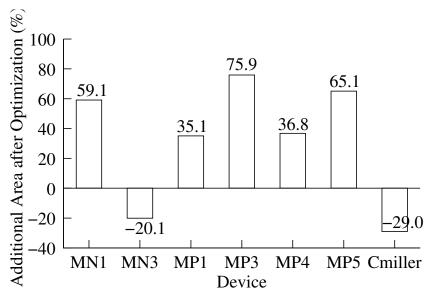

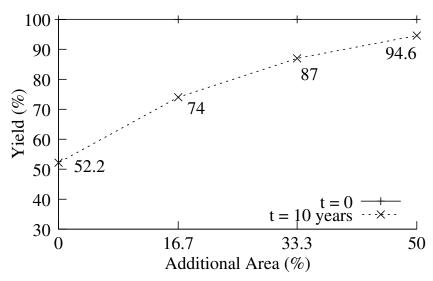

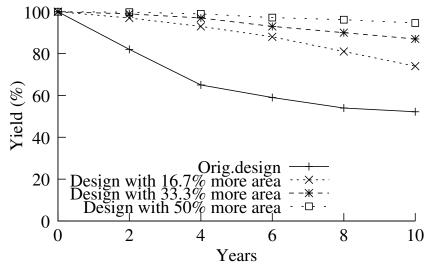

A new design flow is proposed to optimize the lifetime robustness of analog circuits, by optimizing the fresh circuit with the checking of both fresh and aged sizing rules, as well as maximum layout area constraints, to achieve x-sigma robustness in circuit's lifetime. Then the lifetime robustness of the circuit is analyzed by the evaluation of aged worst-case distance values.

By applying the design flow repeatedly with different maximum area constraints, the trade-off between circuit's lifetime robustness and the price we pay in terms of the circuit layout area can be obtained. Circuit designers can choose from different product reliability categories with an acceptable area overhead.

## **1.3.3 Analytical Modeling for Aged Yield Prediction**

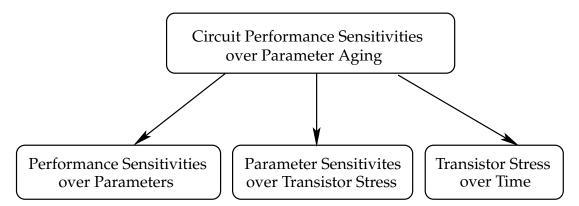

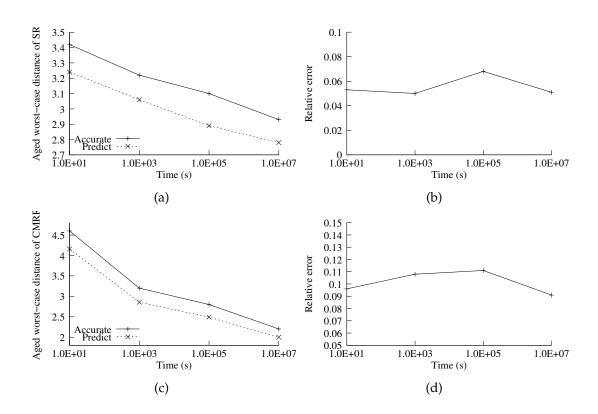

This thesis proposes a modeling and prediction framework to predict the aged worstcase distance value and the corresponding lifetime robustness of analog circuits. The proposed method is based on the sensitivity analysis of transistor parameters over aging, as well as the sensitivity analysis of the circuit robustness over transistor parameters.

It does not involve either analytical formulation of circuit performance or Monte-Carlo simulations. In comparison to the aged yield analysis based on the geometrical yield modeling, the proposed method is more efficient in obtaining the aged worstcase distance values.

Using the proposed method, circuit designers can obtain quickly an overview of the lifetime robustness of their design, since the fresh worst-case distance is already available for a fresh-optimal design. Certain weakness in the lifetime robustness of their design can be obtained early and quickly, thus reducing the redesign cost.

#### **1.4 Previous Publications**

During the past four years, parts of the work presented here were published in [GP09], [PG09], [PG10b], [PG10c], [PG10a], [PG11a], [PG11b] and [PG12]. A twostep reliability optimization flow involving a fresh yield optimization step for the fresh circuit and a lifetime yield optimization step for the aged circuit was detailed in [GP09] and [PG09]. Its software demonstration was presented in [PG10a]. To speed up the analysis of the aged yield value of the circuit, a linear approximation model was introduced in [PG10b], while in [PG10c] several improvements were detailed. The layout area cost for the reliable design was presented in [PG11a]. In [PG11b] the detailed trade-off between circuit reliability and layout area cost was analyzed. An improved version with study into each transistor area and circuit performance was published in [PG12].

## 1.5 Organization of this Thesis

The rest of the thesis is organized as follows. Chapter 2 discusses in detail of the reliability issues of the modern analog integrated circuit design process. Chapter 3 gives the problem formulation of the work presented in this thesis. Special focus is on the formulation of both fresh and aged yield on different design spaces, as well as the fresh and aged sizing constraints. The analysis and requirements concerning statistical analysis methods are discussed in detail. Chapter 4 studies the problem of robustness optimization by fresh yield optimization with consideration of both fresh and aged sizing rules. The fresh circuit is over-designed such that it is tolerant of both process variations and transistor aging. Then Chapter 5 proposes an analytical prediction model based on sensitivity analysis to approximate the aged worst-case distance value and its corresponding aged yield. The model can be used to predict the age of the circuit as well, providing the acceptable aged yield value as the input. The experimental results on different circuitries using industrial models are given in Chapter 6. Finally Chapter 7 concludes the thesis.

## 1.6 Summary

The continuous scaling of semiconductor technology into nanometer scale contributes to the higher chip densities, circuit performances, lower cost per transistor, as well as several challenges and side effects, which will limit the product yield value after manufacturing and in circuit lifetime. Among those hazards, most influential problems arise from manufacturing process variations and transistor degradation related lifetime circuit reliability.

The thesis concentrates on the sizing methodology solutions to the joint effects of process variations and transistor aging. New modeling and prediction framework will be introduced in the thesis.

# **Chapter 2**

# **Reliability Issues**

This chapter presents in detail the reliability issues studied in the thesis. The reliability issues in general relate with the uncertainties of the produced circuits in operating time, in comparison to the figure of merit specified during design time. Section 2.1 covers the manufacture process induced variations and the resulting uncertainties of the manufactured circuits. Section 2.2 introduces the important degradation effects occurred in operating time. Section 2.3 introduces and discusses about the current solutions in solving manufacturing process variations and transistor aging problems.

## 2.1 Process Variations

The modern semiconductor manufacturing normally consists of series of processing steps. From now on we focus on the CMOS technology as it is used in most Very Large Scale Integrated (VLSI) or Ultra Large Scale Integrated (ULSI) circuit chips [Bak08]. Typically those processing steps are performed on ultrapure, defect-free slices of silicon wafers, and photolithography is used repeatedly to build up various features on different locations through multiple layers on the surface of the wafer.

The variations induced during the manufacturing process can be both systematic and random [Nas08]. The systematic variations, or intra-die variations, refer to those variations occurring repeatedly over many chips or wafers, i.e., at system level. Examples of the systematic variations can be wafer-level variations due to layout-induced strain, optical-proximity correction [Sah10], the rapid ramp-rate of the lamp thermal annealing process [ea06], etc. The random variations or inter-die variations, on the other hand, refer to the fluctuations which happen in a statistical manner during the manufacturing process such as thermal oxidation, doping process, etc. Examples of

random variations can be random discrete doping, line-edge roughness, line-width roughness, interface roughness [Sah10], etc. They contribute to the variations of each transistor's threshold voltage or oxide thickness, and so on.

In comparison to the systematic variations which can be addressed either by making changes to the design or by improvements in the manufacturing process, the random variations can only be tolerated if the initial design has enough margins built by the designers. In other words, the designers have to consider during the design phase the worst case scenario that may happen during the manufacturing process to ensure that the circuit can work properly under process variations.

## 2.2 Reliability

## **2.2.1** Reliability Function R(t) and Failure Rate z(t)

In traditional reliability engineering, *Reliability Function* and *Failure Rate* are two very important indicators of the device reliability properties. The study presented in this thesis is closely linked to the evaluation and approximation of the reliability function and failure rate of analog integrated circuits. While detailed discussion will be presented in later chapters, here some basic introduction and definitions regarding these reliability engineering terms are given.

The term *Reliability* is defined as the probability that a device will function without failure over a specified time period or amount of usage, according to the IEEE Standard Dictionary of Electrical and Electronic Terms [RI97].

Here, the term *amount of usage* refers to those kinds of one-shot items, such as electronic fuses, safety matches, etc., the usage of which can be divided into two phases: a non-active phase and an active phase. Since analog circuits mainly operate continuously, we focus our discussion only on the continuous operation devices hereafter, i.e., the term *a specified time period* is of interest here.

The reliability thus can be defined as follows. Assume the lifetime of a device is a random variable, denoted by *X*, and its cumulative distribution function F(t) corresponds to the probability that *X* will not exceed a certain *t*, i.e.,  $F(t) = \text{prob}(X \le t)$  Then, the reliability of the device, denoted by R(t), is

$$R(t) = \operatorname{prob}(X > t) \tag{2.1}$$

$$= 1 - F(t) \tag{2.2}$$

R(t) is the so-called *Reliability function*, while F(t) is the so-called *lifetime distribution function* [BJ77]. The above definition comes from the fact that the reliability of a device at time *t* is also the probability that the lifetime of the device will exceed *t*. In other words, 1 - R(t) equals the value of the lifetime distribution function at *t*. Three observations from (2.2) can be made:

1. when

$$t = 0$$

,  $R(0) = 1$ ;

- 2. when  $t \to \infty$ ,  $\lim_{t \to \infty} R(t) = 0$ ;

- 3. R(t) must be an non-increasing function of time *t*.

The first observation implies an important assumption that, at t = 0, all of the devices are just manufactured and all of them can work properly. At this time, no aging effect happens, and no transistor parameter drifts due to reliability issues. The second observation can be stated also as all of the devices have their maximum lifetime, beyond which they will not work properly any more. And the last observation comes from the definition of R(t).

The failure rate z(t), on the other hand, comes from such a probability evaluation. Considering a small time interval between t and t + dt, the product z(t)dt is thus the probability that a device is failed during this time interval dt, given the condition that it works properly at least until t:

$$z(t)dt = \operatorname{prob}(t < X < t + dt | X > t)$$

=

$$\frac{\operatorname{prob}(t < X < t + dt)}{\operatorname{prob}(X > t)}$$

=

$$\frac{F(t + dt) - F(t)}{R(t)}$$

(2.3)

z(t) can be obtained if (2.3) is divided by dt:

$$z(t) = \frac{F(t+dt) - F(t)}{dt} \cdot \frac{1}{R(t)} = \frac{f(t)}{R(t)}$$

(2.4)

where f(t) is the lifetime probability density function, defined as

$$f(t) = \frac{dF(t)}{dt}$$

(2.5)

$$= -\frac{dR(t)}{dt}$$

(2.6)

The failure rate z(t) is also known as hazard rate, or hazard.

The relationship between R(t) and z(t) can be obtained from (2.4). Since

$$z(t) = \frac{f(t)}{R(t)} = \frac{-dR(t)/dt}{R(t)},$$

(2.7)

we can get R(t) by integration:

$$R(t) = \exp\left[-\int_0^t z(\xi)d\xi\right]$$

(2.8)

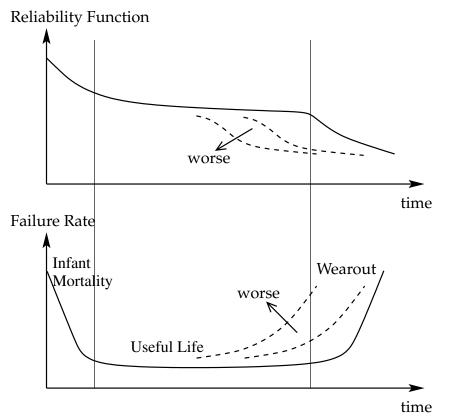

**Figure 2.1:** The Bathtub Curve with effects of the device increasing wearout degradations.

The typical reliability curve is the so-called *bathtub curve* [BJ77], [KKW03], [Hjo80], as shown in Figure 2.1. The name *bathtub* comes from the shape of the failure rate curve z(t) in the lower part of Figure 2.1.

Three typical regions can be identified in Figure 2.1.

- The first is the "infant mortality" period, during which the devices may fail due to initial weakness or defects. The failure rate of this period often drops quickly, until reaching a relatively constant level.

- Now it is the second period when the devices are in their useful normal operating life. In this period the failure rate is approximately constant and very small. It is also called intrinsic failure period. As the time proceeds, the devices gradually degrade due to various aging effects.

- Then the system enters the last period, the wearout period. The failure rate of this period is increasing, and the whole system gradually reaches the end of its useful lifetime.

An example function concerning R(t) and z(t) is from exponential distribution, which is useful when approximating R(t). In this case, the lifetime distribution function F(t) is  $1 - e^{-\lambda t}$ , where  $\lambda$  is a positive constant. According to (2.2) and (2.7), R(t) and z(t) can be expressed as

$$R(t) = e^{-\lambda t} \tag{2.9}$$

$$z(t) = \lambda \tag{2.10}$$

where the failure rate z(t) remains constant during the useful lifetime of the product.

Also shown in Figure 2.1 are the effects which may worsen the device reliability due to increasing aging effects, as can be seen on the dotted lines. Such degradation may happen early during the device normal lifetime, causing the failure rate to increase even during the designed useful lifetime of the devices. As introduced in the following, such problem is getting worse as the semiconductor technology continuously scales.

Some of the most important degradation effects on transistors and on-chip interconnects are reviewed in the following sections. Their impacts on the transistor parameters or on the interconnects are discussed. For a more complete discussion, please refer to [HTH<sup>+</sup>85], [SB03], [AKVM07], [WRK<sup>+</sup>07], [WSH00].

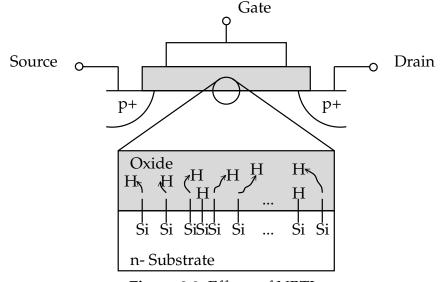

#### 2.2.2 Negative Bias Temperature Instability

The physical behavior of <u>N</u>egative <u>B</u>ias <u>T</u>emperature <u>I</u>nstability (NBTI) on a PMOS transistor is shown in Figure 2.2. As the name indicates, NBTI manifests itself when the PMOS transistor is "negative" biased, i.e.,  $V_{gs} < 0$ . It is commonly accepted that NBTI is the result of hole-assisted breaking of Si-H bonds at Si/SiO<sub>2</sub> inter-

face [AKVM07] when a PMOS is negative biased using the Reaction-Diffusion (R-D) model:

$$\frac{dN_{IT}}{dt} = k_F (N_0 - N_{IT}) - k_R N_H(0) N_{IT}$$

(2.11)

where  $N_{IT}$  is the fraction of Si-H bonds at the Si/SiO<sub>2</sub> interface which breaks at time t,  $N_0$  is the initial number of all Si-H bonds, and  $k_F$  is the dissociation rate constant. The second term in (2.11) describes the annealing process of the released H atoms.  $N_H(0)$  is the H concentration at the interface.

Figure 2.2: Effects of NBTI

NBTI is getting more serious as technology scales, since the vertical oxide field is continuously increasing to enhance transistor performance. Thus a hole in the channel can be easily captured and a two-electron Si-H covalent bond at the Si/SiO<sub>2</sub> interface can be weakened by it. The weakened Si-H bonds break easily at certain high temperature. Atomic H's are released in short time, then they convert to and diffuse as molecular H<sub>2</sub> in long time (>100 s) [AKVM07].

NBTI effect will degrade certain transistor parameters, such as threshold voltage, drain current, transconductance, etc. Threshold voltage degradation due to NBTI is given by [YQD<sup>+</sup>09]

$$\Delta V_{th} = A \left(\frac{V_{gs}}{t_{ox}}\right)^{\alpha} \exp\left(-\frac{E_a}{kT}\right) t^n$$

(2.12)

where *K* is Boltzmann's constant, *A* is a process related prefactor,  $E_a$  is the activation energy,  $\alpha$  denotes voltage acceleration factor, n = 1/4 for atomic H in short time, and n = 1/6 for molecular H<sub>2</sub> in long time as discussed above.

A well known effect of NBTI on PMOS transistor is its partial recovery, or annealing, when the stress is removed [CCL<sup>+</sup>03], [RMY03]. Several studies on the modeling of this dynamic behavior and its application in the design of digital circuits are presented in [VWC06], [LWH<sup>+</sup>07]. For SRAM cell, the impact of fast-recovering NBTI degradation is studied in [DHGSL10]. But for analog circuits, the NBTI recovery is not obvious [JRSR05]. The reason for this is the presence of the constant DC biasing voltage in the most of analog circuits, which leads to a continuous stress voltage applied on the transistors in analog circuits. Such continuous stress voltage is not depend on the input signals. As a result, NBTI recovery or annealing is a minor effect for analog circuits and will be ignored in the rest of this thesis.

The intrinsic variations of NBTI effects are studied in [Rau02]. The expression of variation in  $\triangle V_{th}$  shift is

$$\sigma(\triangle V_{th}) = \sqrt{\frac{Kt_{ox}\mu(\triangle V_{th})}{A_G}}$$

(2.13)

where  $t_{ox}$  is effective gate oxide thickness,  $A_G$  is its area and K is an empirical constant. As tested by authors in [FAH<sup>+</sup>08] and [FAH<sup>+</sup>09], for the transistor parameters  $V_{th}$  and  $I_d$ , their probability density functions follow a Gaussian distribution pre and post NBTI stress.

It is pointed out in [SB03] that, NBTI should not exhibit any gate length dependence, since it does not depend on lateral electric fields. But NBTI is sometimes enhanced with reduced gate length, which is not well understood yet. The closeness of the source and drain maybe one of the reasons for that.

The introduction of new dielectric material, such as high- $\kappa$  gate dielectrics (with high dielectric constant  $\kappa$  compared to silicon dioxide), is one of several strategies developed to allow further shrinking recently [wika]. But at the same time, a so-called Positive Bias Temperature Instability (PBTI) effect on a NMOS transistor occurs as the transistor degrades over time if the NMOS transistor is biased positively.

Recently a reliability assessment of voltage controlled oscillators in 32nm high- $\kappa$ , metal gate technology is presented in [CFSL10] with aging behavior assessment due to NBTI on PMOS transistors and PBTI on NMOS transistors. A detailed study into the impact of analog circuit operations is presented later in [CMFSL11b]. Another study of NBTI and PBTI effects on 6T SRAM memory cell is presented in [DGSL09], showing the significant impact of process variations, NBTI and PBTI on future technologies with new material.

#### 2.2.3 Hot Carrier Injection

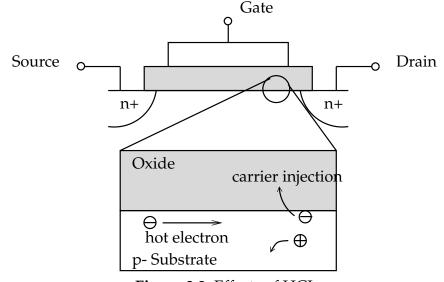

Figure 2.3 shows the simplified physical effects of <u>Hot Carrier Injection (HCI)</u> on an NMOS transistor. HCI refers to the injection of channel carriers from the conducting channel under the gate into the gate dielectric. In contrast to NBTI, which happens uniformly in the channel, HCI mainly happens near the drain area where the lateral electric field is high and the channel carriers gain enough kinetic energy during the acceleration along the channel. Hot channel carriers may hit an atom in the substrate, breaking an electron-hole pair or a Si-H bond, and introducing interface traps and a substrate current.

Figure 2.3: Effects of HCI

Traditional modeling method of HCI is by analyzing the substrate current  $I_{sub}$  [HTH<sup>+</sup>85]. The correlation is due to the fact that both hot-carriers and substrate current are driven by a common factor-the maximum channel electric field  $E_m$  at the drain end. Some recent research [WRK<sup>+</sup>07] point out that, as technology scales,  $I_{sub}$  will be dominated by various leakage components such as gate leakage, junction current, etc. Authors in [WRK<sup>+</sup>07] proposed the following reaction-diffusion based model for the degraded parameter  $\Delta V_{th}$  due to HCI as:

$$\Delta V_{th} = \frac{q}{C_{ox}} K_2 \sqrt{Q_i} \exp\left(\frac{E_{ox}}{E_{o2}}\right) \exp\left(-\frac{\psi_{it}}{q\lambda E_m}\right) t^{n'}$$

(2.14)

where  $Q_i$  is the inversion charge,  $\psi_{it}$  is the trap generation energy and the time exponential constant n' is 0.45.

#### 2.2.4 Time-Dependent Dielectric Breakdown

<u>Time-Dependent Dielectric Breakdown (TDDB)</u> is a reliability issue of the transistor gate oxide. As the technology scales, the thinner gate oxide and the stronger electric fields across the gate oxide can damage the oxide in such a way that the transistor gate current increases, resulting in a totally loss of the isolating property of the gate oxide [WSH00].

There are two types of the dielectric breakdown: soft break down (SBD) and hard break down (HBD). Depending on the number of positions where an increased local gate current occurs, SBD manifests itself as an increase of the leakage current. When the number of such positions and the resulting random traps inside the oxide reache a certain limit, HBD occurs such that the oxide isolating property is completely lost and a percolating path through the oxide will short the gate to the substrate, resulting in a transistor failure [GDWM<sup>+</sup>08]. The time to HBD can be modeled by a Weibull distribution.

As pointed out in [AWS02], the breakdown of oxides stressed at operating voltages (1.0V-1.5V) can "never be" hard. In addition, authors in [AVK08] show that as supply voltage reduces, the transistor can maintain functional under several SBD paths in the oxide. The positions of SBD paths in the oxide have significant influence here.

#### 2.2.5 Electromigration

Electromigration problem is the reliability issue of the on-chip interconnects [TR07]. In modern technologies, the on-chip interconnects are very thin and narrow. Such a small cross section area of the interconnects will increase the current density that flows through it, which means a movement of a huge amount of electrons. The electron movements then can interact with the metal ions in the interconnects and replace them. As a result, "voids" and "hillocks" are formed in the interconnects. The former, a vacancy area of metal ions, can cause open circuit, or in other words extremely large resistance in the interconnects, corresponding to a failure event, while the latter, locally accumulated metal ions, can cause short circuit between neighboring interconnects, resulting in a malfunction of the circuit.

Electromigration is a reliability effect that must be taken care of during layout phase. Certain interconnects must be widened where current will be high in the operation. Some special layout techniques, such as Slotted Wires, can be applied as well [Lie06].

## 2.3 State of the Art

#### 2.3.1 Reliability Simulation

Starting from the early 1990's, microelectronic system reliability problems, such as HCI, TDDB, raised due to the rapid advances of fabrication technologies and the emerging VLSI circuits at that time. Several reliability simulators based on software programs were proposed in academia as well as in industry to help the designers gain more insights into their design quality.

- Sheu *et al.* from the University of Southern California, proposed the simulator RELY [SHL89], which simulated the HCI effects based on the substrate current model.

- Leblebici *et al.* from the University of Illinois at Urbana-Champaign proposed a simulation framework considering the dynamic behaviors of HCI, by solving of a set of differential equations at *t* to obtain the interface trap densities and thus the transistor damage at that time [LK89].

- Hu *et al.* from the University of California at Berkeley proposed the reliability simulation tool BERT [Hu92], which enclosed several modules for different aging effects.

- From industry side, Texas Instruments proposed HOTRON [AHY87] for HCI effects simulation. Philips (later known as NXP) proposed PRESS [LWM<sup>+</sup>93] for HCI effects simulation.

Entering early 2000's, with the ever shrinking of the device feature size and the emerging of new aging effects such as NBTI, the reliability modeling and simulation again attracted the attention from various communities. [LMM06] presented the recent available EDA tools to simulate the HCI, NBTI and Electromigration effects.

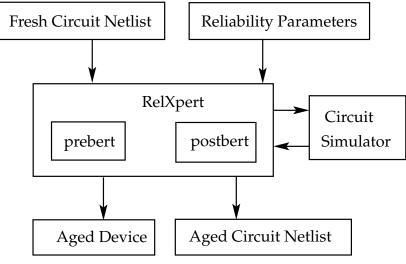

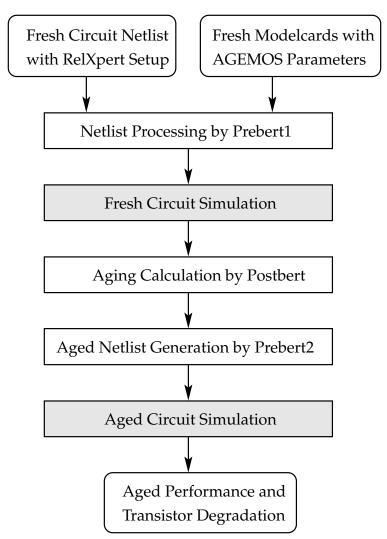

- One of the major commercial tool RelXpert from Cadence Design Systems based on BERT was presented in [LMM06]. The general workflow of RelXpert is shown in Figure 2.4. The prebert and postbert are the internal processors during the aging simulation. The detailed aging simulation using RelXpert is presented in Section 4.3.1.

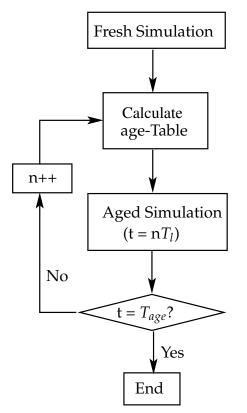

- The implementation of HCI simulation in another commercial simulator Eldo from Mentor Graphics was described in [KFHR01], where the new .AGE command calls repetitive simulations to obtain an accurate prediction of the circuit degradation with dynamic operating conditions. The workflow of such repetitive simulations is shown in Figure 2.5. Inside such a flow, the target time point

Figure 2.4: General workflow of RelXpert

$T_{age}$  is divided into *n* smaller intervals  $T_l$ . The circuit is simulated at the end of each time intervals, such that the gradual change of bias conditions as a result of the transistor degradation can be simulated.

- The simulator ARET from Georgia Institute of Technology was presented in [XCS<sup>+</sup>03]. It can handle HCI and Electromigration simulations. For Electromigration effects, the probability of certain post-fabrication defects on interconnects are obtained based on statistical models.

- Li *et al.* from the University of Maryland introduced another reliability simulator MaCRO in [LQH<sup>+</sup>06]. MaCRO can simulate HCI, NBTI and TDDB by substituting the degradation-sensitive transistors with failure-equivalent circuit models, such that a large number of circuit simulations on small time intervals can be avoided.

#### 2.3.2 Solutions towards Transistor Aging

There are several methods in literature trying to solve the transistor aging issue. They includes initial over-design [KKAR06], smart clock tree signaling [CGRP09], in-situ monitory circuitry [Die07], [QS08], as well as the using of chopper stabilization and autozeroing [MFCSL11].

• Authors in [KKAR06] propose a gate sizing algorithms for digital circuits to initially over-design the circuits. They first calculate the  $V_{th}$  degradation for each transistor assuming signal probability for the gate inputs. Then they size the

Figure 2.5: Repetitive simulation workflow of ELDO

gates assuming the intended lifetime and the calculated  $V_{th}$  degradation, thus achieving a degradation-aware gate sizing. As pointed out by various communities, over-design is straightforward to account for reliability issues. The over-design solutions rely on efficient algorithms to minimize the area overhead while achieving the expected product lifetime reliability.

- Authors in [CGRP09] propose design techniques with low overhead to overcome the NBTI induced skew degradation of clock tree, using a so-called Gating with Both Logic Value (GBLV) scheme. They observe that the PMOS transistors in clock buffers experience alternating stress and recovery stages of NBTI during switches of the clock signal in every cycle. The PMOS transistors in gated clock trees, on the other hand, do not experience such alternating cycles, since that part of the clock tree is shut down by the clock-gating. They generate an auxiliary signal AUX alternating between low and high values, thus balancing NBTI degradations among various clock buffers.

- Authors in [Die07] review the idea of applying additional monitors to the circuits and additional knobs to countermeasure the degradation and other side effects.

The solution can be in both circuit level down to hardware and system level up to intelligent software algorithms to control the circuit behaviors.

- Authors in [QS08] propose an in-situ monitor circuitry to track the effects of NBTI and mitigate the degradation in real time using an adaptive body biasing scheme by forward-biasing the PMOS transistors under stress. Applying the output voltage of the monitor circuitry directly to the body of the PMOS transistors under stress, the tolerance of  $\Delta V_{th}$  increases in comparison to a PMOS transistor with body connected to *Vdd* as in normal cases. The deploying of such monitor circuitry, however, turns out to be another trade-off between the additional layout area and the measurement accuracy, since it is impossible to deploy the monitor for each PMOS transistor under stress. In practice one monitor circuitry is allocated for a group of neighboring transistors to reduce area overhead and the influence of local process variations.

- Authors in [MFCSL11] apply chopper stabilization and autozeroing to reduce the effects of transistor aging on circuit level. The methods were originally developed to reduce the offset and low frequency noise. By applying chopper stabilization, the input low frequency noise can be shifted to high frequencies which locate outside the baseband, and the input differential pair are stressed equally resulting in a symmetrical degradation of the transistor pair. By autozeroing technique, on the other hand, the total stress time of the input pair is reduced by one half, since the amplifier operates in close and open loop in an alternative manner.

None of these solutions considers also the manufacturing process variations. Their methods rely only on the nominal value of circuit parameters, which cannot ensure a robust design over process variations.

#### 2.3.3 Design Centering considering Process Variations

On the other hand, considering process variation effects only, design methodologies towards a robust design tolerant of such process variations have been widely studied during the last 30 years. In these so-called design centering problems, an optimal set of circuit parameters are assigned to optimize the yield for an assumed statistical distribution of process variations. The approaches of design centering can be classified into two categories: statistical methods and deterministic methods.

#### 2.3.3.1 Statistical Methods

The feature of the **statistical methods** is the statistical yield analysis using Monte-Carlo simulations [HH64], [Sch66]. The necessary information about the circuit is

collected through those simulations. Based on the Monte-Carlo analysis result of the yield value, the yield can be optimized with the formulations of its gradient and Hessian matrix with respect to the statistical parameters. A variety of techniques and methods concerning the efficiency of Monte-Carlo analysis as well as the statistical yield enhancements are proposed.

Importance sampling [SSG97] is a technique using a different sampling distribution from the statistical parameter distribution to estimate the yield with improved estimation quality. It is applied widely in several methods such as [HLT83], [STPW76], [SP81] and [SR85].

- Authors in [HLT83] propose a stratified sampling method, where the Monte-Carlo simulations are performed in several disjoint subregions of the original parameter perturbation region. The total sample size is reduced by emphasizing the samples in the region where the performance specifications are met. This method is similar to a regionalization method proposed by authors in [STPW76].

- Authors in [SP81] propose a parameter sampling method, where the information in a single run of Monte-Carlo simulation is reused to derive several yield estimations before being updated.

- Authors in [SR85] propose a control variate technique consisting basically two Monte-Carlo experiments. First a control run is done consisting a small number of samples, used to estimate the yield difference between the main circuit and its simulation-cheaper shadow model. Then an auxiliary run with a larger sample size is done to estimate more accurately the yield of the shadow model. The yield of the main circuit can thus be obtained by the results of these two Monte-Carlo analysis.

Another category of the statistical approaches is the statistical experiment-based, such as response surface method. The basic idea is to build up a quadratic model of the circuit performance, and fit the model parameters via a number of samples on the response surface of the circuit. Such model then can replace the original circuit in simulations for a fast yield estimation and enhancement.

- Authors in [YKHT87] propose an average mean-squared error criterion to select an optimal set of circuit simulations in order to derive an accurate performance model.

- Authors in [PH93] develop a statistical regression procedure to estimate the response function of the circuit performances, where the higher order terms are added selectively to improve the accuracy. The yield is then maximized by pseudo objective function substitution method (POSM).

- More recently, authors in [LFJG09] propose a new stop criterion during the evolutionary computation based yield optimization to reduce the number of iterations. They monitor both the average improvement in the whole population of samples and the improvement in the best objective function value. The former part is important especially at the beginning of the algorithm to avoid wrong detection, while the latter part is important especially at the final stage of the algorithm to better locate the local optimal.

- Authors in [LFG10] further reduce the computational effort in each iteration by allocating the computing budget to each candidate in the population in an optimized manner. They identify those critical candidate solutions through an ordinal optimization problem, allocating enough number of samples to the Monte-Carlo simulation of these solutions, in comparison to the few samples allocated to non-critical solutions.

The advantages of the above-mentioned statistical methods are the yield estimation accuracy in comparison to the deterministic methods discussed below. The main drawbacks of the statistical methods include the high simulation efforts, which are reduced for the deterministic methods discussed below.

#### 2.3.3.2 Deterministic Methods

The **deterministic methods**, as its name implies, optimize the yield by approximating and maximizing the acceptance regions, or by building up and maximizing the robustness measures, in a deterministic manner, i.e., based on sensitivities calculation in stead of a number of random samples as in the statistical methods. Then design centering is performed such that either the center of the approximated acceptance region is found, or the robustness measures are maximized.

The acceptance region is defined either on the performance space or parameter space, where the part of the circuit realization after manufacturing process can meet all performance specifications. The exact definition and formulation is detailed later in Chapter 3. Authors in [BGT81] propose the ellipsoidal method, where the yield is maximized by maximizing the volume of the ellipsoid that is inscribed by the acceptance region. Since the acceptance region itself is nonlinear in most cases, its shape is too difficult to determine. So several other papers make simplification for the shape of the acceptance region.

• Authors in [SPV99] use advanced first-order second moment (AFOSM) method to approximate the yield, where the acceptance region is approximated by a polyhedral. The yield is maximized by finding the maximum-volume norm body

contained in the approximated polytope. The authors also propose a unified framework for different design centering task such as tolerance design, worst-case disign, process design, etc., by selecting appropriate norms.

- Authors in [WVO97] replace the single ellipsoidal approximation of the acceptance region by piecewise second-order functions, so-called piecewise ellipsoidal approximation (PEA). The second-order derivative of the constraint is from the boarder region, i.e., the ellipsoid that matches the constraint region. Then, this information is inserted into the second-order Taylor series expansion in the neighborhood of the nominal value. They show this mixed construction is accurate for yield optimization problem.

- Authors in [PSV01] approximate the acceptance region by a general polytope. The yield is then optimized using convex programming approach with an estimation of the yield gradient.

- Authors in [DH77] approximate the acceptance region by a simplex, the number of which is extended in every iteration during yield optimization. The yield is then optimized by finding of the center of the largest hypersphere inscribed into the convex hull of all approximating simplex.

- Authors in [AMHH99] improve the speed of convergence of the ellipsoidal technique by using double-sided ellipsoidal section. The double-sided ellipsoidal is bounded by two hyperplane, the first of which is built up by linearization of the acceptance region boundary at one boundary point, the second of which is found by determining a boundary point at which the gradient of the boundary of the acceptance region is opposite to that of the first hyperplane.

The other type of deterministic optimization methods is building up and maximizing certain robustness measures.

• Authors in [AGW94] propose the formulation of the worst-case distance, which is defined to be the distance between a performance specification and the mean value of that performance in terms of a number of standard deviations. The standard deviation of a performance is formulated by the attributes of statistical parameters which have underlying statistical distribution during manufacturing process. The analysis and optimization of worst-case distances thus are equivalent to the analysis and optimization of the circuit robustness over process variations. A sequential quadratic programming approach is proposed in [Sch03] to solve that optimization formulation. This thesis further extends the idea of the worst-case distance into the time domain. The methodologies of analysis and optimization considering the aged worst-case distance after transistor aging are proposed. The first- and second-order sensitivities of the worst-case distance over

time are derived for the first time, enabling a quick prediction of the aged worstcase distance based on Taylor expansion.

- Authors in [KD95] use a linearized performance penalty (LPP), which is the performance model linearized over the mean value of the statistical parameters. The evaluation of such model requires only one circuit simulation without using an iterative optimization algorithm, with a trade-off over the accuracy.

- Authors in [DK95] optimize the worst-case performance to increase the total yield, where the performance is built up by a response surface model. It is not exactly a design centering approach, but a method to find a design with predefined worst-case performance, i.e., the worst-case robustness.

- Authors in [AS94] and [DG98] make use of the capability indices C<sub>p</sub> and C<sub>pk</sub>, which originate from process control. C<sub>p</sub> measures how "narrow" the performance distribution is (the variability part), while C<sub>pk</sub> measures the distance between the mean value and the most critical performance specifications (the centering part). Their methods are based on new target functions, combining the above two indices, such that the variability can be minimized and design can be centered. The method in [AS94] builds up response surface models for the performances, while the method in [DG98] makes symbolic equations for the performances.

#### 2.3.4 Joint Effects of Transistor Aging and Process Variations

It is only since very recent years that the joint effects of process variations and lifetime parameter degradations are studied [AKPR07]. A various of solutions are proposed in literature. They differ in the type of reliability effects considered and the type of circuits studied.

For digital circuits, NBTI-aware statistical timing analysis considering process variations are proposed in [VOXW09], [VOX09], [WRY<sup>+</sup>08] and [LSZ<sup>+</sup>09].

- Authors in [VOXW09] build up a gate-level delay fall-out model by propagating the device parameter fall-out model due to NBTI and process variations into the gate delay model. To study the joint effects on the circuit level with multiple gate stages, they use HSPICE based Monte Carlo simulations. They consider in addition the intrinsic variations of NBTI process in [VOX09]. A sizing methodology considering the joint effects is not covered in their works.

- Authors in [WRY<sup>+</sup>08] propose a statistical prediction methodology considering process variations and transistor aging due to NBTI. They study the joint effects on gate level delay by applying the transistor level aging model into a process

variation-aware gate delay model. Then they are able to model the timing behavior of a single path considering the joint effects. No sizing solution is proposed in their work either.

• Authors in [LSZ<sup>+</sup>09] build up an NBTI-aware statistical gate delay model using the stochastic collocation method. They apply their model also into the circuit level statistical timing analysis considering various working conditions of the circuit in runtime. Then they propose a sensitivity analysis framework based on their NBTI-aware circuit level statistical timing analysis, such that the critical gates can be identified and optimized during circuit sizing.

All of those methods rely on the analytical expression of performance features such as delay time, which is suitable for digital circuits but difficult in analog domain.

For analog circuits, various methodologies on the investigation and mitigation of the joint effects are proposed in [MG09], [MG10], [MG11], [MDJG12] and [CMFSL11a].

- Authors in [MG09] use Monte-Carlo simulation loop to obtain the degraded performance values for each fresh random sample at every lifetime point. Then the most appropriate distribution function at each time is fitted, thus a failure distribution throughout the lifetime can be found. It results in a high simulation effort and difficulty for further optimization.

- They improve their method in [MG10] using a response surface model to speed up the simulations, where certain numbers of random samples are still required to obtain the degraded distribution information. They verify that an initial overdesign can improve the lifetime robustness of the circuits. However, a quantified solution is not available from their work to guide the circuit sizing process. The temporal stochastic reliability effects are considered in addition in [MG11] using a similar methodology.

- In [MDJG12], the authors further speed up the simulation on large analog and mixed-signal systems by partitioning of the large system into smaller manageable subblocks. They use fast function extraction symbolic regression method to cope with the high number of dimensions and the nonlinear circuit behavior. An active learning sample selection algorithm is proposed to select optimal model training samples and to limit the amount of expensive aging simulations. No sizing solution is considered either.

- Authors in [CMFSL11a] propose another technique to suppress the effects of aging and process variations on analog circuits. Firstly a Burn-In phase is applied where the asymmetric open-loop stress conditions are switched into symmetric stress to control the BTI effect in saturation. The symmetric stress is generated by switching the asymmetric input stress with a 10Hz clocking frequency. Secondly

a Calibration phase is applied where a selective asymmetric stress is applied to transistors to compensate the offsets caused by process variations. The proposed technique allows smaller device dimensions be used in the design, since offsets can be calibrated after manufacturing.

## 2.4 Summary

The reliability issues from manufacturing process variations and transistor aging are discussed in detail. These have been the major concern for both circuit design and chip manufacturing communities for decades, since these will result in yield loss and extra redesign costs.

Most of the previous research consider these reliability problems separately. Although there are proposals in solutions towards transistor aging or process variations alone, it is only since recent years that the studies on the joint effects appear. The state-of-the-art studies on the joint effects concentrate on digital circuits, where device parameter variations and aging can be propagated into gate level or circuit level performance formulations. For analog counterparts, the studies are still limited and no sizing solutions are available.

This thesis will study the joint effects of manufacturing process variations and transistor degradation related lifetime circuit reliability in detail, with proposal of new models and new design methodologies for analog circuits.

# **Chapter 3**

# **Problem Formulation**

This chapter formulates the problem studied in this thesis and gives formal definition of terms used throughout the thesis.

### 3.1 Age and Lifetime

In this section, the differentiation between two terms which are used throughout the thesis, *age* and *lifetime*, is discussed.

Literally, *age* is defined as "length of time that a person or organism has been alive; length of time that an object has existed", while *lifetime* is defined as "span of a person's life, time during which a person is alive; period of time during which something functions or exists". So for a single person or an object, the value of age is always less or equal to the value of lifetime, since the lifetime refers to the whole length of the functioning period of that person or object.

Similarly, in this thesis, age and lifetime are defined as follows.

First, age, denoted by t, is any point of interest on the time axis. Especially,  $t_0$  corresponds to the time when the circuit is just manufactured without any transistor aging. It can be called as fresh circuit.

Second, given a minimal acceptable yield value,  $Y_{min}$ , the lifetime, denoted by  $T_{life}$ , is the time when the aged yield value  $Y(T_{life})$  of a circuit products drops to  $Y_{min}$ . In other words, at  $T_{life}$ , we have

$$Y(T_{life}) = Y_{min} \tag{3.1}$$

The choosing of  $Y_{min}$  will influence the lifetime  $T_{life}$  of a circuit products, since the aged yield is a decreasing function over time. If the predefined acceptable  $Y_{min}$  drops, the product's lifetime will be longer.

Note that the value of  $T_{life}$  can be smaller than, equal to or bigger than the value of t, since  $T_{life}$  needs a predefined  $Y_{min}$  as an input criteria. In our study t is chosen for any point of interest without a direct indication of the value of  $T_{life}$ .

Sometimes people say "lifetime yield", which has the same meaning as "aged yield", i.e., the yield value of an aged circuit. To avoid any misunderstanding, the term "aged yield" is used throughout the thesis.

## 3.2 Parameters

Parameters of a circuit include all of the contributing factors which influence the behavior of that circuit. These factors can be fixed values, or random variables. They can be from the circuit itself, or from the operating environment. They can drift from their nominal values over time, or remain to be the same amount after manufacturing process.

The circuit parameters can be classified into three categories:

- Design parameters, represented by a vector  $\mathbf{d} \in \mathbb{R}^{n_{\mathbf{d}}}$

- Statistical parameters, represented by a vector  $\mathbf{s} \in \mathbb{R}^{n_{\mathbf{s}}}$

- Operating parameters, represented by a vector  $\boldsymbol{\theta} \in \mathbb{R}^{n_{\boldsymbol{\theta}}}$

In addition, if time-dependent parameter drifts are considered, as discussed in Section 2.2, some of the parameters will be a function of age *t*. Detailed definition and discussion are as follows.

### 3.2.1 Design Parameters

The *design parameters*  $\mathbf{d} = [d_1, d_2, \dots, d_{n_d}]^T \in \mathbb{R}^{n_d}$  correspond to the circuit parameters that the designer can choose during the design phase in order to obtain an "optimal" design. The examples of design parameters in CMOS circuits are transistor widths and lengths, nominal values of capacitors and resistors.

For each of these design parameters, there are correspondingly lower and upper bounds. Usually a lower bound is defined by the manufacturing technology, minimal grids, for example, while an upper bound may arise from the limit of the maximal available on-chip area. These boundary values can be combined as vectors:  $\mathbf{d}_L$  for the lower bounds and  $\mathbf{d}_U$  for the upper bounds. Thus a *design parameter space*  $\mathcal{D}$  is formed, bounded by an  $n_{\mathbf{d}}$ -dimensional hypercube:

$$\mathcal{D} = \{ \mathbf{d} | \mathbf{d}_L \le \mathbf{d} \le \mathbf{d}_U \} \tag{3.2}$$

In Equation (3.2) and the rest of the thesis, the vector inequality is defined as follows. Assume two vectors  $\mathbf{x}, \mathbf{y} \in \mathbb{R}^{n_x}$ ,

$$\mathbf{x} \le \mathbf{y} \Leftrightarrow \underset{i=1,\dots,n_{\mathbf{x}}}{\forall} x_i \le y_i \tag{3.3}$$

Since either the transistor dimensions or the capacitor and resistor values will not change after manufacturing process, we accept the fact that, design parameters **d** will not drift over time. They can only be changed during the design phase, before the manufacturing process starts. Note that for those manual layout designers, the widths and lengths of on-chip interconnects are also designable and may suffer from time-dependent reliability problem, such as Electromigration (EM). But these effects are beyond the scope of this thesis. For more complete discussion of on-chip interconnects reliability problem please refer to [Bla69], [TR07].

#### 3.2.2 Statistical Parameters with Aging

Corresponding to the uncertainty and imperfectness of the manufacturing process, the *statistical parameters*  $\mathbf{s} = [s_1, s_2, \dots, s_{n_s}]^T \in \mathbb{R}^{n_s}$  model the variations during the manufacturing, as introduced in Section 2.1. Such variations can be captured usually by a statistical distribution. In most cases, the probability density functions (pdf) of the statistical parameter distributions are considered.

The types of the statistical distributions vary for different statistical parameters. For example, Normal (Gaussian) distribution for the threshold voltage  $V_{th}$ , lognormal distribution for the oxide thickness  $t_{ox}$ , etc [Ml95]. These distributions can be transformed into Gaussian distribution as shown in [Esh92]. So without loss of generally, the Gaussian distribution are assumed for the statistical parameters throughout the thesis.

For one statistical parameter  $s_i$ ,  $i = 1, ..., n_s$ , it follows Gaussian distribution with mean value  $s_{i,0}$  and standard deviation  $\sigma_i$ . Such distribution can be denoted as

$$s_i \sim \mathcal{N}(s_{i,0}, \sigma_i^2) \tag{3.4}$$

The probability density function of  $s_i$  is given by

$$pdf(s_i) = \frac{1}{\sqrt{2\pi\sigma_i}} \cdot \exp\left(-\frac{(s_i - s_{i,0})^2}{2\sigma_i^2}\right)$$

(3.5)

For a vector **s**, the  $n_s$ -dimensional Gaussian distribution with mean vector  $\mathbf{s}_0$  and covariance matrix **C**, denoted by  $\mathbf{s} \sim \mathcal{N}(\mathbf{s}_0, \mathbf{C})$ , has the probability density function as follows:

$$pdf(\mathbf{s}) = \frac{1}{\sqrt{2\pi}^{n_{\mathbf{s}}} \cdot \sqrt{\det \mathbf{C}}} \cdot \exp\left(-\frac{1}{2} \cdot (\mathbf{s} - \mathbf{s}_0)^T \cdot \mathbf{C}^{-1} \cdot (\mathbf{s} - \mathbf{s}_0)\right)$$

(3.6)

The level contours of the pdf(**s**) are ellipsoids:

$$(\mathbf{s} - \mathbf{s}_0)^T \cdot \mathbf{C}^{-1} \cdot (\mathbf{s} - \mathbf{s}_0) \equiv \beta^2(\mathbf{s})$$

(3.7)

where the covariance matrix **C** is defined by

$$\mathbf{C} = \mathbf{\Sigma} \cdot \mathbf{R} \cdot \mathbf{\Sigma}$$

(3.8)

$$= \begin{bmatrix} \sigma_1^2 & \sigma_1 \sigma_2 \rho_{1,2} & \cdots & \sigma_1 \sigma_{n_s} \rho_{1,n_s} \\ \sigma_2 \sigma_1 \rho_{2,1} & \sigma_2^2 & \ddots & \vdots \\ \vdots & \ddots & \ddots & \sigma_{n_s-1} \sigma_{n_s} \rho_{n_s-1,n_s} \\ \sigma_{n_s} \sigma_1 \rho_{n_{s,1}} & \cdots & \sigma_{n_s} \sigma_{n_s-1} \rho_{n_s,n_s-1} & \sigma_{n_s}^2 \end{bmatrix}$$

(3.9)

The matrix  $\Sigma$  has all of the non-negative standard deviations  $\sigma_i$  for every component of vector **s**

$$\boldsymbol{\Sigma} = \begin{bmatrix} \sigma_1 & 0 & \cdots & 0 \\ 0 & \sigma_2 & \ddots & \vdots \\ \vdots & \ddots & \ddots & 0 \\ 0 & \cdots & 0 & \sigma_{n_s} \end{bmatrix}$$

(3.10)

The matrix **R** has all of the correlations  $\rho_{i,j}$  between the *i*-th and the *j*-th component of vector **s**

$$\mathbf{R} = \begin{bmatrix} 1 & \rho_{1,2} & \cdots & \rho_{1,n_{s}} \\ \rho_{2,1} & 1 & \ddots & \vdots \\ \vdots & \ddots & \ddots & \rho_{n_{s}-1,n_{s}} \\ \rho_{n_{s},1} & \cdots & \rho_{n_{s},n_{s}-1} & 1 \end{bmatrix},$$

(3.11)

where

$$\rho_{i,j} = \rho_{j,i} \tag{3.12}$$

$$-1 \le \rho_{i,j} \le +1 \tag{3.13}$$

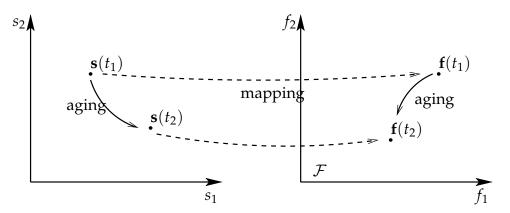

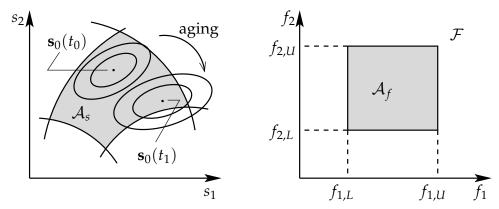

When the transistor aging effects are taken into consideration, certain statistical parameters, such as  $V_{th}$ , will shift their values over time, as introduced in Section 2.2. Thus the vector of statistical parameter can be denoted as a function of age t with aged mean vector  $\mathbf{s}_0(t)$  and aged covariance matrix  $\mathbf{C}(t)$  as:

$$\mathbf{s}(t) \sim \mathcal{N}(\mathbf{s}_0(t), \mathbf{C}(t)) \tag{3.14}$$

whose probability density function at that time is

$$pdf(\mathbf{s}(t)) = \frac{1}{\sqrt{2\pi^{n_{\mathbf{s}}}} \cdot \sqrt{\det \mathbf{C}(t)}} \cdot \exp\left(-\frac{1}{2} \cdot (\mathbf{s}(t) - \mathbf{s}_0(t))^T \cdot \mathbf{C}(t)^{-1} \cdot (\mathbf{s}(t) - \mathbf{s}_0(t))\right),$$

(3.15)

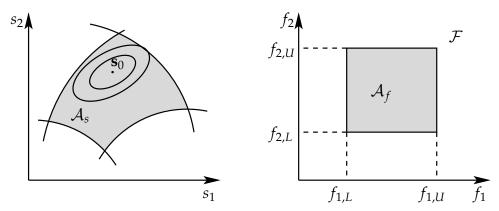

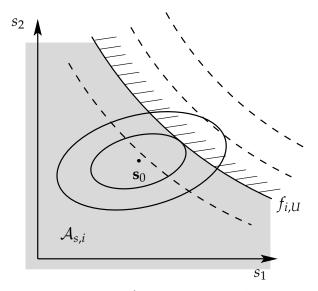

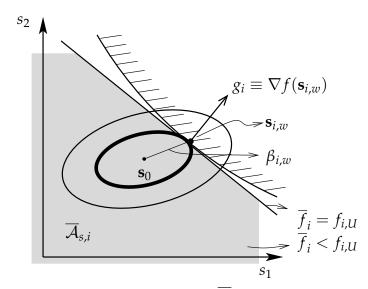

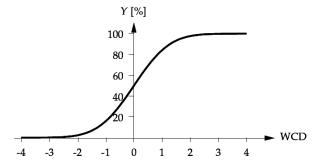

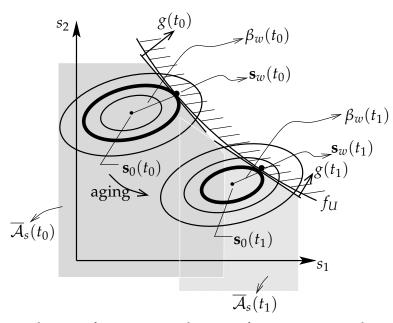

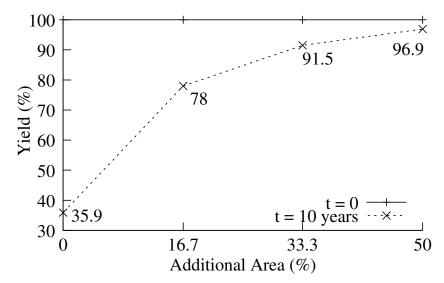

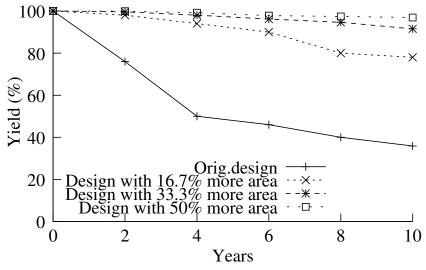

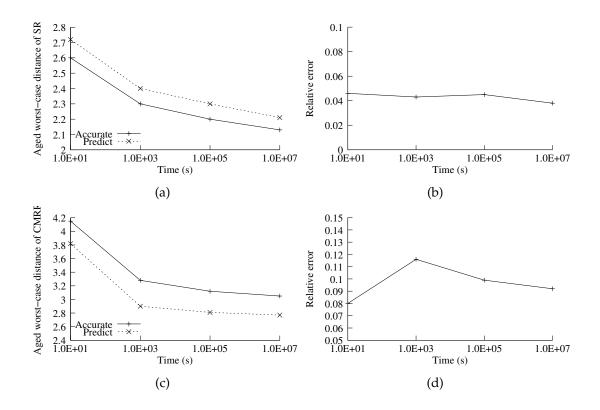

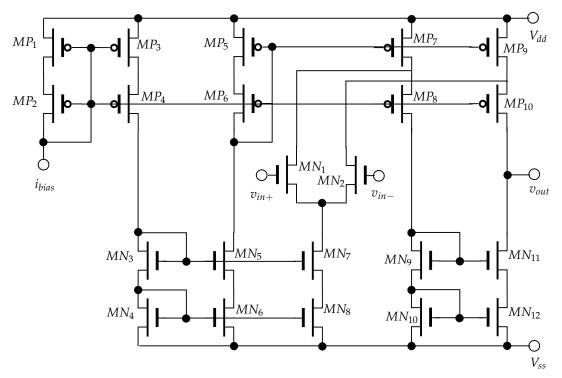

with the level contours as: