Lehrstuhl für Technische Elektronik der Technischen Universität München

# Parametric Reliability of 6T-SRAM Core Cell Arrays

### Stefan Drapatz

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Georg Sigl

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

- 2. apl. Prof. Dr.-Ing. habil. Walter Stechele

Die Dissertation wurde am 14.10.2011 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 7.02.2012 angenommen.

# Summary

The increasing integration density of microelectronic circuits in combination with nonconstantly scaled supply voltages results in higher electric fields in MOS transistors. This is one central source of several aging mechanisms, some of them shifting the parameters of MOS transistors during lifetime. These parametric degradation effects can be separated in two groups called 'Bias Temperature Instability' (BTI) and 'Hot Carrier Injection' (HCI). This work focuses on the impact of these degradation mechansisms on 6-Transistor Static Random Access Memory (SRAM) arrays in 65 nm low power CMOS technology.

First, some basic information is provided about SRAM cell functionality, key performance metrics, reliability and the four parametric degradation mechanisms covered in this work. Then, the sensitivity of the SRAM core cell to each degradation mechanism is simulated. Together with the effective device degradation under normal SRAM operations in real life, this results in the information about the impact of each mechanism. BTI for pMOS transistors, called Negative BTI (NBTI), could be identified as the main problem in actual 65 nm low power technology with conventional  $SiO_2$  gate dielectrics.

NBTI shows strong variation- and recovery-effects, which both are not fully understood, although this degradation mechanism has been known for approx. 30 years. This is why there are no sufficient simulation models so far, thus, measurements have to be performed to do the step from single cell simulation to SRAM array conclusions.

Consequently, a major focus of this work is to develop unconventional new measurement techniques. Contrary to state-of-the-art methods they are faster, do not need dedicated test chips which do not represent mass product design, do not need highly accurate V-I measurements and therefore can be used in-field in products with the only precondition of dual- $V_{DD}$  power routing.

By using these new techniques, the impact of the worst degradation mechanism NBTI was examined directly on large-scale SRAM arrays. Especially the fast-recovering component of NBTI was directly measured on SRAM array stability for the first time. Thus, it could be shown which use-cases are critical to provide long lifetimes, which is the first step to fight the impact of parametric degradation mechanisms.

Finally, a comparison of known countermeasure techniques was performed in order to choose the most promising methods.

# Contents

| Su       | imma | ary                                                        | i         |

|----------|------|------------------------------------------------------------|-----------|

| Ι        | In   | troduction and Background                                  | 1         |

| 1        | Intr | oduction                                                   | 3         |

|          | 1.1  | Technology Scaling: Benefits and Challenges                | 4         |

|          | 1.2  | Scaling of SRAM: Motivation for this work                  | 5         |

|          | 1.3  | Outline and Contributions of this work                     | 6         |

| <b>2</b> | SRA  | AM Fundamentals                                            | 7         |

|          | 2.1  | Functionality of the 6T-SRAM Core Cell                     | 9         |

|          | 2.2  | SRAM Performances and Figures of Merit                     | 10        |

|          | 2.3  | Summary                                                    | 19        |

| 3        | Deg  | radation and Reliability                                   | <b>21</b> |

|          | 3.1  | Quality, Yield, Variations and Redundancy                  | 21        |

|          | 3.2  | Reliability Basics                                         | 22        |

|          | 3.3  | Physics-of-Failure Concept                                 | 25        |

|          | 3.4  | Parametrical Degradation Mechanisms                        | 26        |

|          | 3.5  | Negative Bias Temperature Instability (NBTI)               | 28        |

|          | 3.6  | Positive Bias Temperature Instability (PBTI)               | 33        |

|          | 3.7  | Hot Carrier Injection (HCI) and Non-conducting HCI (NCHCI) | 35        |

|          | 3.8  | Accelerated Stress Measurements                            | 38        |

|          | 3.9  | Summary                                                    | 39        |

| Π        | Ρ   | arametric Degradations on 6T-SRAM Core Cells                           | 41  |

|----------|-----|------------------------------------------------------------------------|-----|

| 4        | Sim | nulations of the four Parametric Degradation Mechanisms                | 43  |

|          | 4.1 | Voltage and Current in each Transistor                                 | 43  |

|          | 4.2 | Negative Bias Temperature Instability                                  | 53  |

|          | 4.3 | Positive Bias Temperature Instability                                  | 56  |

|          | 4.4 | Hot Carrier Injection                                                  | 63  |

|          | 4.5 | Off-State Stress                                                       | 68  |

|          | 4.6 | NBTI plus PBTI                                                         | 69  |

|          | 4.7 | Conclusion                                                             | 73  |

| <b>5</b> | Sta | bility Analysis of SRAM Arrays                                         | 75  |

|          | 5.1 | State of the Art: SRAM Stability Analysis                              | 75  |

|          | 5.2 | New Approach                                                           | 76  |

|          | 5.3 | Simulation of Read Margin                                              | 76  |

|          | 5.4 | Experimental setup                                                     | 80  |

|          | 5.5 | Results                                                                | 84  |

|          | 5.6 | Discussion                                                             | 90  |

|          | 5.7 | Conclusion                                                             | 91  |

| 6        | Imp | pact of Recovering NBTI on SRAM Arrays                                 | 93  |

|          | 6.1 | State of the Art: Measure Recovering NBTI on SRAM Cells                | 93  |

|          | 6.2 | New Approach                                                           | 96  |

|          | 6.3 | Results                                                                | 101 |

|          | 6.4 | Plausibility checks                                                    | 103 |

|          | 6.5 | Temperature dependency of NBTI recovery                                | 110 |

|          | 6.6 | Determination of Read Margin Distribution directly after end of Stress | 111 |

|          | 6.7 | Conclusion                                                             | 113 |

| II       | I   | Countermeasures 1                                                      | 115 |

| 7        | Cοι | intermeasures                                                          | 117 |

| 7.1 | The different levels of countermeasures | . 117 |

|-----|-----------------------------------------|-------|

| 7.2 | Countermeasures against instability     | . 118 |

#### CONTENTS

|              | 7.3   | Countermeasures against NBTI- and PBTI specific $V_{th}$ drift | 123 |

|--------------|-------|----------------------------------------------------------------|-----|

|              | 7.4   | Comparison of countermeasure techniques                        | 126 |

|              | 7.5   | The best countermeasure techniques                             | 127 |

|              | 7.6   | Conclusion                                                     | 130 |

| 8            | Cor   | clusion and Outlook                                            | 131 |

| A            | ppe   | ndix                                                           | 135 |

| A            | Det   | ermination of Static Noise Margin SNM and Read N-Curve         | 137 |

| В            | Det   | ermination of Read Margin RM                                   | 138 |

| С            | Det   | ermination of Write Level or Write-Trip Point                  | 139 |

| D            | Det   | ermination of Write N-Curve                                    | 140 |

| $\mathbf{E}$ | Det   | ermination of Read Current $I_{read}$                          | 141 |

| $\mathbf{F}$ | List  | of Symbols and Abbreviations                                   | 142 |

| G            | Puł   | olications by the author                                       | 144 |

| Li           | st of | Figures                                                        | 147 |

| Bi           | bliog | graphy                                                         | 155 |

| Da           | anks  | agung                                                          | 160 |

# Part I

# Introduction and Background

# Chapter 1

# Introduction

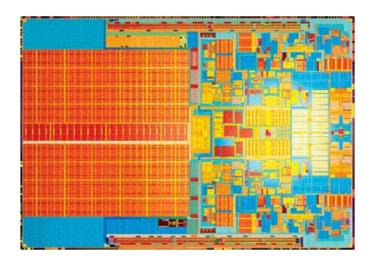

Static Random Access Memory (SRAM) nowadays is a dominant part of Systems-on-Chip (SoC). Up to about half of the die area and 2/3 of the transistor count of a modern microprocessor consists of SRAM cells. Fig. 1.1 shows the die photo of an Intel Penryn processor manufactured in 45 nm technology [www.intel.com]; the SRAM area can be identified on the left half of the die with its characteristic homogeneous layout style. 6 MB of SRAM Cache memory equals approx. 300 million transistors, which is 73% of the complete number of 410 million transistors.

Fig. 1.1: Intel Penryn Processor: about half of the die area and 2/3 of transistor count consist of SRAM, identifiable on the left half of the die [www.intel.com].

Systems on Chip will require more and more memory in the future. 90% of the die area are projected to be memory in the next 10 years [1]. Die area directly translates to cost. To get maximum memory capacity on smallest possible area, the two obvious main approaches are: 1. minimize transistor sizes, 2. densify transistor packaging. This is why SRAM has the smallest transistors and the highest transistor density of the whole chip. This work focuses on the behavior of SRAM cells made of minimum size transistors with special tight design rules with respect to parametric reliability issues.

## 1.1 Technology Scaling: Benefits and Challenges

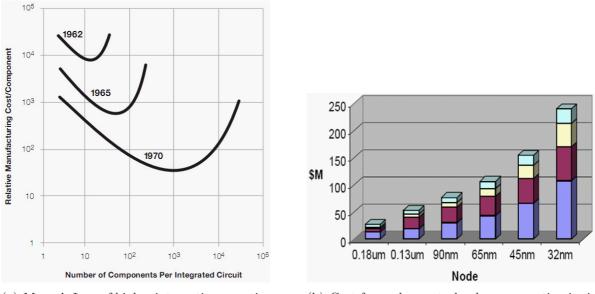

"The number of transistors incorporated in a chip will approximately double every 24 months" (Gordon Moore, Co-founder of Fairchild and Intel) [www.intel.com]. This quote, better known as "Moore's Law" from 1965, has just celebrated its 45th anniversary and is still valid. It is motivated from the falling cost per transistor on a chip when the integration density is ramped up (Fig. 1.2(a)). Increasing the number of transistors is feasible only by decreasing the size of each transistor. All 18 to 24 months, the length of one transistor is divided by  $\sqrt{2}$  and therefore the transistor count is doubled. While in 1970, the minimum transistor length was about 10 µm, in 2011 product development has reached 32 nm or even less.

(a) Moore's Law of higher integration over time is motivated from decreasing cost per transistor [2]

Fig. 1.2: Moore's Law and cost of new technology development

This 'law' could only last that long because, contrary to power semiconductors, the optimum transistor in information technology is a small device. Smaller transistors not only need less area and create less cost, but they are faster and have less energy consumption. This is why scaling in the last 4 decades had almost nothing but advantages, which is an unlike behavior for all kinds of engineering. Only in the last 10 years, the disadvantages are increasing.

First of all, the cost of development for each new technology generation is increasing dramatically (Fig. 1.2(b)). It is getting more and more difficult to produce tiny structures in the deca-nanometer regime, e.g. for lithography to create 32 nm structures with the actual 193 nm wavelength. Immersion layers are state of the art before the next step to Extreme Ultra-Violet (EUV) with 13 nm wavelength can be done. Actually, this technology has too low throughput to replace the well-known state-of-the-art lithography. This is why conventional lithography in combination with highly regular layout pattern is used.

Furthermore, the produced devices show more and more non-ideal behavior: short channel effects are increasing, so the small-signal output resistance  $r_{out}$  is reduced because of the slope in the output characteristics. Oxides are getting thinner to avoid decreasing transconductance  $g_m$ . But this increases subthreshold leakage, also because  $V_{DD}$  cannot be reduced as much as it should be in order to keep enough overdrive voltage ('nonconstant voltage scaling'). Also gate leakage increases: the thickness of gate oxide is in the range of some atomic layers now, which causes direct tunneling, and static power dissipation is going up. Another topic is variability: the small number of dopants in the channel results in high  $V_{th}$  distribution.

The two worst effects on circuit perspective in the last 10 years were leakage and  $V_{th}$  variability, and many approaches have been done to fight against both effects [3]: 1. high- $\kappa$  gate oxide materials and metal gate electrodes. 2. Bulk CMOS is replaced by Silicon-On-Insulator (SOI). 3. MuGFETs: multi-gate FETs, FINFETs.

But now, degradation effects are adding: With decreasing gate oxides, but almost constant  $V_{DD}$ , electric fields in the gate oxide increase. This is the motor for parametric degradation.

## **1.2** Scaling of SRAM: Motivation for this work

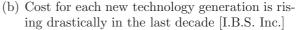

Volatile memory like SRAM has been one of the major driving forces for scaling in the last decades. This is because scaling has the greatest area effect on these high-density transistor structures, much more effect than for ordinary logic [4]. Fig. 1.3 shows the cell area shrink from 1995 till today including a view into the future until 2025 [1]. While in

Fig. 1.3: ITRS roadmap for volatile memory incl. SRAM from 1995 until 2025 [1] 1995, a 6T-SRAM cell had an area of  $20 \ \mu\text{m}^2$ , 2010 this got reduced to  $0.15 \ \mu\text{m}^2$ , which

is about 1%. But how do the already discussed challenges of further shrinking translate to SRAM? Shrinking the node size from 250 nm down to 50 nm divides the cell stability by a factor of 4 [4]. This is the first reason why technology scaling challenges the SRAM cells. ITRS sees the difficult challenge in SRAM scaling in 'maintaining adequate noise margins and control key instabilities and soft-error rate' [1].

Summing up, leakage, variability and stronger electric fields are the three major challenges in the ongoing transistor scaling. Since SRAM must provide as much memory as possible on minimum space, SRAM suffers most from the drawbacks of scaling:

- 1. Up to hundreds of millions of transistors are a huge multiplier for single transistor leakage. This is why SRAM is one of the worst leakage current sources in a SoC.

- 2. Variability is increasing with decreasing transistor size, following Pelgroms law [5]. This is why variability on SRAM with its minimum-size transistors is much worse than for digital (and of course analog) transistors.

- 3. Degradation due to high electric fields can affect the SRAM behavior. Degradation and variability are always combined, i.e. degradation never appears without variability. This will be in the focus of this work.

Yield and Reliability are going to be more and more critical from technical and economical point of view, this is why degradation has to be investigated on SRAM cells.

## **1.3** Outline and Contributions of this work

**Chapter 2** is about the functionality of 6-transistor SRAM cells as well as performance indicator metrics. Several metrics for the same performance exist, the advantages and disadvantages are discussed. Chapter 3 discusses the basics of yield, quality and reliability. Four actually known parametrical degradation mechanisms on transistor level are introduced. In **Chapter 4** the impact of the four parametric degradation mechanisms on the SRAM cell is simulated. It is examined in which modes the SRAM circuit fulfills which degradation conditions and how it reacts to degradations. Together, this can state how strong each degradation takes effect on the circuit. Additionally, a combination of degradation mechanisms is considered. Chapter 5 performs the step from the single SRAM cell to the SRAM array. It describes the newly developed method for fast analyzing stability of SRAM arrays. The impact of NBTI can be measured with this technique. Chapter 6 examines the recovering NBTI component and its measurement on SRAM arrays. This has never been done on SRAM cells before, because all existing measurement approaches were too slow. But the new technique developed within this work is able to measure this component. Chapter 7 is dealing with countermeasures to aged SRAM core cells. After only the impact of degradation on the memory cell was discussed so far, the focus now is on countermeasures. What can be done to achieve memory cells that are working correctly many years after production and usage? Chapter 8 is the conclusion followed by an outlook.

# Chapter 2

# **SRAM Fundamentals**

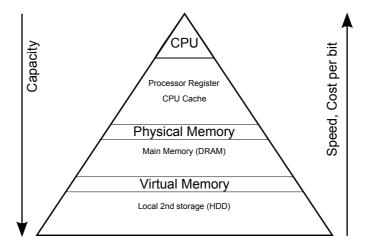

In computer memory hierarchy, the fast and small-capacity memory types are on top, while the slow and huge-capacity memories are at the bottom (Fig. 2.1). While disc

Fig. 2.1: Memory hierarchy of a Personal Computer (PC)

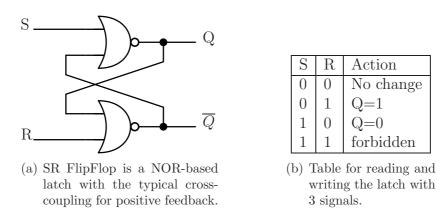

drives store Terabytes of data and have access time in the 10 ms region, main memory of DRAM type typically stores some Gigabytes but has a factor of  $10^{5}$ - $10^{6}$  faster access time of approx. 10 -100 ns. Most of these faster techniques are based on charging or discharging of capacitors, which takes some time for transportation of charge. Often they represent dynamic memories, which must be refreshed in fractions of a second to enable long storage time [6]. To further improve access time by a factor of 10 or more in order to get to the top of the memory hierarchy pyramid, the principle of positive feedback is used. No charge must be stored, positive feedback is a technique that brings a circuit to its extreme values and therefore realizes bistable systems. In case of memory those are the two binary states '1' and '0'; systems using this technique are called 'Flip-Flops'. SRAM, latches and registers are based on that principle: their killer feature is having extremely fast read and write access. Latches, which are level-sensitive and typically used to build sequential logic circuits, are often based on cross-coupled NAND or NOR gates, compare Fig. 2.2(a). Its advantage is the simple usage and asynchronous data interface, it can be easily read and written with 3 signals R, S and Q, compare Fig. 2.2(b). Q always keeps the stored information, and setting R or S to 1, while keeping the other signal at 0 resets or sets the latch. To build edge-triggered registers, the level-sensitive latch must be transformed to a synchronous circuit, which is adding some more transistors. So the disadvantage is the big area consumption: typically 10 to 30 transistors are required to store only one binary digit (bit).

Fig. 2.2: Simplest latch: asynchronous SR Flip-Flop which can be used to build sequential logic circuits [6].

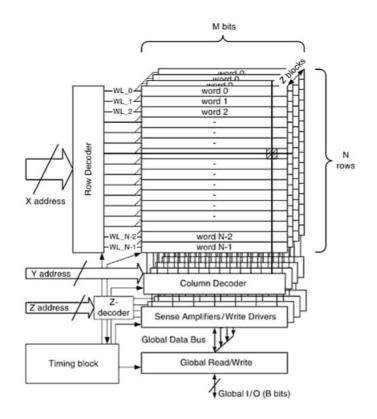

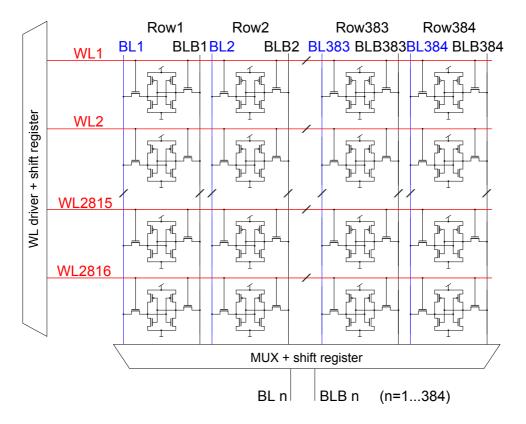

SRAM on the other hand needs a complex periphery to read or write a distinct cell in a huge array of core cells, compare Fig. 2.3 [7]. Reading and writing are complex procedures, which will be described in section 2.1. Due to the periphery overhead, SRAM cells do not make sense as single latch cells. So one SRAM cell never comes alone, the typical SRAM array size is at least some thousand to some millions of cells, which makes it a kBit or MBit array. Therefore SRAM is also a great test vehicle for variability examinations.

So the key performance of SRAM compared to all other memory types is speed: SRAM has about 1 ns read and less than 1 ns write access time. It is typically used inside a microcontroller for cache memory, which is divided in several, normally up to 3, speed or hierarchy levels. Level 1 cache is clocked with CPU frequency, which is some GHz. Therefore, a memory type with less than 1 ns access time is needed. This level nowadays normally has a size of 4 to 64 kB.

Level 2 is much bigger, about 64 kB to 12 MB. Sometimes it is not on the CPU itself, and it is always clocked slower, e.g. with some hundreds of megahertz.

For the advantage of high speed, one SRAM cell needs about 10 to 15 times more area than a DRAM cell [1], which directly translates to cost. One SRAM cell in 65 nm is about  $0.5 - 0.7 \,\mu\text{m}^2$ , the core cells examined in this work have a size between  $0.6 - 0.7 \,\mu\text{m}^2$ . To keep this area as small as possible, they are built with especially tight design rules. This is possible because of their regular layout. They allow to place more minimum size transistors than for conventional logic, so SRAMs do have special status in semiconductor manufacturing.

#### 2.1. FUNCTIONALITY OF THE 6T-SRAM CORE CELL

Fig. 2.3: SRAM block diagram showing the core cell array and the periphery containing row/column decoder and sense amplifier taken from [4]

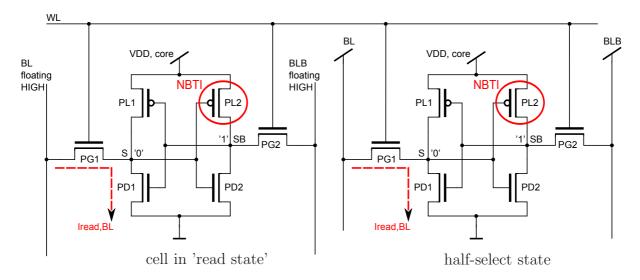

## 2.1 Functionality of the 6T-SRAM Core Cell

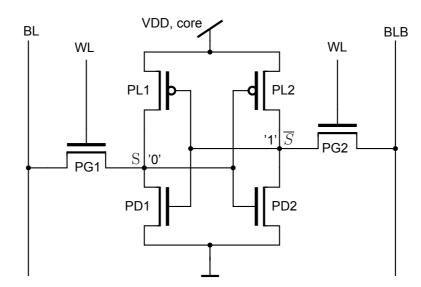

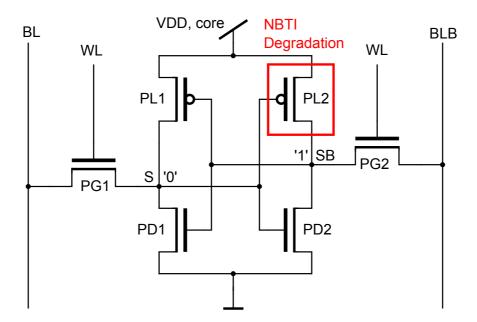

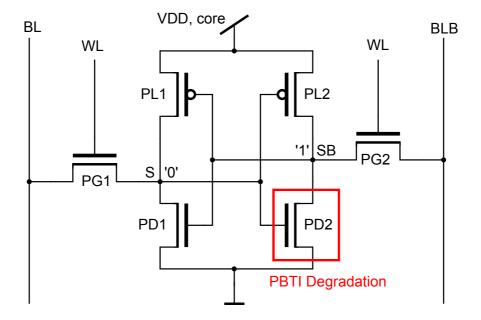

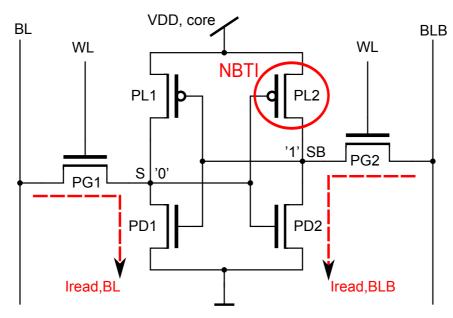

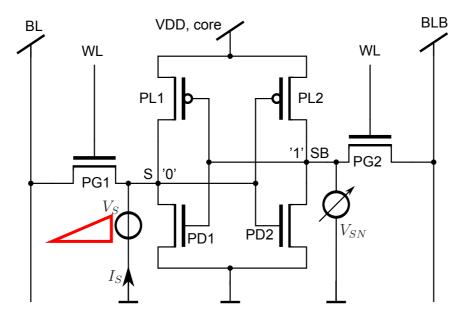

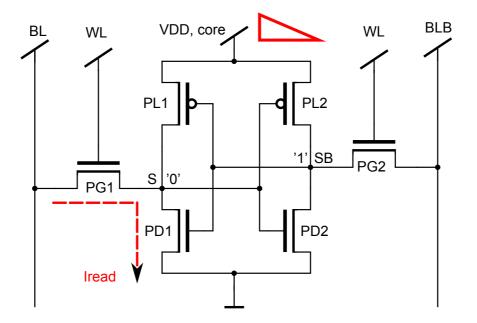

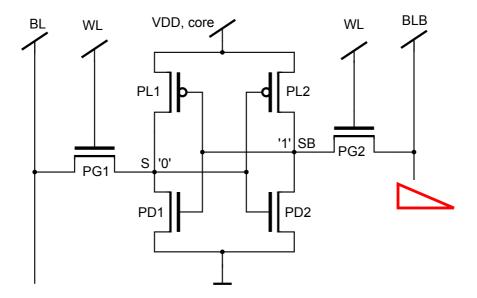

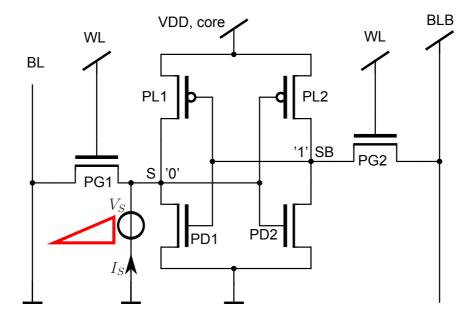

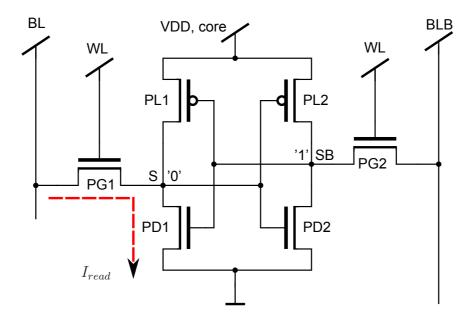

Although many SRAM core cell designs exist with various number of transistors [8], the standard choice is the cell with 6 transistors, called the 6T cell. It is often used because at least until 65 nm technology, this type of cell provides the optimum trade-off between stability and area consumption [9]. The core cell consists of 2 cross-coupled inverters implementing the positive feedback and therefore the two memory nodes which keep the information (original S and inverted  $\overline{S}$ ). 2 additional access- (or pass gate-) transistors are required to read and write the cell in a differential way, resulting in a more robust circuit. Fig. 2.4 shows the schematics of the 6T-SRAM core cell. The transistors in this work are named pullup (PL1, PL2), pulldown (PD1, PD2) and pass-gate or access (PG1, PG2). The pullups are p-type, while the pulldowns and pass-gates are n-type. The 3 standard procedures hold, read and write work as follows [10].

- 'Hold': the access transistors are disabled (WL=0), the information is stored on the feedback-coupled inverter-pair.

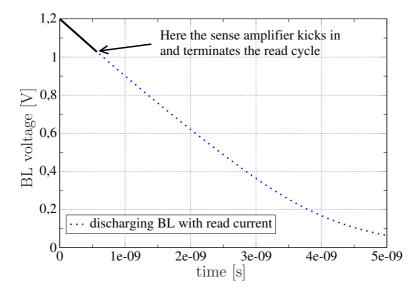

- 'Read': both bitlines BL and  $\overline{BL}$  (or BLB) are precharged to  $V_{DD}$ , then the access transistors are enabled (WL=1). The '0' memory node provides a conducting pull-down to ground and discharges the bitline via the opened access transistor on this side. A sense amplifier detects the sloping voltage on one of both bitlines and concludes this side to be the '0' memory node. The sense-amplifier serves to speed-up

Fig. 2.4: The 6T-SRAM cell consists of 2 feedback-coupled inverters that only allow the 2 stable states '1' and '0' on the memory nodes S and  $\overline{S}$  plus 2 access transistors. This SRAM circuit is in memory state S='0'. The inverted information is kept on memory node  $\overline{S}$ .

the read process, because the bitline then does not need to be discharged completely down to 0 V.

• 'Write': starting from 'Read' case (BL=BLB=1, WL=1), the bitline on the desired '0' memory node side is tied to ground, while the other bitline is kept at V<sub>DD</sub>. If the cell is not in this state already, the voltage on the desired '0' node will drop below the switching level of the opposite inverter and flip the cell.

# 2.2 SRAM Performances and Figures of Merit

SRAM is a volatile memory and its task from the user's point of view is simple: as long as the cell is connected to supply voltage, it must keep data (hold) and enable to read and write data. Ideally, this must be done very fast, on minimum die area, with almost no leakage and great yield.

Each core cell has different qualities and strengths, depending on its design. All these different qualities must be measurable to be able to compare various core cells. While some qualities are unambiguos (e.g. area in  $\mu$ m<sup>2</sup>), some others need Figures of Merits (FoMs) when they are not directly measurable (e.g. cell stability). Table 2.1 provides the list of all core cell performances and Figures of Merit if necessary.

It is important to note that, as in probably every technical system, not all performances can be improved together; some of them are oppositional requests. The most important fact for SRAM is that reading and writing are conflicting challenges. Generally, SRAM stability is limited by the switching levels of the 2 inverters. When the '0' memory node voltage surmounts the switching level of the '1' side-inverter, the cell flips. This must be avoided in read case, but must be achieved in write case. This means that a cell is either

| Section | Performance    | Meaning                                       | Figures of Merit  |

|---------|----------------|-----------------------------------------------|-------------------|

| 2.2.1   | Read stability | How easy cell flips during read access        | SNM(read) [V]     |

|         |                |                                               | NCurve [V,A]      |

|         |                |                                               | RM[V]             |

| 2.2.2   | Hold stability | How easy cell flips during hold               | SNM(hold) [V]     |

|         |                |                                               | NCurve [V,A]      |

|         |                |                                               | $V_{min,ret}$ [V] |

| 2.2.3   | Write-ability  | How easy cell flips during write access       | Write Level [V]   |

|         |                |                                               | NCurve [V,A]      |

| 2.2.4   | Speed          | How fast the cell can be read                 | I(read) [A]       |

| 2.2.5   | $V_{min}$      | Lowest $V_{DD}$ to provide full functionality | n/a [V]           |

| 2.2.6   | Area           | Size of one cell on the die                   | $n/a \ [\mu m^2]$ |

| 2.2.7   | Leakage        | Static current during hold state              | n/a [A]           |

| 2.2.8   | Yield          | Fraction of functional cells                  | n/a [1]           |

Table 2.1: 8 performance parameters of an SRAM cell including 4 Figures of Merit

very stable and has good reading quality, but then does not flip easily during write access and therefore has poor writing quality. A cell must always be a trade-off between these 2 qualities. If this trade-off is met best, the cell is called 'centered'.

The next sections are about the 8 performance metrics of an SRAM cell.

#### 2.2.1 Read Stability

These metrics express how easily a cell flips under read conditions, which is sometimes also called 'Access Disturb Margin' (ADM).

#### Static Noise Margin for read case: SNM(read)

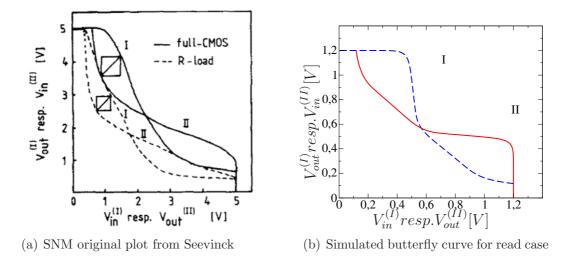

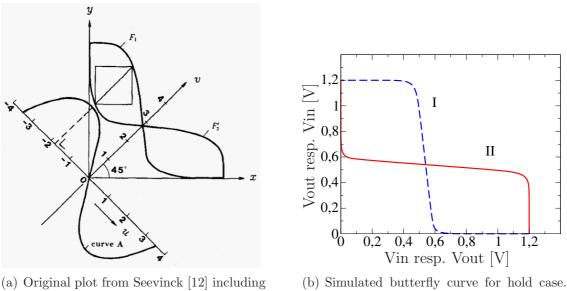

Static Noise Margin (SNM) is the most prominent stability metrics and was introduced more than 40 years ago [11]. Seevinck et al. then wrote the maybe most cited paper in SRAM design, some analytical work and a simulation method about the stability of SRAM cells [12]. Nowadays, this FoM to measure read stability is universally accepted and automated using DC circuit simulators. With this metric, the cell is actually not being flipped, but it is estimated how much voltage room for static noise, i.e. DC voltage, is left until the cell will flip. Therefore, both inverters are first scanned independently to get the transfer curves, also known as voltage transfer characteristics VTC (compare Appendix A). Then, curves are plotted into one diagram, while one transfer curve is mirrored. This results in 2 overlaying curves, better known as 'butterfly curve', compare Fig. 2.5(a) from the original publication and Fig. 2.5(b) from simulation. The eye opening of the biggest inbuilt square is a measure for how much static noise is needed to reach the trigger level of the opposite inverter under read conditions. For this DC value, the curve still represents a 'butterfly', i.e. 2 stable regions and 1 metastable point in the middle. The higher the SNM value, the more stable the cell.

Fig. 2.5: Butterfly curves for read case: original plot from [12] and simulated in 65 nm technology

SNM is perfectly suited for simulation. This is done with a trick: a 45 degrees rotated coordinate system is introduced to optimize calculating the inbuilt square [12]. Simulations in a 65 nm technology showed the results in the middle column of Table 2.2. It can be seen that elevated temperature decreases cell stability. This is due to the decrease in threshold voltages.

| Temperature                | SNM(read)         | SNM(hold)         |

|----------------------------|-------------------|-------------------|

| -40 °C                     | $254 \mathrm{mV}$ | 487  mV           |

| $25 \ ^{\circ}\mathrm{C}$  | $243 \mathrm{mV}$ | $468 \mathrm{mV}$ |

| $125 \ ^{\circ}\mathrm{C}$ | 220  mV           | $436 \mathrm{mV}$ |

| Table 2.2: Simulated SNM values for read and hold case in a 65 nm technology.                         |

|-------------------------------------------------------------------------------------------------------|

| Stability is reduced by $10\%$ in read case and by $7\%$ in hold case when the temper-                |

| ature is increased from 25 $^{\circ}$ C to 125 $^{\circ}$ C. Furthermore, read case is generally much |

| more critical than hold case at nominal supply voltage.                                               |

Unfortunately, SNM is not very well suited for measurement, as access to the memory nodes is needed, which is not provided by conventional SRAM products. Dedicated test structures ('fly cells') are needed. Furthermore, calculating the eye opening is much too complex for extremely fast inline-testing.

#### Read N-Curve

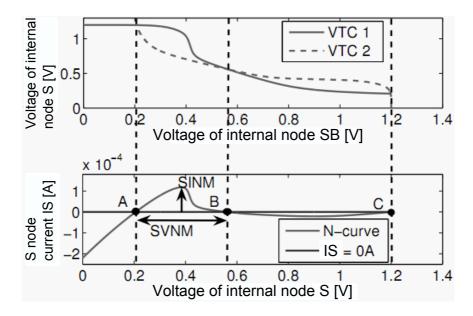

This FoM came up recently [13]; its general idea is to flip the cell with an external force, which can be measured. This external force is a voltage source which is connected to the '0' memory node and then ramped up to  $V_{DD}$ , compare Appendix A. Not only the voltage (and therefore the voltage transfer characteristic) of this setup is monitored, but also the current that the sweeping source provides. This results in the so-called N-curve shown in the lower plot of Fig. 2.6, since it has the shape of an 'N'. Both SNM(read)

Fig. 2.6: Comparison of N-Curve (lower plot) with SNM (upper plot), taken and adapted from [3]. The voltage information in both stability analysis methods is almost the same. N-Curve provides some additional information with the measured current.

and Read N-Curve show correlated results, at least for small currents [14], depicted in Fig. 2.6: the 3 voltages where the current equals 0 are the 3 crossing points in SNM analysis: two stable and one meta-stable point. N-Curve provides additional information with the measured current [3] [15].

In contrast to SNM, the big advantage of Read N-Curve [13] is the ability to measure this metric very fast with automatic inline testers. But unfortunately, this method again requires access to the memory nodes and is therefore not capable for product measurement, compare Static Noise Margin.

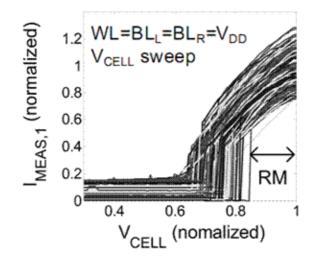

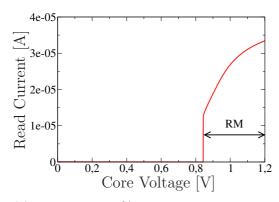

#### Read Margin RM

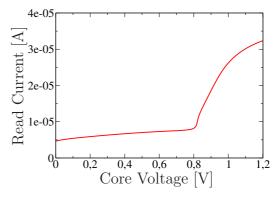

For Read Margin, only the core voltage is reduced to zero, while the periphery is left on nominal  $V_{DD}$ , compare Appendix B. Lowering the core voltage decreases cell stability, and at some voltage, the bitline current drops, compare Fig. 2.7. The difference between the nominal core voltage and the reduced voltage where the bitline current drops is the Read Margin. Static Noise Margin and Read Margin are well correlated [17].

It is important to note that the bitline current only drops if the cell is not kept on its preferred side. Fig. 2.8 provides the two cases of a cell on its non-preferred side (Fig. 2.8(a): bitline current drops) and on its preferred side (Fig. 2.8(b): bitline current does not drop). An ideal SRAM cell (like in simulation) does not have a preferred side, but the unavoidable manufacturing variations in real life always result in a preferred side. Therefore, while SNM can be simply calculated with a DC simulation, RM is only accessible via Monte Carlo simulations. Only when the variability is known for the simulated technology, then the RM stability can be MC simulated.

Fig. 2.7: Read Margin: the difference between nominal supply voltage and the reduced supply voltage where the bitline current drops. Original plot taken from [16]

(a) For about 50% of the cells, at some  $V_{DD,core}$  the read current on the '0' memory side drops to zero. The difference between  $V_{DD}$  and  $V_{DD,core}$  is the Read Margin.

(b) For the other 50% of the cells, the current drop does not happen. The cell is alrady in its preferred state and therefore the current never reaches zero.

Fig. 2.8: Read Margin criterion only works for about 50% of all cases. Two Monte Carlo simulation plots with completely different result.

In contrast to SNM and N-Curve, RM is the only stability-FoM that can be measured with product-like core cells, as no access to the memory nodes is required. Unfortunately, V-I measurements are relatively slow and therefore, this technique is not well suitable for array characterization so far. This is the reason why RM is the better measurement metric.

#### 2.2.2 Hold Stability = Data Retention Stability

These metrics express how easily a cell flips under hold conditions. In principle, the read stability FoMs could be used as well for hold stability characterization, with the difference of a disabled WL. But in practice, this is only valid for SNM and N-Curve: disabling the WL creates SNM(hold) and Hold N-Curve. Read Margin current measurement does not work for hold case, since the measured read current, which is analyzed for the current drop, does not exist in hold case.

#### Static Noise Margin for hold case: SNM(hold)

This is measured like SNM(read) (compare Appendix A), but the access transistor is disabled while the inverter characteristics are scanned. Since the access transistor is not conducting, the transfer characteristic has the typical inverter-shape, compare Figs. 2.9. Some simulated values for 65 nm technology are listed in the right column of Table 2.2

(a) Original plot from Seevinck [12] including the 45 degrees rotated coordinate system

(b) Simulated butterfly curve for hold case. The inbuilt square is much bigger than for read case, because the stability-decreasing access transistor is switched off.

Fig. 2.9: Butterfly curves for hold case: original plot from [12] including the rotated coordinate system for DC circuit simulation and simulated in 65 nm technology

on page 12. The eye opening is much bigger than in read case, which means that in

comparison to SNM (read), for nominal  $V_{DD}$  read case is much more critical than hold case.

To save leakage power, SRAM arrays are often operated with reduced supply voltage, compare sections 2.2.5 and 2.2.7. This is why hold stability must be considered as well. In systems with permanent nominal supply voltage, hold case is no problem.

#### Hold N-Curve

The same setup like for Read N-Curve can be used for Hold N-Curve (compare Appendix A), but with disabled wordline [17]. Again, the 3 voltages where the current equals 0 are the 3 crossing points in SNM analysis: two stable and one meta-stable point, compare section 2.2.1.

#### Minimum Retention Voltage $V_{min,ret}$

Another FoM to characterize hold stability is to lower  $V_{DD}$  when WL=0, i.e. during hold condition. The minimum voltage at which the cell still does not lose its memory state is the minimum retention voltage  $V_{min,ret}$ . Reading is not allowed with this drastically reduced voltage. Since the hold case is very stable compared to read case, the retention voltage can be reduced drastically until the cell loses its state.

#### 2.2.3 Write-ability

Write-ability describes how easily the cell can be flipped under write conditions and is therefore the opposite to stability. This is the reason why it is not possible to optimize both qualities together.

#### Write Level or Write-Trip-Point

The commonly used FoM for writeability is the Write Level, also known as Write-Trip-Point. First, read conditions are applied to a cell (WL=BL=BLB=1), then the BL voltage is lowered on the '1' memory side, compare Appendix C. When the BL voltage is low enough so that the cell flips, then this is called the Write Level. The lower this BL voltage must be to flip the cell, the harder the cell is flippable. So the higher the Write Level value, the better the cell is writeable. Table 2.3 shows some simulated Write Level values. Increasing temperature increases writeability, again of course opposite to stability.

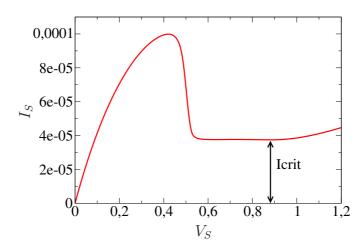

#### Write N-Curve

Similar to Read N-Curve, an external voltage source which is connected to the '0'-memory node is ramped up to  $V_{DD}$ , compare Appendix D. This time the cell is under write conditions, i.e. the '1'-bitline is high, the '0'-bitline is low. The current flowing into the memory node is a measure for the writeability of the cell [13]. The resulting curve is similar to an

| Temperature               | Write Level       |

|---------------------------|-------------------|

| -40 °C                    | $376 \mathrm{mV}$ |

| $25 \ ^{\circ}\mathrm{C}$ | 406  mV           |

| $125~^{\circ}\mathrm{C}$  | 440  mV           |

Table 2.3: Simulated WL values in a 65 nm technology. Write-ability is increased by 8% when the temperature is increased from 25 °C to 125 °C.

'N', compare Fig. 2.10. The so-called critical writeability current  $I_{crit}$  can be read from the graph, it is defined as the current valley in the right half of the plot. If this critical

Fig. 2.10: Write N-Curve: the current valley close to the right end is the writeability current. Bigger values represent better writeable cells.

current is a positive value for all applied voltages (like in Fig. 2.10), then the write process was successful. A more positive current value represents a better writeable cell, a critical current <0 represents a write failure.

It is also possible to use the read stability N-Curve plot to analyze the circuit for writeability [18]. Then, the read N-Curve in Fig. 2.6 on page 13 is read from right to left because this represents lowering of the memory node voltage. The Write Trip Voltage in this approach is the voltage difference between the last 2 zero crossings, namely the points B and C.

#### 2.2.4 Speed / Performance

One of the most important SRAM parameters is the speed of a cell, i.e. how fast the cell can be read. This parameter is sometimes called performance. A Figure of Merit is introduced that does not directly measure speed or a time, but the read current. This read current is discharging the parasitic capacitances of the long bitlines. It is called  $I_{read}$  and determines the time necessary to discharge the bitlines to a value where the sense amplifiers detect the zero node. The bigger this current, the faster the BLs can be

discharged, and the faster the sense amplifier is able to detect the cell state. Since speed is the most important parameter and the reason to use SRAM instead of another volatile memory type, it is the main performance of the cell.

#### 2.2.5 Minimum supply voltage $V_{min}$

In times of high leakage currents, lowering  $V_{DD}$  is the simplest way to save energy in low-power systems, which of course costs performance. But lowering the supply voltage is not only possible during retention mode, but also during normal operation of SRAM, i.e. including read- and write-accesses.

$V_{min}$  is a very prominent parameter for SRAM circuits. It defines the minimum supply voltage that provides full functionality, namely hold, read and write. It is important to note that not only the core voltage is lowered, but also the complete periphery voltage, i.e. BL, BLB and WL voltages. The difference to  $V_{min,ret}$  (which is a parameter of hold stability, compare section 2.2.2) is that also read and write must still work properly.

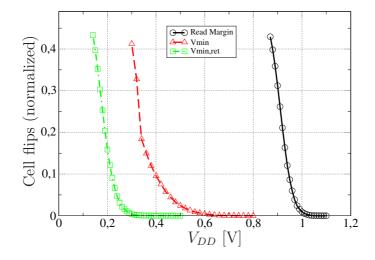

It is remarkable how deep  $V_{DD}$  can be lowered until the first cells start to flip during read condition. Fig. 2.11 shows the measured number of flipped cells for Read Margin condition (right), hold condition (WL=0, left) and  $V_{min}$  (middle). This plot does not include the writing procedure, but it shows that the supply voltage can be lowered from 1.2V to approx. 0.6V before the first cells start to flip. When only the core voltage is lowered (Read Margin case), cells start to flip at much higher voltages, because the access transistors are connected to nominal  $V_{DD}$ .

Fig. 2.11: Measured flips due to lowering core voltage in read state (RM criterium), supply voltage  $(V_{min})$ , and core voltage in hold state  $(V_{min.ret})$

$V_{min}$  cannot be used as a metric for stability, but it is of big importance in mass production. Contrary to many other FoMs, this metric can be determined very easily without special test structures. Hold, read and write procedures are repeated with continuously lowered supply voltage until one procedure fails. This is the  $V_{min}$  value. While SNM and RM represent the stability of the core cell alone,  $V_{min}$  represents the minimum voltage for which the complete system incl. periphery still works. So SNM and RM show Gaussian Distribution, while  $V_{min}$  does not: it includes failure of the periphery.

#### 2.2.6 Area

No FoM is necessary to determine the area of the core cell. For a 65 nm low power CMOS technology, this is a value between 0.6 and 0.7  $\mu$ m<sup>2</sup>. It is very important to keep this area as small as possible, since millions of core cells represent one memory array and a big fraction of area on the die.

#### 2.2.7 Leakage

With shorter channels and thinner gate oxides, channel- and gate-leakage are increasing. Leakage in one transistor is not a big issue, since it normally is in the pA region. But in SRAM arrays with millions of devices, the currents are adding up to a big fraction of complete SoC's power consumption. Measurements have shown that the 1 MBit array in 65 nm low power CMOS technoloy has approx. 25 µA of leakage current at room temperature and nominal  $V_{DD}$ . Of course this is highly temperature-dependent, so operation at 125 °C will multiply this leakage current. Since SRAM is volatile memory, it cannot be switched off, otherwise the data is lost. This is why often the supply voltage is reduced to minimize leakage, compare section 2.2.5. This can be done on two levels. First, only reducing the supply voltage about some 10 mV to ensure full functionality of hold, read and write. This is the  $V_{min}$  value. Second, drastically lower the supply voltage to about half of the nominal supply voltage to ensure only retention of data. This is also called retention mode and can only be done with disabled WL. The corresponding voltage is called minimum retention voltage  $V_{min,ret}$ , compare section 2.2.2.

#### 2.2.8 Yield

Yield is the fraction of working cells of all produced cells. The goal of every production is to reach a yield of close to 1. A cell will fail either due to read or due to write problems. If it is not able to hold data, then it is totally misdesigned. The next chapter 3 will discuss the topic of yield more in detail.

## 2.3 Summary

SRAM cells must be able to hold, read and write data. Ideally very fast, on minimum area, with low leakage and high yield. The goal is to design a cell that provides the best trade-off between all these qualities; it is then called 'centered'. Since it is not possible to optimize all these qualities at the same time and every core cell design has its characteristic strengths and weaknesses, performance parameters are introduced to quantify every single quality of the cell. The main FoMs are for read stability, hold stability, write-ability and speed. FoMs do not provide an absolute value of each quality, but a scalar quantity, so different cells can be compared between each other. This gives the result that read stability is much more critical than hold stability during nominal  $V_{DD}$  usage. Furthermore, stability decreases with increasing temperature.

Comparing the 3 stability metrics SNM, N-Curve and RM, it must be stated that SNM and N-Curve are not very well suited for measurement purpose. They need dedicated test structures with access to the memory nodes ('fly cells') which is not feasible on product chips. Read Margin can be determined with nominal core cell design, but needs slow V-I measurements.

# Chapter 3

# **Degradation and Reliability**

Moore's Law results in an exponentially growing number of devices per chip. This directly leads to much more complex systems, and reliability could be expected to sink drastically. Interestingly, this is not the case: over the last years, reliability was even increasing in spite of growing product complexity and application stresses [19]. This was only possible because of distinct reliability engineering, which is examining the reasons for failure and analyzing the systems with statistical means. The basics to this approach, called the physics-of-failure-concept, as well as the degradation mechanisms will be introduced in this chapter.

# 3.1 Quality, Yield, Variations and Redundancy

'Quality' is the degree to which products or services satisfy or even exceed the requirements and expectations [20]. Simply spoken, this means the product is 'fit for use'. In terms of SRAM, this means that the core cell is able to hold, read and write data.

'Yield' is the fraction of high-quality (i.e. fit-for-use) chips directly after production.

$$Yield = \frac{\text{number of high-quality SRAM cells}}{\text{all SRAM cells}}$$

(3.1.1)

The two main reasons for reduced yield are local defects (randomly distributed in waferand assembly lots) and variations of physical and electrical parameters. The 'random defects' are caused by e.g. irregularities in material structure, effects of introduced particles, damages due to handling of wafers and assembly, etc. Their effect on yield and reliability depends on their size in relation to the dimensions of the affected functional structure. They are addressed by modern automated production techniques in high-class clean rooms. The 'parameter variations', however, are of statistical nature and represent differences between ideally identical physical elements of today's deca-nanometer transistors. The reasons for this are very broad and refer to variations of e.g. doping fluctuations, dimensions due to deposition, lithography and etching processes and related functional electrical parameters (e.g.  $V_{th}$ ,  $g_m$ , ...).

The variations are divided in global and local variations. While global variations, i.e. differences between two dies, can be kept in narrow margins, local variations increase with decreasing feature size. They obey Pelgrom's law [5], which says that the standard deviation of the threshold voltage is increasing with decreasing area of the device.

$$(\sigma = \frac{A}{\sqrt{WL}}). \tag{3.1.2}$$

So if the transistor area is divided by 2 (which is the case from one technology step to the next), the standard deviation will increase by a factor of  $\sqrt{2}$ . This is why variations, together with leakage, are the main challenge in semiconductor manufacturing today.

Generally, microelectronic circuits must be designed in a way that they have high yield after production. This is done by e.g. simulations in all corners (different combinations of PVT: process, voltage, temperature) and design techniques that make the circuit robust against variations.

Although this is also done for memory circuits, it still cannot be guaranteed that all cells in a Mega-Bit array are working correctly after production. This is mainly due to variations on the tiny devices and the huge device count, which results in a non-vanishing probability of single cells with up to  $6\sigma$  variability. If  $1\sigma$  of  $V_{th}$  variation is assumed to be around 40 mV in the 65 nm technology, this means  $V_{th}$  variations of up to 240 mV. This is approx. half of the absolute  $V_{th}$  value!

Consequently, redundancy is commonly used to fight SRAM yield problems. After a burnin step to eliminate the weak cells, a functionality check of every single cell is performed, which can be done in a reasonable time frame. Every cell (or every wordline) that does not work is then re-routed with fuses in the periphery to a spare, additional cell in the array. Then, if not too many cells were failing and enough spare cells were available, the complete memory array is working properly. But this concept only works directly after production, the fusing step cannot be done in-field.

But so far, yield was only considered directly after production. This will now be extended to lifetime and is then called 'reliability'.

## **3.2** Reliability Basics

Reliability = quality during use = stability of its properties and characteristics at time of delivery during subsequent use under the intended conditions during the planned period of use = yield over lifetime [20].

This means that a completely working circuit directly after production must keep its properties over its lifetime so that after a couple of years, this circuit still is of high quality. Unfortunately, there are degrading mechanisms based on the usage (electric fields, temperature, flowing currents, ...). Some of them shift the parameters of the devices over time, these are called parametrical degradation mechanisms and are subject of this work.

#### 3.2. Reliability Basics

Parametrical degradation mechanisms are adding to variations over lifetime [21].

Variations during lifetime = variations after production + degradation during lifetime (3.2.3)

So it makes no sense to consider degradation effects isolated, they always appear together and on top of the unavoidable variations. This approach will be taken into account for SRAM circuits in this work.

The fundamental reliability aspects are now discussed with the help of an example of working semiconductor devices over time, taken from [22]. Table 3.1 shows the number of fails counted after each time segment. The cumulative number of fails is the complete

| Time [years] | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|--------------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Fails count  | 15  | 1   | 0   | 0   | 0   | 1  | 2  | 2  | 2  | 2  | 2  | 2  | 5  | 15 | 25 |

| $\sum$ fails | 15  | 16  | 16  | 16  | 16  | 17 | 19 | 21 | 23 | 25 | 27 | 29 | 34 | 49 | 76 |

Table 3.1: Number of failures of a device over time with a sample size of 5000

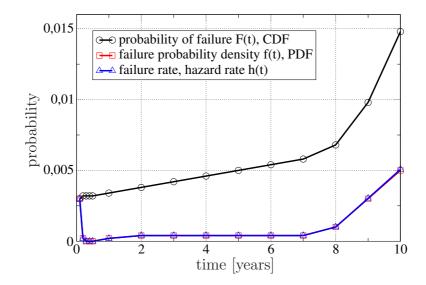

number of non-working chips over time. Normalized to the sample size of 5000, it is called the probability of failure F(t), better known as the cumulative density function (CDF) of failure. The derivative of the CDF is the failure probability density, which is the number of fails per time segment normalized to the complete sample size. It is better known as the probability density function (PDF). The failure rate  $\lambda(t)$  (or hazard rate h(t)) is the number of fails per time segment normalized to the number of working samples. Since the number of fails is low in this example, both characteristics coincide, compare Fig. 3.1. The

Fig. 3.1: Cumulative density function (CDF), Probability density function (PDF) and bathtub-like failure rate h(t). PDF and h(t) coincide in this example.

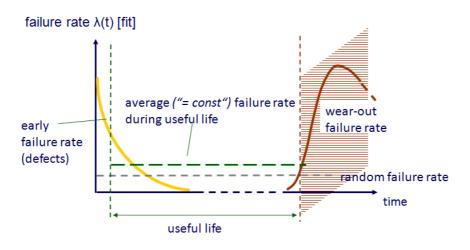

shape of the failure rate curve  $\lambda(t)$  is like the cross-section of a bathtub, it is therefore called the bathtub curve [23]. The characteristic shape of this most famous reliability

curve can be divided in 3 parts and results from the superposition of 3 fundamental failure rate curves, compare Fig. 3.2.

- 1. Infant mortality region with early failure rate

- 2. Useful operating life region with randomly distributed failure events vs. time, therefore almost constant failure rate

- 3. System wear-out region with wear-out failure rate (due to failure modes covered in this work)

Fig. 3.2: The characteristic shape of the bathtub curve results from the superposition of 3 failure rates: early-, constant- and wear-out-failure rate. This work is about the wear-out failure rate. [20]

The early failures are because of products with production weaknesses, which still pass the functionality check but have some built-in defects. These normally do not live long, they fail during the first usage. In semiconductor industry, this is fighted by special screening or 'burn-in': usage with raised temperature and voltage stresses the device so much that most of the infant mortality candidates fail during production test in the company and not at the customer.

The random failure rate phase is the phase of useful life. Failures in this period are not built in the product, but caused externally by the conditions of use, like overvoltage, radiation etc. The dominant value in this region is the mean time between failure MTBF. It is not predictable for a single device, it can only be determined for a big amount of devices via statistics. But with a huge number of devices, these statistics work very precisely.

The random failure rate phase can be compared with radioactive decay: nobody knows about one specific atom when it will decay, but with the huge number of atoms in materials, the radioactive half-life can be determined very precisely. This half-life is an equivalent information to MTBF, but half-life is not a used term in semiconductor industry.

The wear-out region is the end-of-life region. Wear-out happens because of degrading mechanisms. These mechanisms do not start after some years, they start directly after production when the device is used. But after useful life, the degradation becomes so bad

#### 3.3. Physics-of-Failure Concept

that the quality of the device is no longer given, it is not fit-for-use anymore. The question that is most important: when does the wear-out failure rate reach a certain limit, which determines end of useful life?

This thesis is about the parametrical wear-out mechanisms of 6T SRAM cells. What different mechanisms exist, which of them have bad impact on the performance or quality and can it be quantified? And, in the end, are there any means against that?

## **3.3** Physics-of-Failure Concept

The physics-of-failure concept is an approach to design and development of reliable products to prevent failure based on the knowledge of root cause failure processes. It is based on understanding the effects of loads (stressors) on product materials and their influence on the life time with respect to the use conditions and time [20].

This concept dominantly works for the wear-out zone of the bathtub curve. The root cause failure processes in this work are parametrical degradation mechanisms that are discussed in the following section 3.4.

These parametrical degradation mechanisms did not occur so drastically in the last decade, they are the result of continuous scaling. While scaling down the geometry of a microelectronic circuit with the factor 1/k, the supply voltage must be scaled with the same factor, otherwise the stressors are increasing. Table 3.2 shows the scaling principles of microelectronic components. The right column repesents constant field scaling, the middle column non-constant field scaling at constant  $V_{DD}$ . In practice, a value between those two extremes is given. The factor k typically is approx.  $\sqrt{2}$ , e.g. between 90 nm and 65 nm technology.

| supply voltage scaling          | 1         | 1/k   |

|---------------------------------|-----------|-------|

| packing density                 | $k^2$     | $k^2$ |

| drain current per channel width | $k^2$     | 1     |

| current density                 | $k^3$     | k     |

| oxide field strength            | k         | 1     |

| power dissipation density       | $k^3$     | 1     |

| power dissipation per gate      | k         | 1/k   |

| gate delay                      | $1/k^{2}$ | 1/k   |

Table 3.2: Principle of scaling: if the supply voltage was scaled with the same factor 1/k like the geometry (typically  $1/\sqrt{2}$  from one technology node to the next), all values except current density would either improve or stay the same. Unfortunately, supply voltage scaling is limited by noise and threshold voltage; therefore the voltage scaling is somewhere between both columns. This means increasing stressors. [24]

The clear trend is, that operational stresses increase dependent on voltage scaling, but voltage scaling is limited by noise and threshold voltage. This is why the voltage cannot be scaled according to the geometry scaling factor ('non-constant field scaling'), and the result is stronger electrical fields and therefore stronger degradation mechanisms in every technology node. They are the reason why this work is now done for 65 nm technology node, when the influence is starting to have heavy impact on the circuit behavior and its reliability.

When the stresses become so huge that the next scaling step is not possible anymore, materials research has to supply a new material with different properties. This is the case for high- $\kappa$  materials. With conventional  $SiO_2$  gate dielectrics, the 65 nm technology node was one of the last to have reasonable performance in terms of leakage. The next miniaturisation step would have increased leakage so much that a new material with higher dielectric constant had to be found. It enables to increase the gate insulator thickness but keep or even improve the gate capacity, which is necessary for good transistor behavior. On the other hand, however, it is the source for a new parametrical degradation mechanism.

# **3.4** Parametrical Degradation Mechanisms

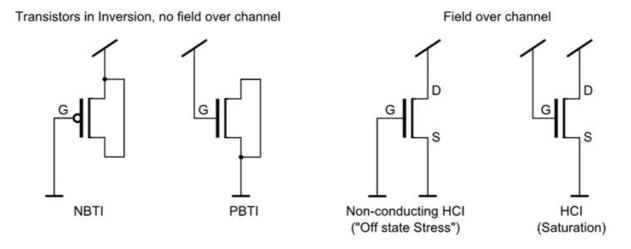

There are 4 different voltage and current scenarios for a metal oxide semiconductor field effect transistor (MOSFET) causing 3 types of parametrical degradation mechanisms:

- 1. Conducting transistor, but no electrical field over the channel and therefore no current  $\rightarrow$  BTI (Bias Temperature Instability), left half of Fig. 3.3

- 2. Conducting transistor and electrical field over the channel, therefore current flowing  $\rightarrow$  HCI (Hot Carrier Injection), right scenario in Fig. 3.3

- 3. Non-conducting transistor, but electrical field over the channel  $\rightarrow$  off-state Stress or NCHCI (Non-conducting Hot Carrier Injection), 2nd from right in Fig. 3.3

- 4. Non-conducting transistor, no electrical field over the channel  $\rightarrow$  no degradation mechanism (not considered further)

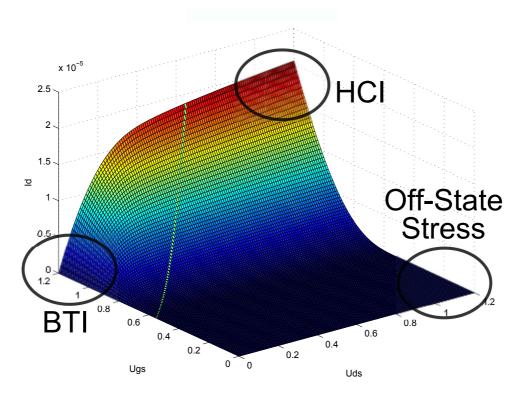

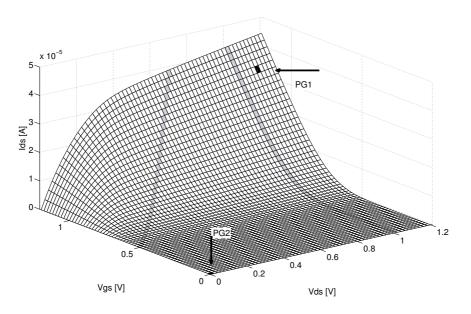

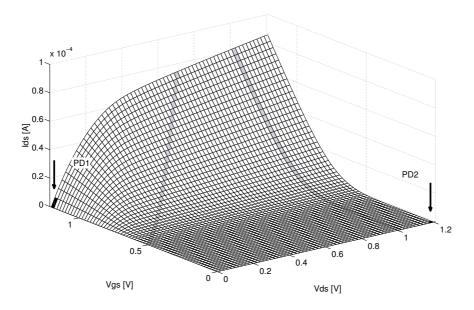

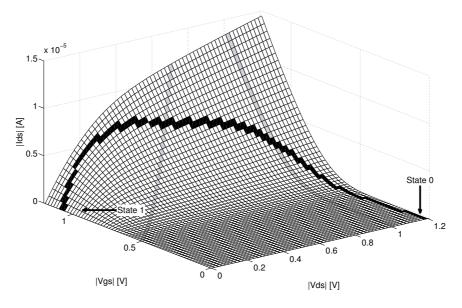

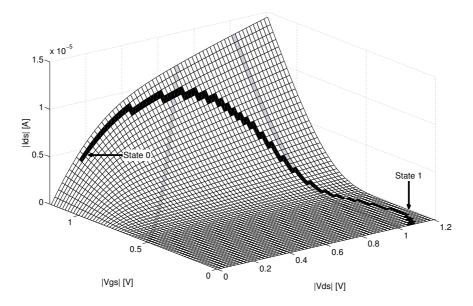

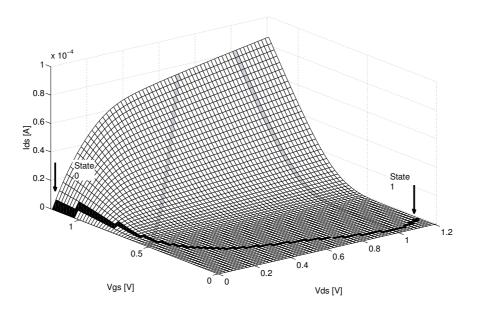

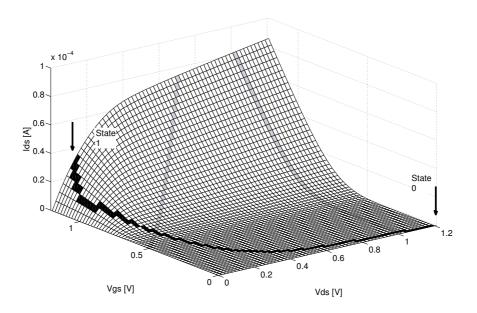

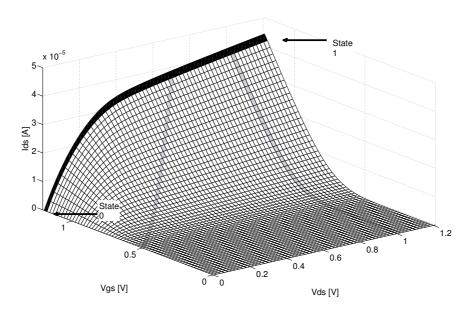

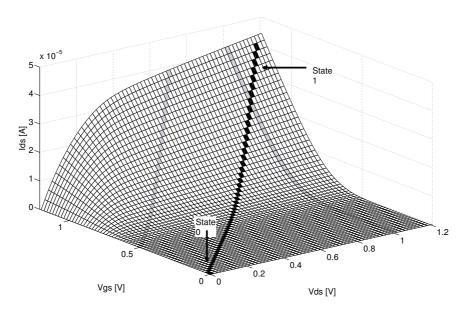

In Fig. 3.4 the corresponding regions in the output characteristic of a MOSFET are shown. In the following sections, these 4 parametric degradation effects will be discussed in detail.

BTI also occurs when the transistor is conducting, but the effect is reduced due to the lowering electric field along the channel from source to drain. As this mode is not of importance for SRAM cells, it will not be regarded here.

Fig. 3.3: The 4 parametrical degradation effects caused by the 3 different connection scenarios. NBTI is only active for pMOS and PBTI is only active for nMOS, while HCI and NCHCI are active for both polarities.

Fig. 3.4: 3D plot of the output characteristic of a MOSFET. The fine line is separating the triode region from the saturation region. In every section of the plot, there is one active degradation mechanism.

## 3.5 Negative Bias Temperature Instability (NBTI)

#### 3.5.1 NBTI threshold voltage drift $\Delta V_{th}$

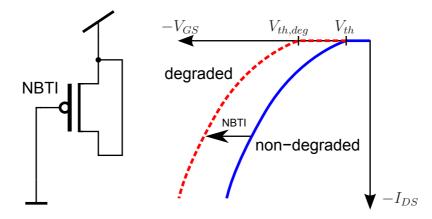

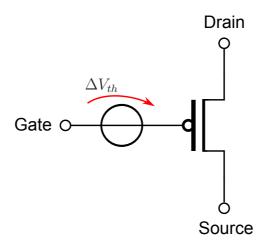

Negative Bias Temperature Instability (NBTI) is a degradation effect that occurs on pMOS transistors in inversion without electric field over the channel [25] [26]. Fig. 3.5 on the left shows the stress conditions: gate is pulled to ground, while source and drain are both connected to  $V_{DD}$ . Many parameters will be shifted by NBTI, e.g. the transconductance  $g_m$ , the channel mobility  $\mu_0$  or the on and off current. But all these shifted parameters can be modeled with the shift of only one core parameter, the threshold voltage. Fig. 3.5 on the right shows the transfer characteristic of a stressed vs. a non-stressed device. The threshold voltage  $V_{th}$  got shifted to smaller values, i.e. a transistor with e.g.  $V_{th} = -0.5V$  will degrade to e.g.  $V_{th} = -0.55V$ .

Fig. 3.5: Stress conditions (left) for NBTI and the impact of this degradation mechanisms on the output characteristic: shift of  $V_{th}$  (right)

The shift of this threshold voltage due to NBTI was modeled. This is the formula which gives an estimation of the  $V_{th}$  drift [27].

$$\Delta V_{th} = A \cdot \left(\frac{|V_{gs}|}{t_{inv}}\right)^m \cdot exp\left(\frac{\Delta E}{kT}\right) \cdot L^{\alpha} \cdot W^{\beta} \cdot t^n \tag{3.5.4}$$

The formula can be divided in four parts, which represent several factors:

- 1. Electrical field dependency with power law. The exponent m is getting bigger with smaller technology (90 nm:  $\approx 2, 65$  nm:  $\approx 4, 32$  nm:  $\approx 5$ ).  $t_{inv}$  is not the geometrical oxide thickness, but the effective electrical oxide thickness in inversion given by the location of the inversion layer, which is thicker. Here, the geometrical oxide thickness is 1.8 nm, but the  $t_{inv}$  value is 2.85 nm.

- 2. Exponential Arrhenius temperature dependency with Boltzmann constant  $k=8.617\cdot 10^{-5} \text{ eV/K}$  and effective activation energy  $\Delta E$ .

#### 3.5. Negative Bias Temperature Instability (NBTI)

- 3. Geometry dependency over power law (L=length, W=width of the device)

- 4. Time dependency over power law

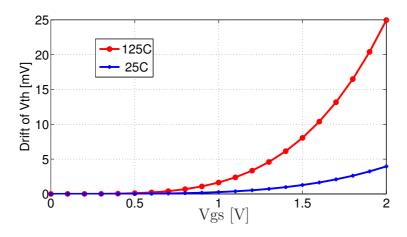

Using this formula for typical scenarios, Fig. 3.6 shows the plot of  $\Delta V_{th}$  over the gate source voltage  $V_{gs}$  for an example of 10<sup>4</sup> s stress time for two different temperatures. It is getting clear that the  $V_{th}$  drift is depending heavily on temperature and gate-source voltage.

Fig. 3.6:  $\Delta V_{th}$  over  $V_{gs}$ . Increasing temperature from room temperature to 125 °C increases the  $V_{th}$  drift by a factor of 6. Doubling  $V_{gs}$  increases the  $V_{th}$  drift by a factor of 15.

The dependency on  $V_{gs}$  is calculated from:

$$\frac{\Delta V_{t1}}{\Delta V_{t2}} = \frac{\left(\frac{V_{g1}}{t_{inv}}\right)^m}{\left(\frac{V_{g2}}{t_{inv}}\right)^m} = \left(\frac{V_{g1}}{V_{g2}}\right)^m \tag{3.5.5}$$

So compared to nominal supply voltage of 1.2 V, for 1.0 V  $V_{gs}$  there is still 48%  $\Delta V_{th}$ , at 0.8 V  $V_{gs}$  there is 20% and at 0.6 V  $V_{gs}$  a rest of 6%. In other words, doubling  $V_{gs}$  increases  $\Delta V_{th}$  by about a factor of 15. But NBTI is also heavily depending on temperature. This shows the comparison of both curves in Fig. 3.6: one is for 25 °C, the other one for 125 °C. Increasing the temperature from room temperature to 125 °C increases the  $\Delta V_{th}$  by about a factor of 6.

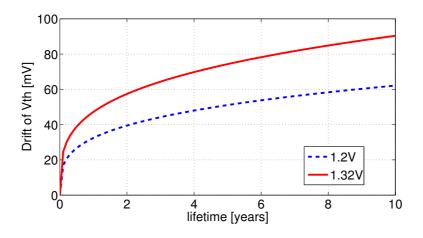

Fig. 3.7 shows  $\Delta V_{th}$  shift over linear lifetime. This shows the typical log-like behaviour so that 50% of the final degradation after 10 years is reached after approx. 1 year.

To add several degradation scenarios resulting from several consecutive stress-steps, the single  $\Delta V_{th}$  cannot simply be added, since they are not adding linearly. Instead, the following equation must be used:

$$\Delta_{tot} = (\Delta_1^{(1/n)} + \Delta_2^{(1/n)} + \Delta_3^{(1/n)} + ...)^n$$

(3.5.6)

The worst case for SRAM products is 10 years @ 125 °C and 1.32 V (110% nominal  $V_{DD}$ ),

Fig. 3.7:  $\Delta V_{th}$  over time. 50% of the degradation after 10 years is already reached after approx. 1 year.

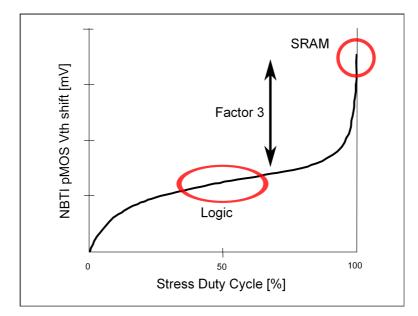

resulting in almost 100 mV  $\Delta V_{th}$ , compare Fig. 3.7. But the biggest problem of NBTI is not only the  $V_{th}$  shift, but two other major issues: variability and recovery [28], which are covered in the next two sections.

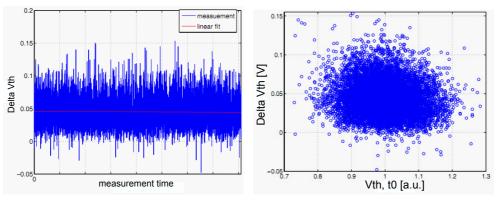

#### 3.5.2**NBTI** variability

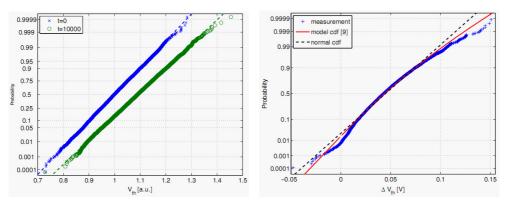

The model provided so far only supports the mean value of threshold voltage drifts of big transistors (area in the  $\mu m^2$  region). SRAM transistors have an area in the 5000 nm<sup>2</sup> region, which is about 2 orders of magnitude smaller. NBTI is a highly statistical process, as measurements on SRAM-sized pMOS transistors (W/L=90/65 nm) show in Fig. 3.8(a) and Table 3.3 [29]. After  $10^4$  s stress with 2.4 V stress voltage at 125 °C, the threshold

(a) pMOS  $V_{th}$  shifts caused by NBTI after (b) High threshold voltage values before  $10^4$  s stress with 2.4 V and 500 s recovery [29]. Shift values between +40 mVand -150 mV show huge variability.

stress and high threshold voltage drift due to NBTI are not correlated

Fig. 3.8: Measurements on SRAM-sized pMOS transistors (W/L=90/65 nm) taken from [29]

voltage drift of each device varies between +40 mV and -150 mV. It is important to note that there are only a few mavericks that show  $V_{th}$  drift to more positive values. The scatter plot in 3.8(b) shows that the transistors with high threshold voltage values are not the devices with high threshold voltage drift. [29]. Both values are uncorrelated, which is good news for circuit design; this avoids single devices with extremely high threshold voltage after stress. While the threshold voltage is normal distributed over SRAM cells,

|                                | $\sigma/\mu$ | $\mu$              | σ                  |

|--------------------------------|--------------|--------------------|--------------------|

| $V_{th} (t=0)$                 | 0.077        | -                  | -                  |

| $V_{th}$ (t=10 <sup>4</sup> s) | 0.078        | -                  | -                  |

| $\Delta V_{th}$                | 0.51         | $44.9 \mathrm{mV}$ | $22.8 \mathrm{mV}$ |

Table 3.3: Ratio of mean value and standard deviation shows a highly statistical process [29]

NBTI creates a shift of the mean value of this distribution. Additionally, the standard deviation seems to increase slightly (Fig. 3.9(a) and Table 3.3). Another hint to a wider  $V_{th}$ distribution after NBTI stress is the  $\Delta V_{th}$  distribution, which does not follow a Normal distribution exactly (Fig. 3.9(b)).

of threshold voltage, while the standard deviation is slightly increased.  $V_{th}$  is normal distributed pre and post NBTI stress.

(a) NBTI causes a mean value right-shift (b) The threshold voltage drift does not show perfect Normal distribution. Too many transistors show a huge  $V_{th}$  shift.

#### Fig. 3.9: Distributions of absolute threshold voltage and threshold voltage drift taken from [29]

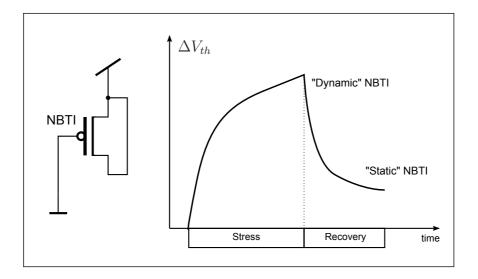

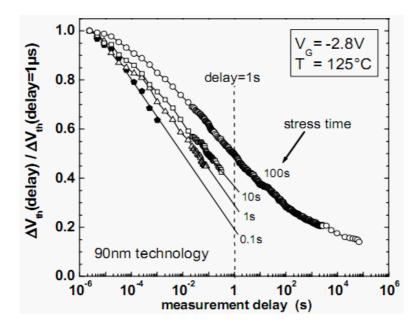

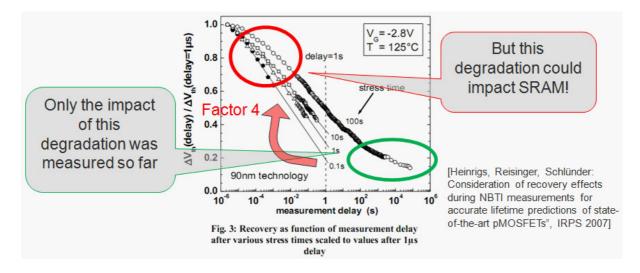

#### 3.5.3NBTI recovery

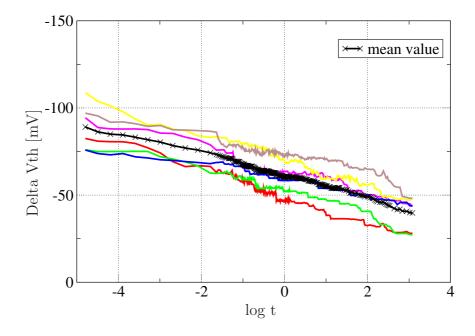

NBTI not only has strong variability, but also shows recovering behavior after end of stress, compare Fig. 3.10. Measurements on huge single transistors in 90 nm technology  $(W=10 \ \mu m, L=0.12 \ \mu m)$  have shown that directly after termination of NBTI stress conditions, the  $V_{th}$  shift starts to drop [30]. In Fig. 3.11 the x axis represents the time after end of stress, while the y axis represents the  $V_{th}$  shift. This happens with extremely short

Fig. 3.10: Stress condition of NBTI and qualitative diagram of static and dynamic NBTI on single pMOS transistor: During stress,  $V_{th}$  shift grows quasilogarithmically. Directly after end of stress,  $V_{th}$  rapidly decreases to a quasi-static value, which then only changes in very long timescales.

Fig. 3.11: Recovering behaviour of NBTI directly after end of stress. At 1 s after end of stress, approx. 50% of the  $\Delta V_{th}$  has disappeared. Original plot taken from [30]

time constants, so that 1 s after end of stress, 50% of the maximum  $\Delta V_{th}$  @ 1 µs after end of stress has disappeared. This behaviour leads to 2 problems.

First, the NBTI  $\Delta V_{th}$  models would have to refer to a specific time after stress, since this value is changing drastically. For the currently used models, this is not the case.

Second, all measurements would have to be done immediately (i.e. some ns after end of stress). This is not possible, and considering this effect in the measurements is a huge challenge.

#### 3.5.4 NBTI physical background and modeling

NBTI appeared in 1967 [25], and in the 1970s, the first model describing this phenomenon was created: the reaction-diffusion model. This is based on the theory that H+ ions are trapped in the oxide by a diffusion process, which also explains the high temperature dependency [26]. Although this model was under discussion and was almost accepted for decades, it could not explain the recovery behavior precisely [31]. The model therefore got changed from 'reaction-diffusion' to 'capture-emission' in the last 2 years [32] [33]. Now it seems that diffusion is not involved in this process [31]. With this theory, degradation means trapping ('Capture') of charges with a broad range of time constants, similar to 1/f noise. Recovery on the other hand means detrapping ('Emission') of charges with comparably, but independent broad range of time constants, again similar to 1/f noise.

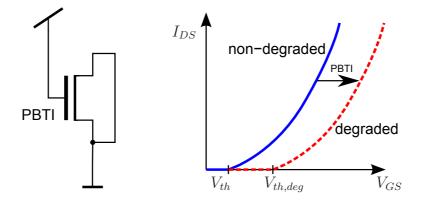

# **3.6** Positive Bias Temperature Instability (PBTI)

With scaling the transistor sizes and widths of dielectrics, leakage is becoming more and more dominant. Until 65 nm technology, leakage was in an acceptable region. But going below 65 nm requires the introduction of new gate dielectrics, which allows to increase gate thickness on one hand to decrease leakage, but at the same time increase or at least keep the dielectric properties. This can be done with new materials with a higher dielectric constant, so-called high- $\kappa$  dielectrics.

Unfortunately, this is the source for another parametric degradation effect: the Positive Bias Temperature Instability (PBTI) for nMOS transistors. The behavior is very similar to NBTI: charges are trapped in the gate oxide [34]. But contrary to NBTI, no positive charges, but electrons are trapped. The result is threshold voltage drift to more positive values, so that the transistor is also getting weaker over time. Fig. 3.12 shows the stress conditions and the impact of this degradation mechanism. PBTI is even less understood than NBTI. Right now, PBTI is discussed not so often in literature, as even the much better known NBTI modeling is still not well understood.

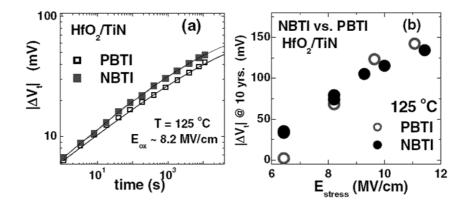

First measurements in Fig. 3.13 have shown that the amount of threshold voltage drift is similar to NBTI. Also, PBTI shows the same variability and recovery like NBTI [36]. So the analytic model describing the mean  $V_{th}$  shift is similar to NBTI, but with a different set of parameters. But since 65 nm technology is a non-high- $\kappa$  technology, no PBTI exists, so this is not discussed further.

Fig. 3.12: Stress conditions (left) for PBTI and the impact of this degradation mechanism on the output characteristic: shift of  $V_{th}$  (right)

Fig. 3.13: Measurements show that the threshold voltage drift of NBTI and PBTI is about the same value under the same stress conditions. High- $\kappa$  material is a stack of  $HfO_2/TiN$ . Original plot taken from [35]

# 3.7 Hot Carrier Injection (HCI) and Nonconducting HCI (NCHCI)

Hot Carrier Injection (HCI) is the best understood parametrical degradation mechanism of all covered in this work. It was very famous in the 1980s, when supply voltages where higher [37]. This effect got reduced in its impact in the last decades by technology development, esp. drain engineering like Lightly Doped Drain (LDD). So in 130 nm technologies and below, the HCI effect almost disappeared. But now, with smaller and smaller channel lengths, the effect might return.

When carriers travel through regions of high electric field, they can gain large kinetic energy. When the mean energy is getting larger than that associated with the lattice in thermal equilibrium, they are called 'Hot' because the carriers were historically assumed to be thermally distributed at an effective temperature higher than that of the lattice [23]. These high-energy carriers can be injected into the gate oxide or cause interfacial damage.

To get enough kinetic energy, high electric fields are needed. Since E=V/d, the voltage  $V_{ds}$  must be high and the distance L (the length of the device) must be small. In 1970, L was big, but so was  $V_{ds}$ . Nowadays,  $V_{ds}$  got reduced to about 1 V, but the length got down to about 65 nm. This is why this effect came back.

Two mechanisms of HCI must be distinguished: conducting and non-conducting Hot Carriers. Non-conducting HCI is also called 'off-state stress'. While in the conducting HCI the source of the channel carriers is the drain current in the pinch-off region (at SRAM size in the 10  $\mu$ A range), in the NCHCI case this is the channel off-current (at SRAM size in the pA range). Since the on-current is a factor of 10<sup>6</sup> higher, it is clear that the effect of NCHCI is small compared to HCI.

The hot carrier damage will modify the electrical characteristics of the MOSFET device  $(V_{th}, I_{on}, \text{etc.})$ . These modifications can impact the functionality of SRAM cells.

## 3.7.1 Hot Carrier Injection (HCI)

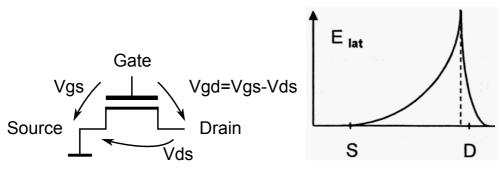

When  $V_{gs}$  is relatively high compared with  $V_{ds}$ , the resistivity along the inverted channel is nearly constant and the potential varies linearly between source and drain (Fig. 3.14(a)). If, however,  $V_{gs}$  is comparable to or lower than  $V_{ds}$ , the inversion layer is much stronger on the source side than on the drain side, and the voltage drop due to the channel current is concentrated on the drain side, compare Fig. 3.14(b). Carriers traveling from the source to the drain can gain a considerable amount of energy in this drain-side high-field region [20]. The field can be so high that carriers gain a significant amount of energy between two scattering events.

So the device must be in saturation mode, which is  $V_{gs} > V_{th}$  and  $V_{ds} > V_{dsat}$ . Only then the electrical field has a strong peak on the drain side of the device, which does not happen in triode region. High  $V_{ds}$  and short L lead to an extremely high lateral electric field on the drain side (compare Fig. 3.14(b)). While in analog circuits, minimum transistor lengths do not occur, it is the case for digitial (and especially SRAM) circuits and therefore HCI is a possible candidate for a degradation mechanism.

Some of the hot carriers gain so much energy that they can surmount the energy barrier at the  $Si/SiO_2$  interface and be injected into the oxide. If the hot-carrier injection is strong enough, the trapped charges or generated defects will permanently modify the electric field and hence the electrical characteristics of the FET. This especially results in a degradation of the on-current. HCI is mostly degrading transistors with full  $V_{ds}$  and

(a) Inversion needs voltages >  $V_{th}$  over the gate. (b) The drain-sided pinch-off For  $V_{gs} < V_{ds} - V_{th}$ , the threshold voltage is not reached anymore on the drain side of the fields. device. This results in pinch-off.

Fig. 3.14: Voltages and high lateral electric field on drain side

$V_{gs}$ . Then the transistor is in saturation with maximum overdrive voltage. In case  $V_{gs}$  and/or  $V_{ds}$  are reduced, the HCI degradation is lowered.

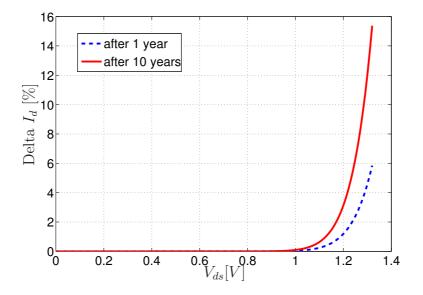

Models have been developed to calculate the lowered current in the channel. This formula calculates the on-current degradation in percent [38]. Each device needs a distinct set of parameters A, m,  $V_0$  and n.

$$\Delta I_D(\%) = A \cdot L^m \cdot exp(\frac{V_{ds}}{V_0}) \cdot t^n \tag{3.7.7}$$

Especially for nFETs, HCI is depending strongly on the applied drain-source voltage  $V_{ds}$ . This can be calculated from 3.7.7

$$\frac{\Delta I_{D1}}{\Delta I_{D2}} = \frac{exp(-\frac{V_0}{V_{DS1}})}{exp(-\frac{V_0}{V_{DS2}})} = exp(-V_0(\frac{1}{V_{DS1}} - \frac{1}{V_{DS2}}))$$

(3.7.8)

So for nFETs, below a drain-source voltage of 1.0 V, this effect can be neglected, compare Fig. 3.15.

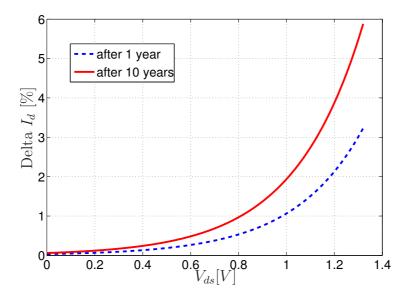

For pFETs, the dependency on the drain-source voltage is smaller, comparable to NBTI voltage dependency, compare Fig. 3.16.

## 3.7.2 Non-conducting HCI

For the non-conducting case,  $V_{gs}=0$  (or at least below  $V_{th}$ ) and  $V_{ds}$  is high. This means that the device is switched off, but an electric field over the channel exists. This is the reason

Fig. 3.15: HCI sensitivity of nFET on  $V_{ds}$ : strong degradation after 10 years with nominal or increased supply voltage. When  $V_{ds}$  is lowered to 1 V, HCI damage has disappeared.

Fig. 3.16: HCI sensitivity of pFET on  $V_{ds}$ : less strong degradation compared to nFET, but still active with lowered supply voltage.

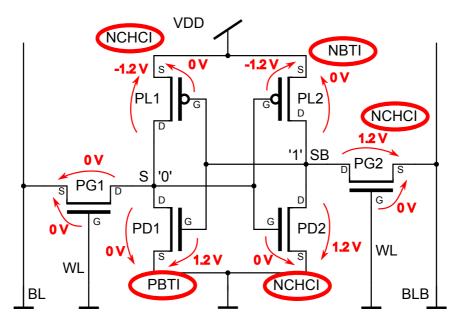

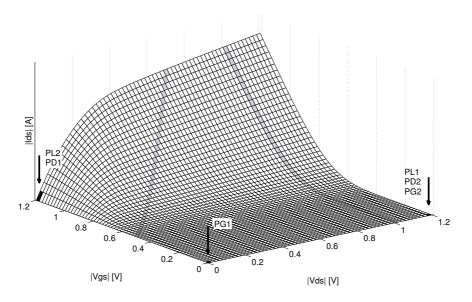

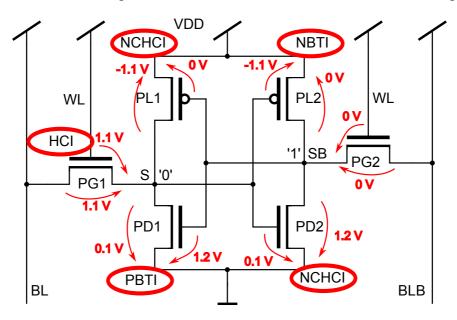

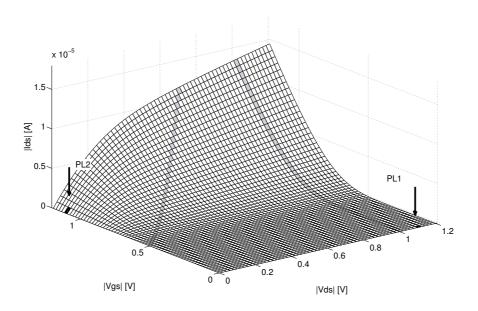

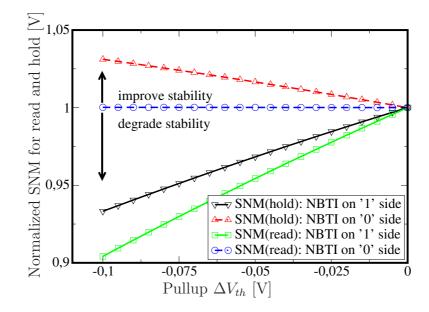

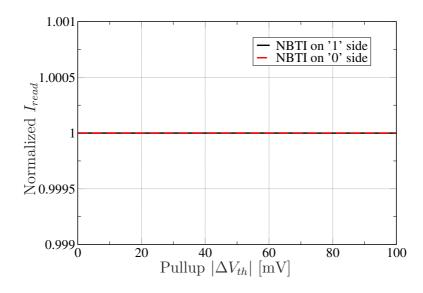

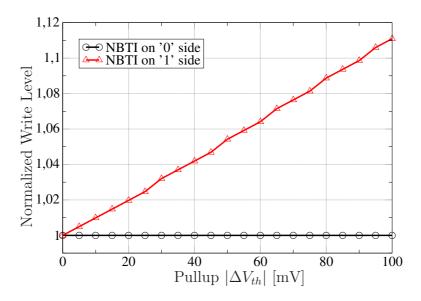

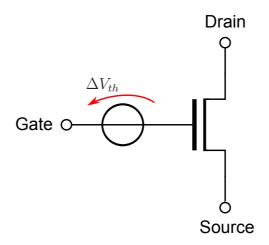

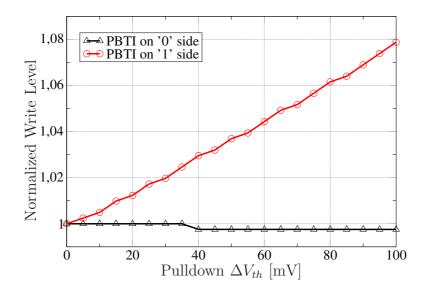

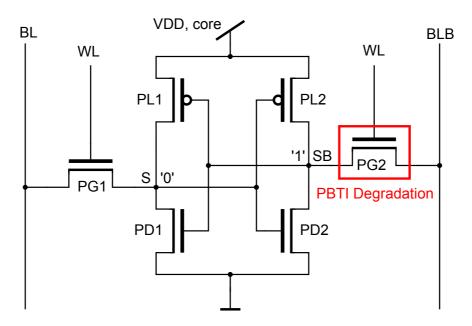

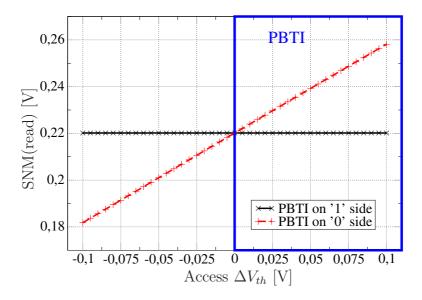

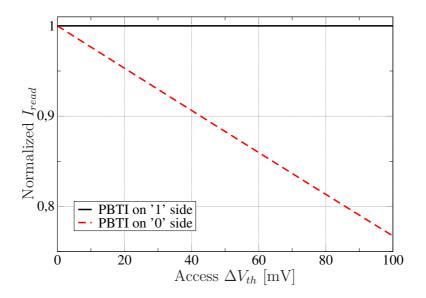

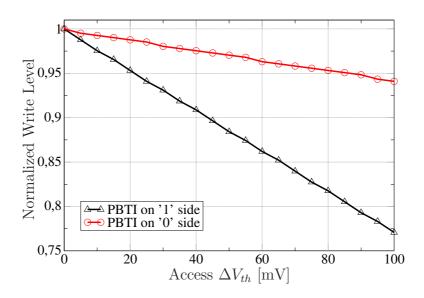

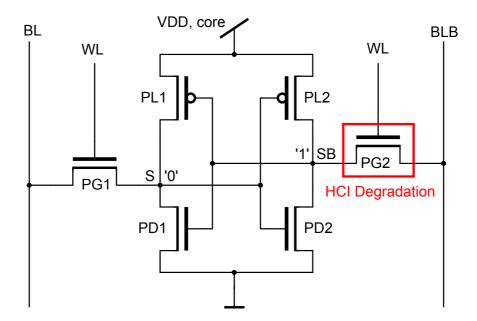

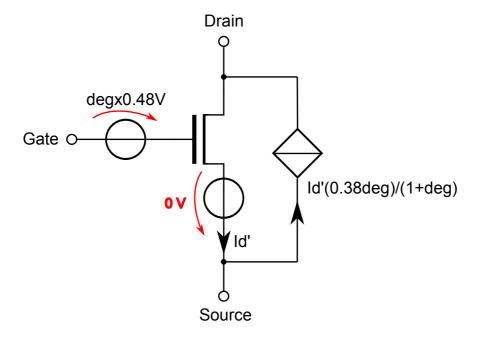

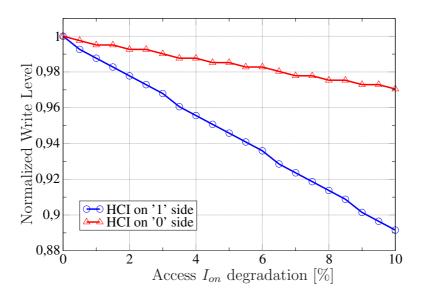

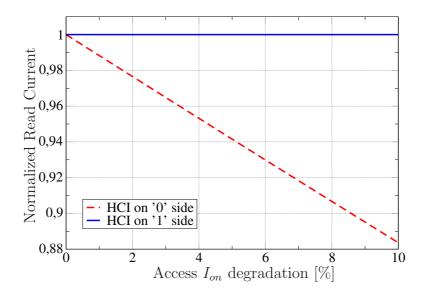

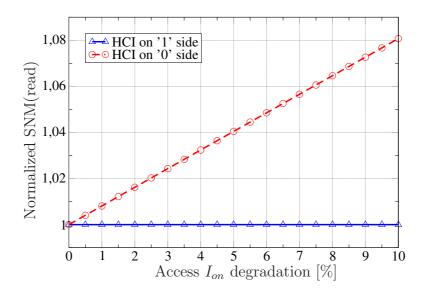

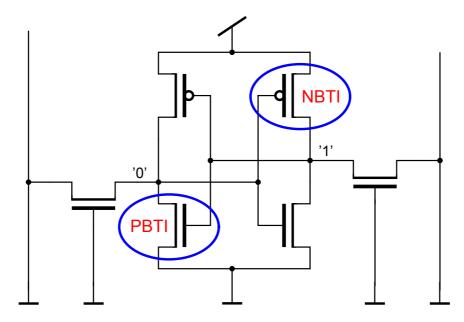

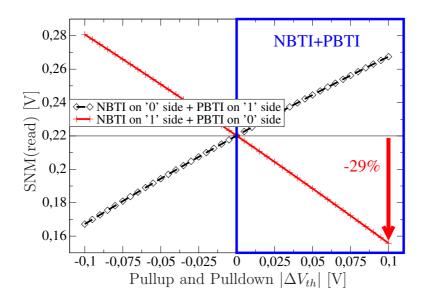

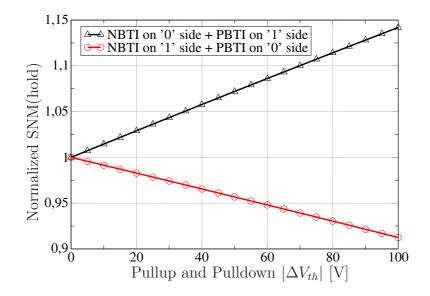

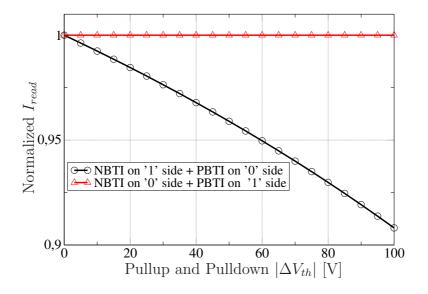

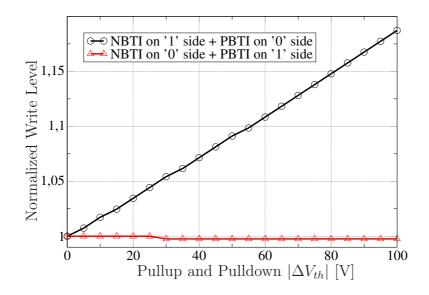

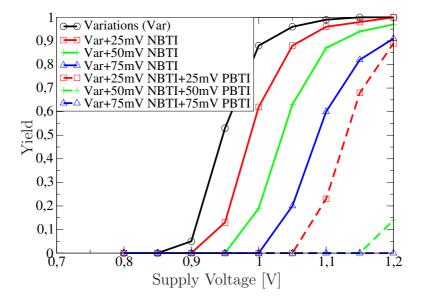

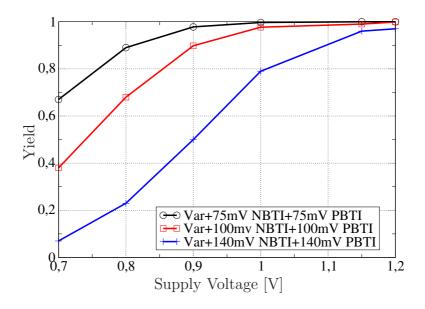

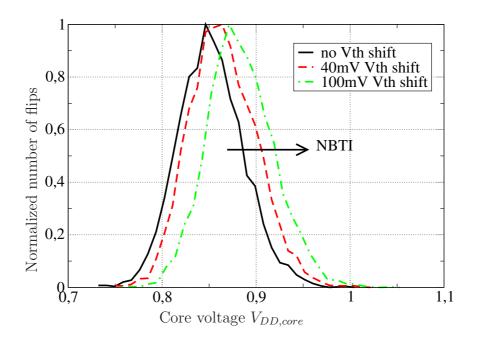

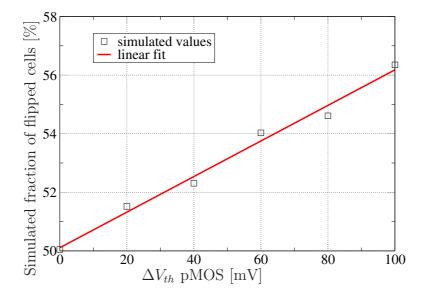

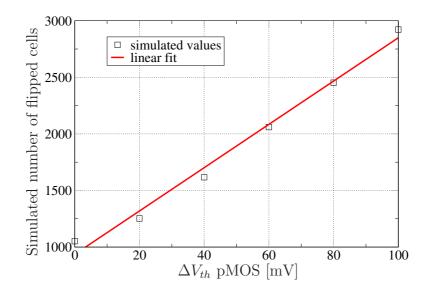

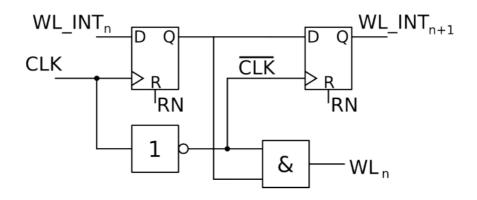

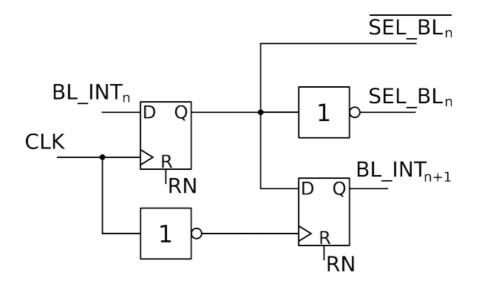

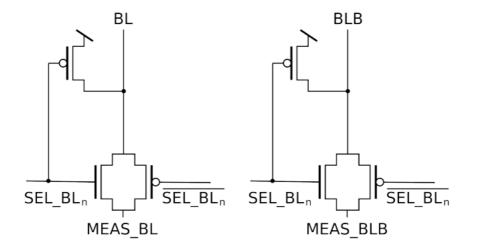

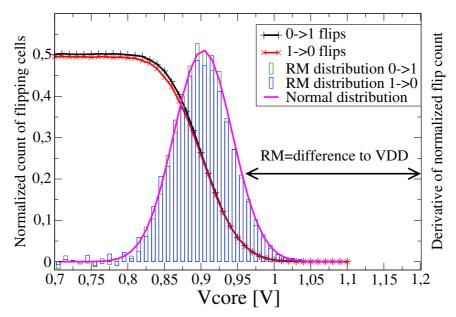

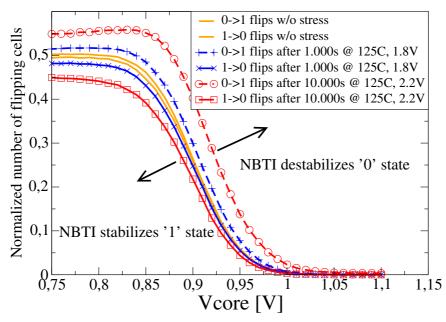

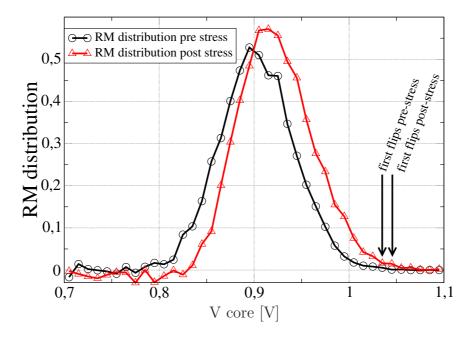

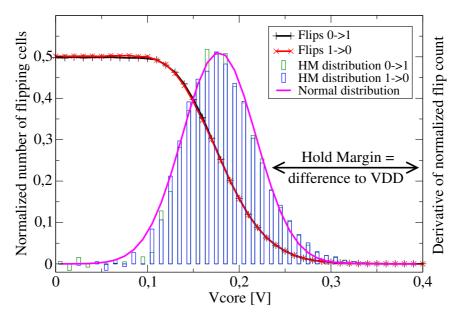

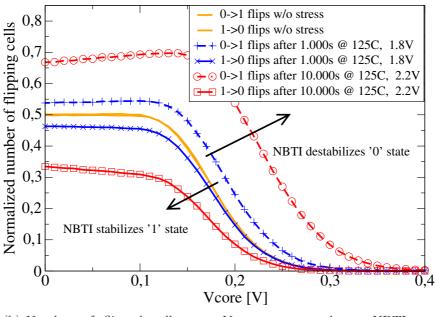

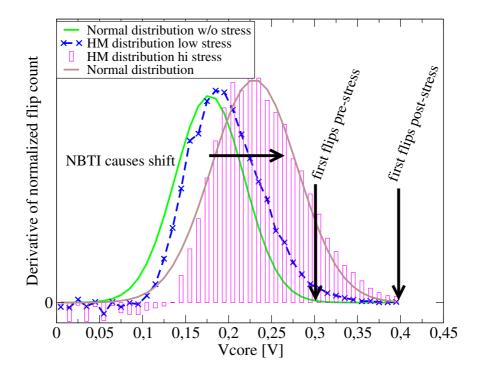

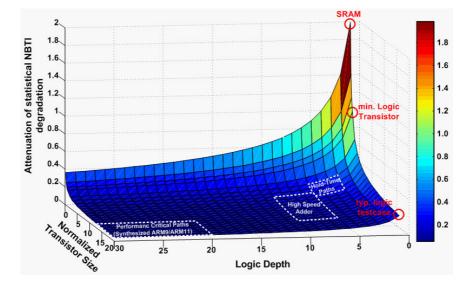

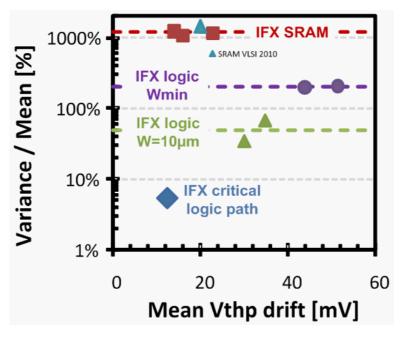

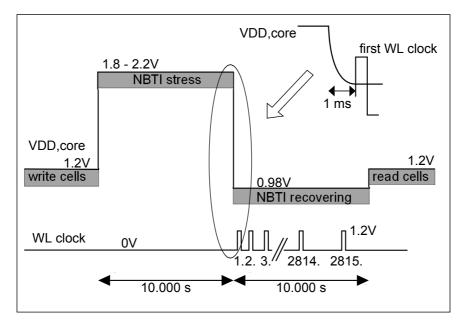

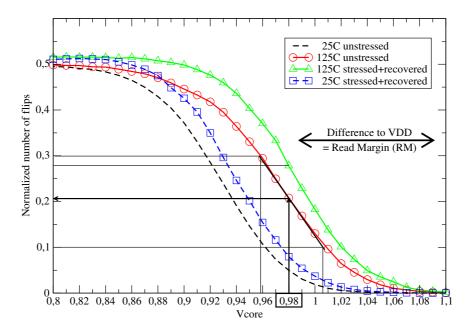

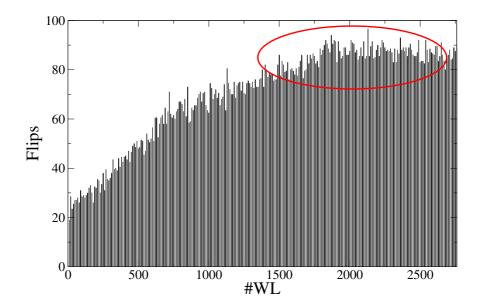

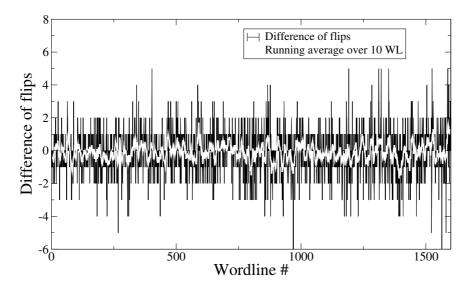

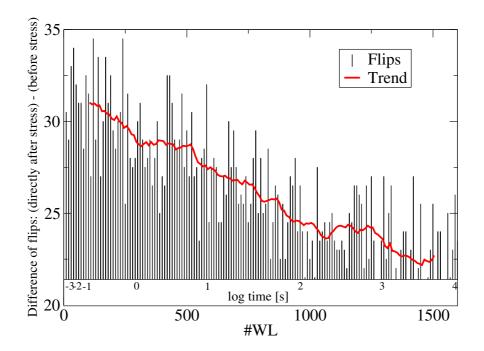

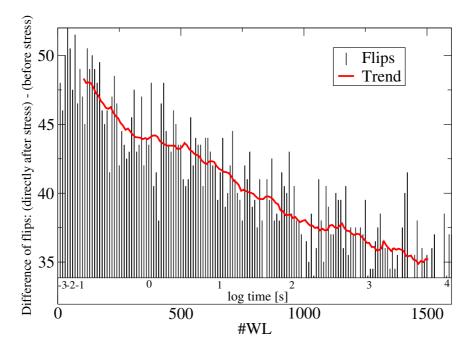

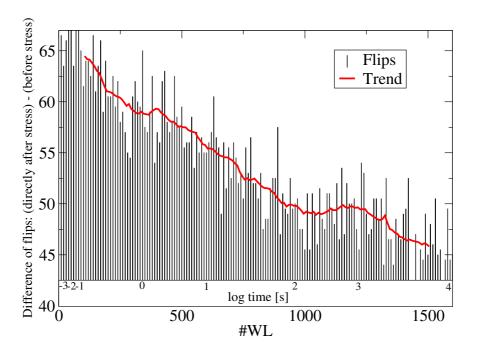

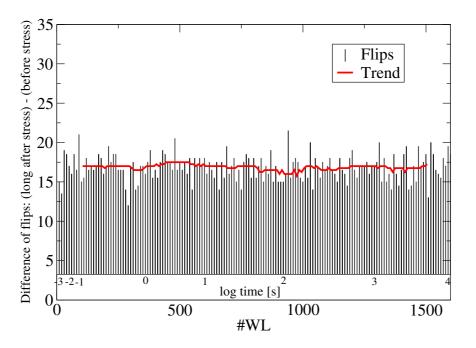

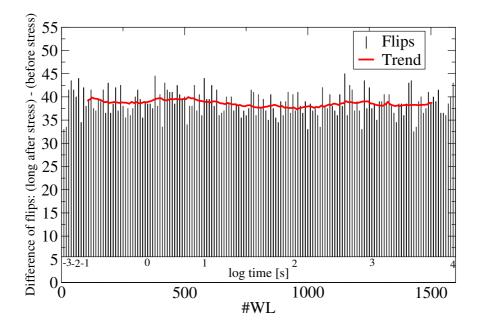

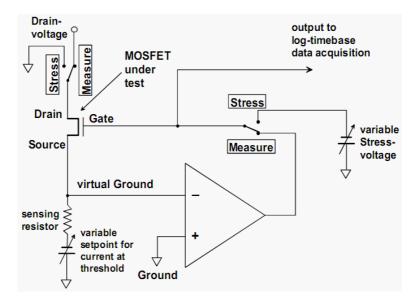

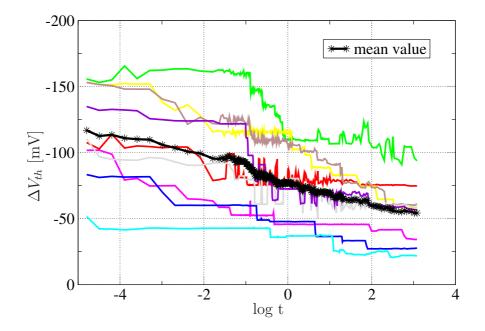

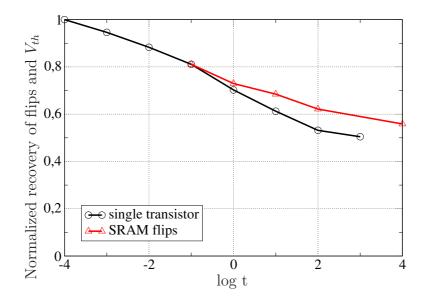

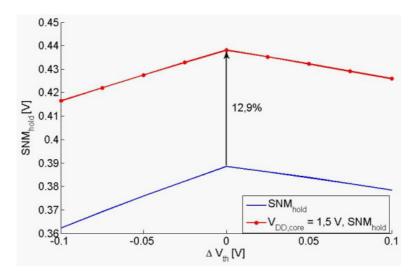

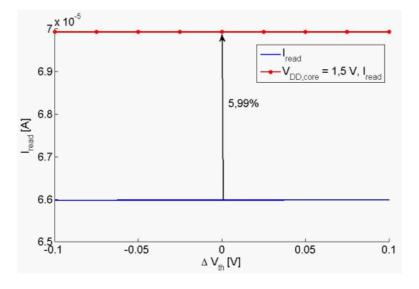

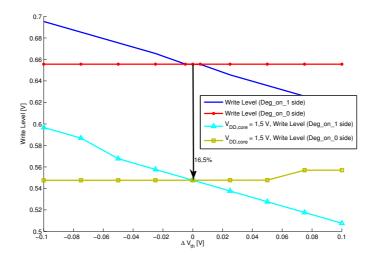

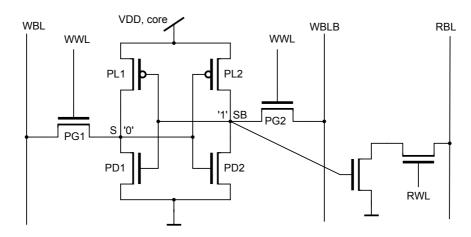

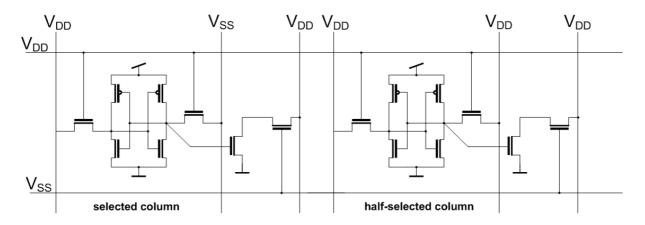

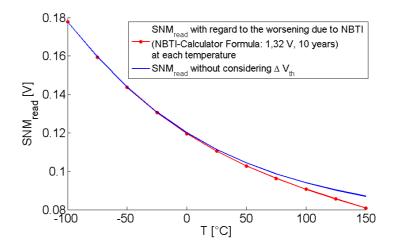

for subthreshold leakage currents in the channel, which causes the NCHCI phenomenon. NCHCI shows a strong dependency on channel length [39] [40]. Even small variations of channel length have high impact on the device lifetime [41].