#

# Technische Universität München Institut für Informatik

# **Doctoral Thesis**

Timing Constraints in Distributed Development of Automotive Real-time Systems

Oliver Scheickl

# Technische Universität München Institut für Informatik

# Timing Constraints in Distributed Development of Automotive Real-time Systems

# **Oliver Scheickl**

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: U

Univ.-Prof. Dr. Alois Knoll

Prüfer der Dissertation:

1. Univ.-Prof. Dr. Dr. h.c. Manfred Broy

2. Univ.-Prof. Dr. Rolf Ernst,

Technische Universität Braunschweig

Die Dissertation wurde am 3. März 2011 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 16. August 2011 angenommen.

ii

### Acknowledgements

This thesis was created during my work as doctoral candidate at BMW Car IT GmbH in Munich. From 2007 to 2010 I worked there on several internal and external projects related to the modeling and analysis of embedded automotive real-time systems. I actively participated in the timing subgroup of AUTOSAR, which developed and released a timing model for the automotive industry's embedded system specification standard.

First and foremost I wish to thank Prof. Manfred Broy for supervising my thesis and for all the fruitful discussions during my time working on it. Further I thank Prof. Rolf Ernst for being the second referee of the thesis and for his helpful feedback.

I am thankful to all of my colleagues at BMW Car IT for an incredibly inspiring working environment and for their kind help and support at all times. I extend my thanks especially to Prof. Harald Heinecke and Michael Rudorfer for guiding my work and for providing me with such a great opportunity in balancing a combination of scientific and industrial work. For their continuous support, countless discussions and finally for reviewing and commenting on my thesis, I am deeply grateful to my colleagues Christoph Ainhauser, Thomas Benedek, Dr. Sebastian Benz, Paul Hoser and especially Dr. Reinhard Stolle, who inspired and motivated me to write a doctoral thesis.

Finally, I thank my parents for their invaluable support throughout my studies and the work on my thesis. All of this has only been possible because of you. iv

### Abstract

The amount of functions that are realized by software is increasing in modern automobiles. Most innovations in the automotive industry are driven by such functions today. Many of these functions, especially safety-relevant functions, must fulfill strict timing constraints. This thesis introduces a new development approach for automotive real-time systems.

Traditionally, the overall vehicle electrical system is designed and integrated by the car manufacturer (OEM). Suppliers actually develop different subsystems in a so-called distributed development process. The OEM specifies the desired functionality, and suppliers develop their subsystem according to its specification. End-to-end car functions are often realized by software components that are distributed over several electronic control units (ECU), which exchange data via communication busses. ECUs and software components are typical subsystems. The control and data paths of functions thus often cross several subsystems, which are typically provided by different suppliers.

The response times of functions, which must fulfill given timing constraints, include execution and transmission times along their control and data paths. In such a distributed development process of distributed automotive real-time systems, OEMs today face a challenging system integration task. First, they must ensure that the combined timing behavior – i.e. execution and transmission times – of all supplied subsystems fulfills all function timing constraints of the system. Second, if a timing constraint is not fulfilled, the OEMs need to know which subsystem causes the problem and how the problem can be solved.

This thesis proposes a solution to that system integration challenge. In our approach, the specifications for the suppliers include requirements for the desired subsystem timing behavior. However, the subsystem timing requirements are not independent from each other. Rather they are derived from the function timing constraints. The timing behavior of a supplied subsystem is reported back to the OEM in a way that abstracts from the underlying implementation details by providing data path-related timing behavior guarantees. By comparing the timing requirements with the reported guarantees of all subsystems, timing problems can be localized and an according reaction in terms of an intelligent modification of the timing requirements can be triggered. In an iterative process the approach tries to find a suitable timing specification for all subsystems, until all function timing constraints are fulfilled.

The process is based on TIMEX, a new timing model for the specification of both function timing constraints and derived subsystem timing requirements. Further, the TIMEX development methodology describes and formalizes an algorithm to derive and iteratively maintain subsystem timing requirements. The benefit of the methodology is that the timing behavior of subsystems can be analyzed independently from each other. Timing problems that cause unfulfilled function timing constraints can be identified in the model. They are then repaired by a structured, systematic redistribution of time budgets between subsystems. vi

### Zusammenfassung

Die Anzahl Software-basierter Funktionen in Fahrzeugen nimmt stetig zu. Viele der Funktionen müssen strikte zeitliche Anforderungen erfüllen. Die Software-Komponenten solcher Funktionen sind zunehmend über kommunizierende Steuergeräte verteilt. Wegen der für die Automobilindustrie typischen verteilten Entwicklung, in der mehrere Zulieferer verschiedene Steuergeräte oder Software-Komponenten liefern, müssen zeitliche Anforderungen während der Entwicklung zwischen dem Automobilhersteller und den Zulieferern koordiniert werden. Diese Arbeit stellt einen neuen Ansatz vor, um zeitliche Anforderungen von Funktionen auf Subsysteme abzubilden und während der Entwicklung Zeitbudgets für Subsysteme zu koordinieren. Basis des Ansatzes ist das in der Arbeit eingeführte Modell für zeitliche Anforderungen TIMEX. Die Regeln zur Abbildung von Funktions- auf Subsystemanforderungen werden mittels Prädikatenlogik formalisiert und deren Anwendung an einer typischen Automobilfunktion demonstriert. viii

# Contents

| 1 | Intr | roduct | ion                                        | 1  |

|---|------|--------|--------------------------------------------|----|

|   | 1.1  | Backg  | round                                      | 1  |

|   | 1.2  | Proble | em Statement                               | 3  |

|   | 1.3  | Soluti | on Outline and Thesis Contributions        | 4  |

|   | 1.4  | Struct | ture of this Thesis                        | 5  |

| 2 | Fun  | ıdameı | ntals                                      | 7  |

|   | 2.1  | Real-t | ime Systems                                | 7  |

|   |      | 2.1.1  | Introduction and Definitions               | 7  |

|   |      | 2.1.2  | Scheduling Concepts and Strategies         | 11 |

|   |      | 2.1.3  | Timing Analysis                            | 13 |

|   |      | 2.1.4  | Time-triggered Systems                     | 16 |

|   |      | 2.1.5  | Event-triggered Systems                    | 20 |

|   | 2.2  | Autor  | notive Embedded Systems                    | 22 |

|   |      | 2.2.1  | Distributed Embedded Real-time System      | 22 |

|   |      | 2.2.2  | Automotive Software Engineering            | 24 |

|   |      | 2.2.3  | Operating Systems and Communication Busses | 25 |

|   | 2.3  | Model  | l-based Development                        | 27 |

|   |      | 2.3.1  | Overview of System Modeling                | 27 |

|   |      | 2.3.2  | Autosar                                    | 28 |

|   |      | 2.3.3  | Timing-augmented System Model              | 29 |

|   | 2.4  | Const  | raint Logic Programming                    | 30 |

| 3 | Bas | ic Cor | cepts Used in this Thesis                           | 33 |

|---|-----|--------|-----------------------------------------------------|----|

|   | 3.1 | Distri | buted Development of Automotive Systems             | 33 |

|   |     | 3.1.1  | Process Roles in Distributed Development            | 33 |

|   |     | 3.1.2  | Collaboration Workflows                             | 35 |

|   |     | 3.1.3  | Role Responsibilities Regarding Timing              | 36 |

|   | 3.2 | Obser  | vable Events and Event Chains                       | 36 |

|   |     | 3.2.1  | Events in Real-time System Literature               | 37 |

|   |     | 3.2.2  | Events in Real-time System Development              | 37 |

|   |     | 3.2.3  | Definition of Observable Events                     | 37 |

|   |     | 3.2.4  | Definition of Event Chains                          | 39 |

|   | 3.3 | Syster | n Architecture Model Used in this Thesis            | 39 |

|   |     | 3.3.1  | System Definition                                   | 39 |

|   |     | 3.3.2  | System Architecture Description Overview            | 40 |

|   |     | 3.3.3  | Functional Architecture Model                       | 44 |

|   |     | 3.3.4  | Logical Software Architecture Model                 | 45 |

|   |     | 3.3.5  | Technical Architecture Model                        | 48 |

|   |     | 3.3.6  | Example System Model                                | 55 |

|   | 3.4 | Obser  | vable Events of the System Model                    | 58 |

|   |     | 3.4.1  | Observable Events of the Functional Architecture    | 59 |

|   |     | 3.4.2  | Observable Events of the Logical Architecture       | 60 |

|   |     | 3.4.3  | Observable Events of the Technical Architecture     | 61 |

|   |     | 3.4.4  | Example for all Observable Events of a System Model | 63 |

|   | 3.5 | Funct  | ion-triggered Timing Constraints                    | 65 |

|   |     | 3.5.1  | Timing Constraints in Real-time Systems Literature  | 65 |

|   |     | 3.5.2  | Definition of Function-triggered Timing Constraints | 69 |

|   |     | 3.5.3  | Function-triggered Timing Constraint Types          | 70 |

|   | 3.6 | Requi  | rements and Guarantees                              | 71 |

|   | 3.7 | Summ   | ary and Comparison of Timing Constraint Types       | 73 |

|   |     | 3.7.1  | Summary of Related Work on Timing Constraints       | 73 |

|   |     | 3.7.2  | Comparison of Constraint Types                      | 74 |

|   |     |         |                                                | Contents   | xi |

|---|-----|---------|------------------------------------------------|------------|----|

| 4 | The | Glob    | al Scheduling Problem                          |            | 75 |

|   | 4.1 | Usage   | of our System Model                            |            | 75 |

|   |     | 4.1.1   | Assumptions                                    |            | 75 |

|   |     | 4.1.2   | Timing Properties                              |            | 77 |

|   |     | 4.1.3   | System Model Example                           |            | 78 |

|   | 4.2 | Timin   | g Constraints                                  |            | 78 |

|   | 4.3 | Globa   | l Scheduling Problem Description               |            | 79 |

|   |     | 4.3.1   | Definition of Global Scheduling                |            | 79 |

|   |     | 4.3.2   | Global Scheduling Steps                        |            | 81 |

|   | 4.4 | Task l  | Mapping and Frame Mapping Approaches           |            | 83 |

|   | 4.5 | Sched   | uling Approaches for Event-triggered Systems   |            | 84 |

|   |     | 4.5.1   | Rate Monotonic Scheduling                      |            | 84 |

|   |     | 4.5.2   | Response Time Calculation                      |            | 85 |

|   |     | 4.5.3   | Deadline Monotonic Scheduling                  |            | 86 |

|   |     | 4.5.4   | Compositional Scheduling Analysis              |            | 87 |

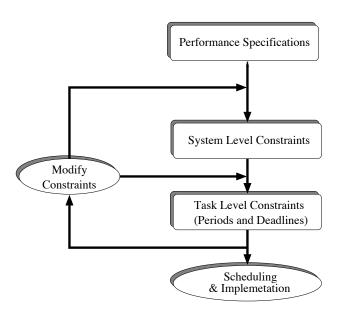

|   |     | 4.5.5   | Generating Intermediate Task Deadlines         |            | 88 |

|   | 4.6 | Sched   | uling Approaches for Time-triggered Systems    |            | 89 |

|   |     | 4.6.1   | Frame Mapping and Scheduling                   |            | 89 |

|   |     | 4.6.2   | Frame Scheduling                               |            | 90 |

|   |     | 4.6.3   | Instruction Precedence Scheduling              |            | 90 |

|   |     | 4.6.4   | System Scheduling of Tasks and Messages .      |            | 91 |

|   |     | 4.6.5   | System Scheduling with Frame Mapping $\ . \ .$ |            | 92 |

|   | 4.7 | Limita  | ations of Related Work                         |            | 92 |

|   |     | 4.7.1   | Derivation of Subsystem Constraints            |            | 92 |

|   |     | 4.7.2   | Visibility of Timing Properties                |            | 93 |

|   |     | 4.7.3   | Consequences of Changes                        |            | 94 |

|   |     | 4.7.4   | Conclusion of the Related Work Analysis        |            | 95 |

| 5 | TIM | iex - A | A new Timing Model for Distributed De          | evelopment | 97 |

|   | 5.1 | Need    | for a new Timing Model                         |            | 97 |

|   |     |         |                                                |            |    |

|   | 5.2 | TIME   | x - Timing Extension                              |

|---|-----|--------|---------------------------------------------------|

|   |     | 5.2.1  | Timing Extension Definition                       |

|   |     | 5.2.2  | TIMEX                                             |

|   | 5.3 | TIME   | x Model Elements Formalization                    |

|   |     | 5.3.1  | TIMEX Example                                     |

|   |     | 5.3.2  | Hand Over Points                                  |

|   |     | 5.3.3  | Function Timing106                                |

|   |     | 5.3.4  | System Timing                                     |

|   |     | 5.3.5  | TIMEX Example Formalization                       |

|   | 5.4 | Consis | stency of a TIMEX Model                           |

|   |     | 5.4.1  | Reasonable Hops                                   |

|   |     | 5.4.2  | Loose Hops                                        |

|   |     | 5.4.3  | Outer Hops                                        |

|   |     | 5.4.4  | Segment Types                                     |

|   |     | 5.4.5  | Segment Sequences                                 |

|   |     | 5.4.6  | Chain Segmentation                                |

|   |     | 5.4.7  | Chain Constraints                                 |

|   | 5.5 | Develo | opment Methodology based on TIMEX123              |

|   |     | 5.5.1  | Define Function Timing                            |

|   |     | 5.5.2  | Develop Deployment Model                          |

|   |     | 5.5.3  | Define System Timing                              |

|   |     | 5.5.4  | Initialize Requirement Types                      |

|   |     | 5.5.5  | Generate Requirement Values                       |

|   |     | 5.5.6  | Generate Communication Model128                   |

|   |     | 5.5.7  | Iterative Steps                                   |

| 6 | Gen | eratin | g Subsystem Requirements in TIMEX with CLP $.131$ |

|   | 6.1 | Requi  | rements and Guarantees in a TIMEX Model           |

|   |     | 6.1.1  | Possible Types of Requirements and Guarantees 131 |

|   |     | 6.1.2  | Assigning the Types to Segments and Hops132       |

|   |     |        |                                                   |

|   |                                               |                          | Contents xiii                                                     |

|---|-----------------------------------------------|--------------------------|-------------------------------------------------------------------|

|   |                                               | 6.1.3                    | Fulfillment of Requirements with Guarantees134                    |

|   | 6.2                                           | Initial                  | lizing Requirement Types                                          |

|   |                                               | 6.2.1                    | Initialization Basics                                             |

|   |                                               | 6.2.2                    | Initialization for Event-triggered Systems                        |

|   |                                               | 6.2.3                    | Initialization for Time-triggered Systems140                      |

|   |                                               | 6.2.4                    | Example                                                           |

|   | 6.3                                           | Gener                    | rating Requirement Values - General Approach145                   |

|   |                                               | 6.3.1                    | Problem Analysis145                                               |

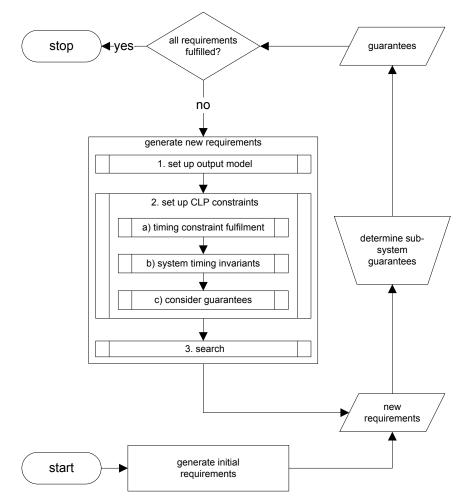

|   |                                               | 6.3.2                    | General Algorithm Description                                     |

|   |                                               | 6.3.3                    | Set up Output Model149                                            |

|   |                                               | 6.3.4                    | System Timing Invariants                                          |

|   | 6.4                                           | Gener                    | rating Requirement Values for Event-Triggered Systems 151         |

|   |                                               | 6.4.1                    | Timing Constraint Fulfillment151                                  |

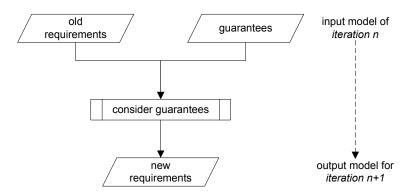

|   |                                               | 6.4.2                    | Consider Guarantees - The Shifting Approach 152                   |

|   |                                               | 6.4.3                    | Search                                                            |

|   | 6.5                                           | Gener                    | rating Requirement Values for Time-Triggered Systems 160          |

|   |                                               | 6.5.1                    | General Rules for Requirement Values in<br>Time-triggered Systems |

|   |                                               | 6.5.2                    | Timing Constraint Fulfillment162                                  |

|   |                                               | 6.5.3                    | Consider Guarantees - The Windowing Approach 164                  |

|   |                                               | 6.5.4                    | Search                                                            |

|   | 6.6                                           | Gener                    | rating a Communication Model175                                   |

| 7 | Evo                                           | lustio                   | <b>n</b>                                                          |

| 1 |                                               |                          |                                                                   |

|   |                                               |                          |                                                                   |

|   | 1.2                                           |                          |                                                                   |

|   |                                               |                          |                                                                   |

|   | 73                                            |                          |                                                                   |

|   | 1.9                                           |                          |                                                                   |

|   |                                               |                          |                                                                   |

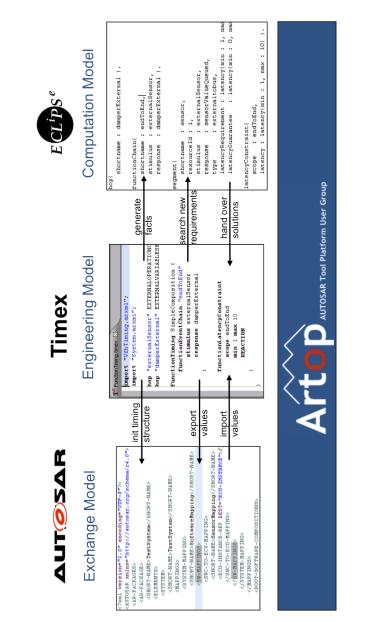

|   | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Applie<br>7.2.1<br>7.2.2 | ardization of the TIMEX Model                                     |

| nclusion                                     |

|----------------------------------------------|

|                                              |

| Outlook                                      |

|                                              |

| bl Prototype                                 |

| Tool Overview                                |

| Textual TIMEX Model Editor197                |

| Timex Visualization                          |

| Requirement and Guarantee Value Table Editor |

|                                              |

# List of Figures

| 1.1  | The increasing complexity of vehicle electrical systems (based on Negele [67]).                                                           | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Structure of this thesis.                                                                                                                 | 6  |

| 2.1  | Hard and soft timing constraints and the relation between<br>their time bounds and the system quality (based on Mächtel<br>[63, page 30]) | 9  |

| 2.2  | The basic task state model according to OSEK [70]                                                                                         | 10 |

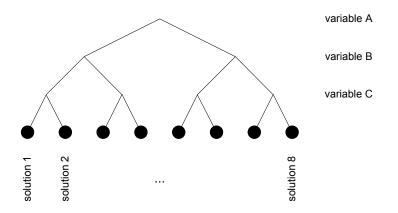

| 2.3  | Representation of a search tree for three boolean variables A, B, and C                                                                   | 31 |

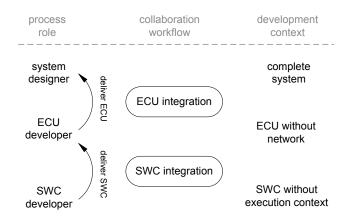

| 3.1  | Roles, collaboration workflows and development contexts in distributed development of automotive real-time systems                        | 35 |

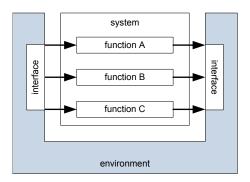

| 3.2  | A system, its interface and the environment                                                                                               | 40 |

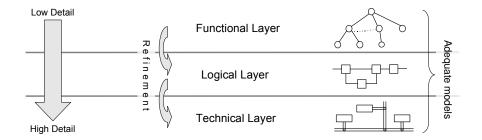

| 3.3  | Three abstraction layers of the system architecture model according to Feilkas et al. [30]                                                | 42 |

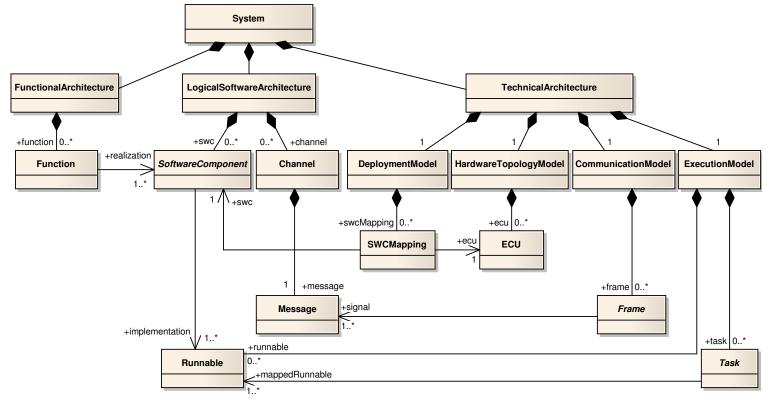

| 3.4  | Overview of the system architecture model used in this thesis                                                                             | 43 |

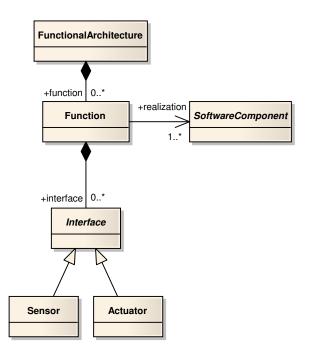

| 3.5  | The functional architecture of the system model                                                                                           | 44 |

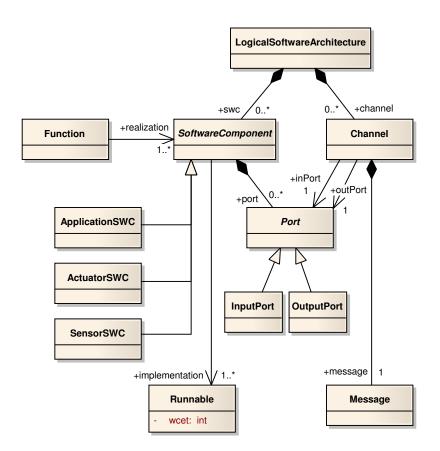

| 3.6  | The logical software architecture of the system model. $\ldots$                                                                           | 46 |

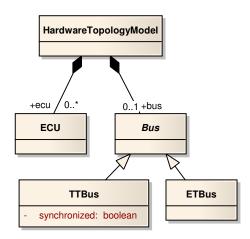

| 3.7  | The technical architecture of the system model consists of four sub-models                                                                | 49 |

| 3.8  | The hardware topology model of the system model                                                                                           | 50 |

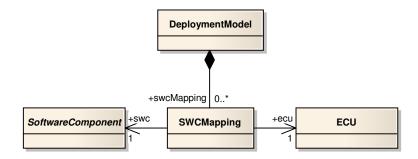

| 3.9  | The deployment model of the system model                                                                                                  | 51 |

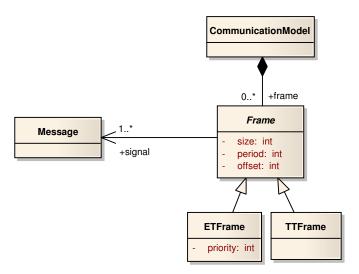

| 3.10 | The communication model of the system model                                                                                               | 52 |

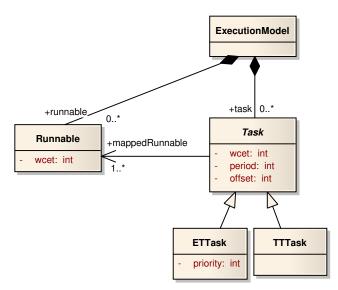

| 3.11 | The execution model of the system model                                                                                                   | 54 |

### List of Figures xvi

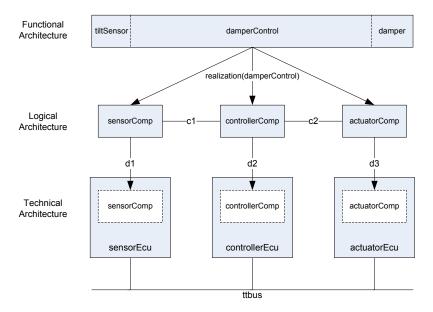

| 3.12 | Visualization of the formally specified system model example 56                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

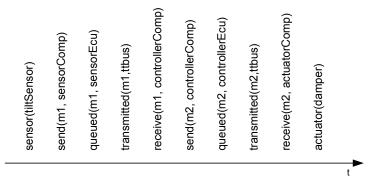

| 3.13 | The temporal order of all observable events of the system model example                                                                                 |

| 3.14 | Constraint types and their relation according to Saksena [79] $68$                                                                                      |

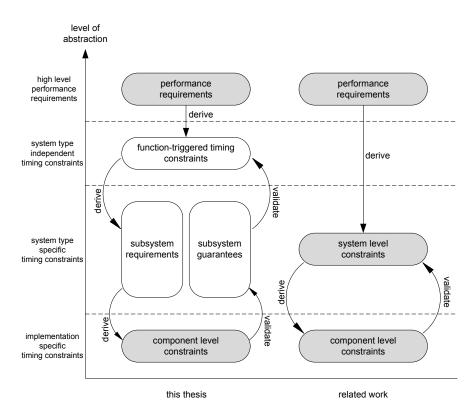

| 3.15 | Comparison of timing constraints in this thesis and in related<br>work                                                                                  |

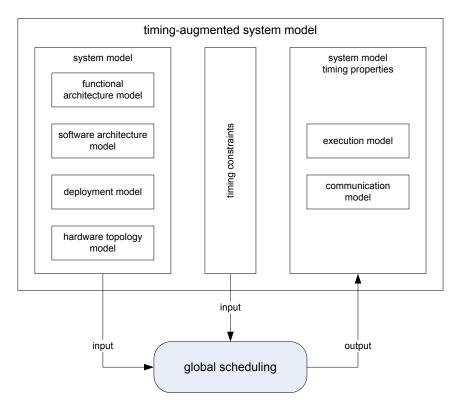

| 4.1  | Timing-augmented system model as input and output of global scheduling                                                                                  |

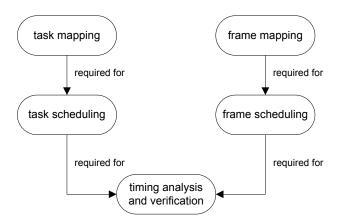

| 4.2  | Dependency of the five global scheduling steps 82                                                                                                       |

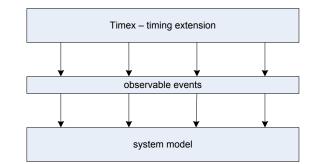

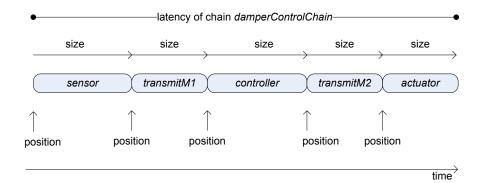

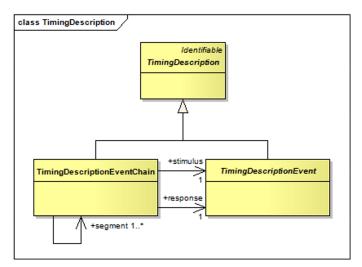

| 5.1  | Observable events as our concept to connect a system model with a timing extension like TIMEX                                                           |

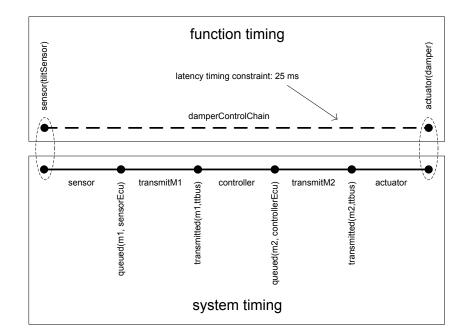

| 5.2  | Timing extension of the example system model using TIMEX on both function level and implementation level104                                             |

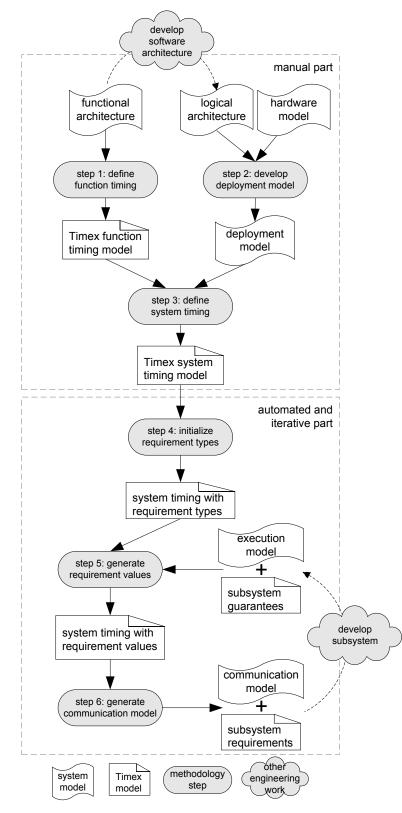

| 5.3  | Methodology for distributed development of automotive real-time systems based on TIMEX and our system model 125                                         |

| 6.1  | Flowchart representing the algorithm to iteratively<br>generate and modify subsystem requirements according to<br>function-triggered timing constraints |

| 6.2  | The input and output of the processing step $consider \ guarantees.148$                                                                                 |

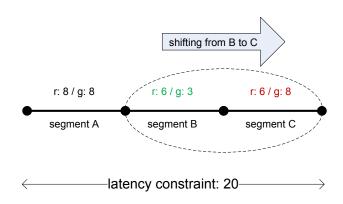

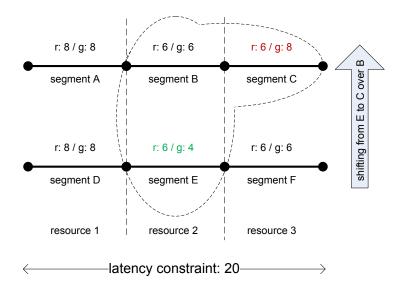

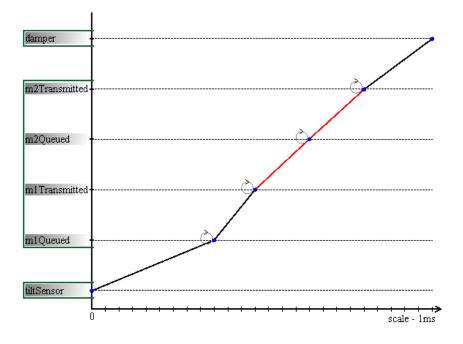

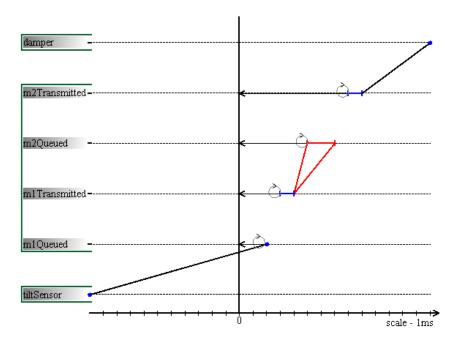

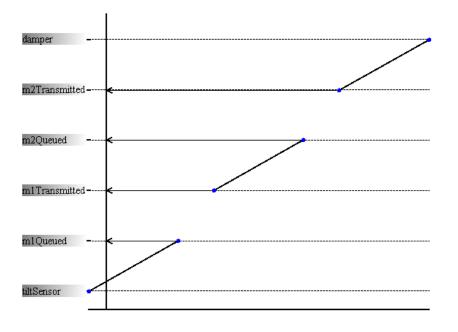

| 6.3  | Example for horizontal shifting                                                                                                                         |

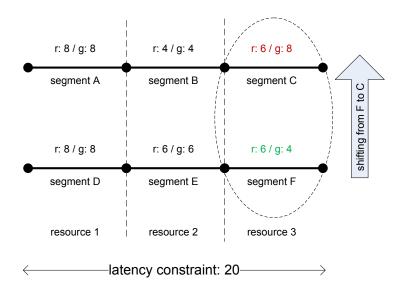

| 6.4  | Example for vertical shifting on the same resource for an iteration $i$ and the subsequent iteration $i+1$ 155                                          |

| 6.5  | Example for diagonal shifting across different resources for an iteration $i$ and the subsequent iteration $i+1$ 156                                    |

| 6.6  | Window representation of the TIMEX example165                                                                                                           |

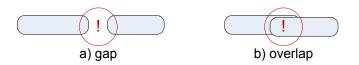

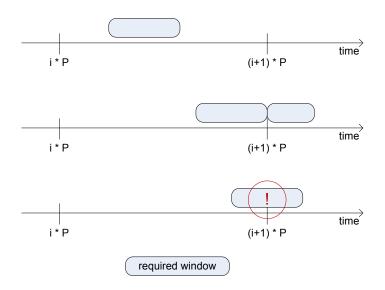

| 6.7  | Unwanted situations of windows: a) gap b) overlap 166                                                                                                   |

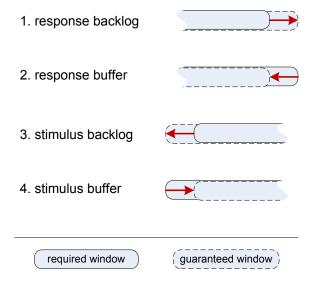

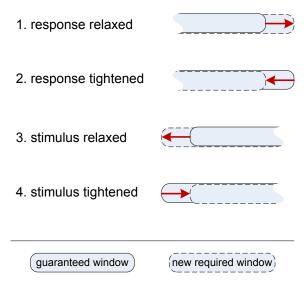

| 6.8  | Four possible situations how the old required window can<br>relate to its guaranteed window167                                                          |

| 6.9  | Four possible situations how the guaranteed window can relate<br>to its new required window                                                             |

| 6.10 | All window requirements must be in a way that a period<br>switch does not occur during a window                                                         |

| 7.1  | AUTOSAR timing model: events and event chains [4]178                                                                                                    |

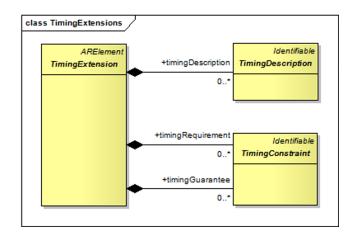

| 7.2 | AUTOSAR timing model: timing requirements and timing guarantees [4]                                |

|-----|----------------------------------------------------------------------------------------------------|

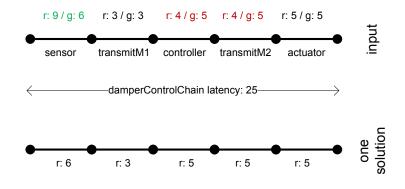

| 7.3 | Example with one solution by horizontal shifting181                                                |

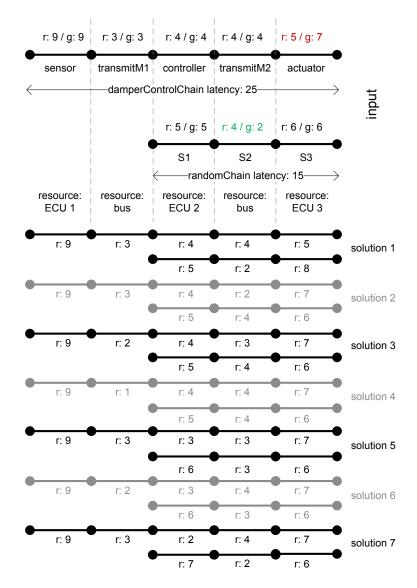

| 7.4 | Example with seven solutions by diagonal shifting. $\dots \dots \dots 182$                         |

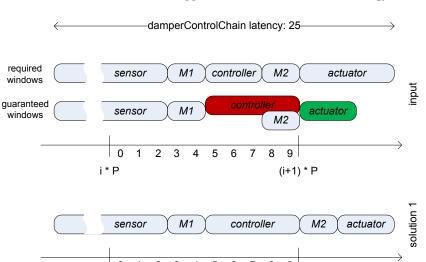

| 7.5 | Example with two solutions by the windowing approach. $\dots \dots 185$                            |

| A.1 | Three different model types of the overall TIMEX tooling196                                        |

| A.2 | Example function timing in the textual TIMEX editor. $\dots \dots 197$                             |

| A.3 | Example system timing in the textual TIMEX editor                                                  |

| A.4 | Visualization of the example TIMEX model for an event-triggered system                             |

| A.5 | Visualization of the example TIMEX model for a time-triggered system                               |

| A.6 | Structural visualization of the example TIMEX model for a time-triggered system                    |

| A.7 | Table editor view of the requirements and guarantees of the      event-triggered example.      201 |

| A.8 | Table editor view of the requirements and guarantees of the time-triggered example.         202    |

# List of Tables

| 3.1  | Categorization of timing constraints in related work                                                                  | 73  |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 4.1  | Frame Packing according to Navet et al. [78, 61]                                                                      | 84  |

| 4.2  | Rate Monotonic Scheduling by Liu and Layland [59]                                                                     | 85  |

| 4.3  | Response time calculation based on Rate Monotonic<br>Scheduling, Joseph and Pandya [51].                              | 86  |

| 4.4  | Deadline Monotonic Scheduling, Audsley et al. [1, 3, 2]                                                               | 86  |

| 4.5  | Compositional Scheduling Analysis according to Richter et al. [74, 49]                                                | 87  |

| 4.6  | Generating intermediate task deadlines according to Gerber<br>et al. [37]                                             | 88  |

| 4.7  | Frame scheduling according to Grenier et al. [38]                                                                     | 89  |

| 4.8  | Message scheduling according to Nossal and Galla [68]                                                                 | 90  |

| 4.9  | Instruction precedence scheduling according to Chung and<br>Dietz [21]                                                | 91  |

| 4.10 | System scheduling according to Schild and Würtz [84]                                                                  | 91  |

| 4.11 | System scheduling according to Ding et al. [24]                                                                       | 92  |

| 4.12 | System scheduling approach addressed by our work                                                                      | 95  |

| 5.1  | Subsystems developed by the different roles in distributed development of automotive systems                          | 98  |

| 6.1  | Possible types of the first and last segment of a function event<br>chain in the two possible collaboration scenarios | 42  |

| 6.2  | Complete example for horizontal shifting for an iteration $i$<br>and the subsequent iteration $i+1$ .                 | 154 |

### List of Tables xx

| 6.3 | Complete example for vertical shifting on the same resource<br>for an iteration $i$ and the subsequent iteration $i+1$   |

|-----|--------------------------------------------------------------------------------------------------------------------------|

| 6.4 | Complete example for vertical shifting on different resources<br>for an iteration $i$ and the subsequent iteration $i+1$ |

| 7.1 | The input values of the windowing approach example                                                                       |

| 7.2 | Solution 1 of the windowing approach example                                                                             |

| 7.3 | Solution 2 of the windowing approach example                                                                             |

## Introduction

### 1.1 Background

Today's automobiles include an increasing number of functions that are realized by electronics and especially by software [8, 14]. These functions are typically provided by interactive distributed real-time systems. The development of these vehicle electrical systems is a complex task mainly due to the following five reasons:

- 1. Software-based car functions are often distributed across the system and can involve several electronic control units (ECUs), sensors, actuators and communication busses for their execution.

- 2. Each ECU can be involved in the realization of many different functions. This leads to a mutual influence of the functions on each ECU.

- 3. Subsystems are often developed by different teams and suppliers. The car manufacturer (OEM, *Original Equipment Manufacturer*) must integrate the subsystems to a fully functioning system.

- 4. The ECUs realize an increasing number of functions. This leads to a higher degree of integration on each ECU.

- 5. The distributed functions in an automobile's real-time system often have to fulfill stringent timing constraints to function properly.

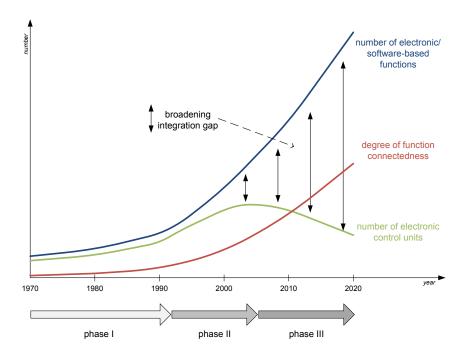

The main drivers for the increasingly challenging development of automotive systems are depicted in Figure 1.1. In the beginning of software and electronics in cars each function was realized by software that was exclusively executed on one dedicated ECU. This era is shown as *phase I* in Figure 1.1. An example for such an early software-based function is the electronic fuel injection. Later, airbags and automatic door openers followed. In the early 1990s, denoted by *phase II*, more functions and ECUs were introduced in the system. The characteristic of this phase is that for the first time several functions were brought onto one ECU and the functions started to become distributed. This increasing *function connectedness* was driven by the introduction of the CAN bus in cars in the early 1990s (Davis et al. [23]).

### 2 1 Introduction

Several years ago, the current *phase III* of automotive system development started, which is characterized by the fact that the number of ECUs is not growing further but even tends to decrease. However, new innovative software-based functions still are continuously introduced. This causes a broadening integration gap on each ECU. From the viewpoint of real-time system development, the increasing complexity results in more and more functions that a) have to fulfill timing constraints, b) are developed by different suppliers and c) highly influence each other's timing behavior in the system.

**Fig. 1.1.** The increasing complexity of vehicle electrical systems (based on Negele [67]).

A continuation of software-based functional innovations, markedly in the regions of safety, comfort and chassis functions, as well as further growth of system design and integration complexity are expected for future automobile generations [14, 47, 13, 87]. The industry as well as the research community is searching for methods and new approaches to cope with the increasing complexity of automotive system design.

A new branch of system design and software engineering has emerged in computer science in the last decade, which is focusing on the challenges of the automotive industry. This new research field called Automotive Software Engineering – see for example Broy et al. [8, 14, 13] or Schäuffele et al. [85] – both brings well-understood methods of traditional software engineering to the automotive domain and develops new solutions especially for the needs that arose with modern automotive system design. Other research groups like Ernst et al. [74, 43, 71] have developed methods for the correct design and analysis of vehicle electrical real-time systems. However, some challenges still remain to be solved as we will explain in the next section. In the automotive industry a new spirit of collaboration has emerged in recent years. To be prepared for the increasing complexity of automotive embedded systems, major car manufacturers and suppliers founded the AUTOSAR development partnership in the year 2003. Today, many car manufacturers, suppliers, software and hardware companies as well as service providers participate in this partnership [33]. The main goal of the initiative is to define a common development methodology and a standardized software architecture for ECUs with well-defined component interfaces [31]. AUTOSAR allows for a standardized formal description of a system model that consists of application software components, communication, basic software and the mapping of software to ECUs. This information can be exchanged between car manufacturers and suppliers if necessary, i.e. between different development teams.

We identified the lack of a timing model in AUTOSAR in [76]. Later, we presented a proposal for such a timing-augmented system model in [82] and ideas for its application in [83], [72] and [81]. Finally, since its version release 4.0 (Dec. 2009), the desired timing behavior can be described with AUTOSAR and exchanged between development teams [4]. The structural system, ECU and component models can be extended to carry a variety of timing constraints. The remaining prime challenge however is, how timing constraints for teams, or subsystems, can be managed during system design. This is the main problem focus of our work, which we state more precisely in the following section.

### 1.2 Problem Statement

As outlined in the previous section, a vehicle electrical system is a so-called real-time system, because many of the functions that are realized with the system have to fulfill timing constraints. As these timing constraints characterize a function and are independent of any function realization using hardware and software, we call them function-triggered timing constraints. The realization of one function is often carried out by several application software components on several ECUs that share data over a common communication bus. We call all these components subsystems. Thus, the realization of one function often involves several subsystems in modern automobiles. The functions are therefore often called distributed functions, because they are "distributed" over several subsystems across the system.

Traditionally, and further driven by the AUTOSAR development partnership, the automotive industry is working in a distributed development process. That is, the subsystems are typically developed by suppliers according to the car manufacturer's specification of the subsystem's desired functionality and timing behavior. The car manufacturer has the role of a system designer and system integrator in that distributed development process. The suppliers usually only exchange information with the car manufacturer and not among each other, although they collaboratively develop the same automotive system. Furthermore, the car manufacturer, who has a view on the entire system, has the knowledge of all function-triggered timing constraints and must ensure their fulfillment after all subsystems have been integrated into the overall system. The suppliers only develop and bear for their subsystem and its timing requirements.

### 4 1 Introduction

As functions often are distributed over several subsystems, different suppliers indirectly collaborate on the development of one function. Function-triggered timing constraints thus can lead to mutual timing dependencies of different suppliers in such a distributed development process.

There are many examples for such timing dependencies between subsystems in both the typical time-triggered and event-triggered networks of automobiles. In a synchronous time-triggered FlexRay [32] network the ECU and bus schedules are tightly coupled if they use the same synchronized time base. A change of the bus schedule influences the data availability for software that is executed on an ECU, which is connected to that network. In an asynchronous event-triggered CAN [50] network all sending ECUs can influence the sending behavior of each other dynamically, because messages with a higher priority delay messages with a lower priority sent by another subsystem. Another example for timing dependencies in both types of networks is the synchronization of the timing behavior of one or more functions. The synchronization of events on different ECUs implies the synchronization of the schedules of different ECUs developed by different suppliers.

Every subsystem developer is responsible for the timing behavior of his particular subsystem. However, as the above explanation clarifies, the subsystem implementations also influence the timing behavior of other subsystems. Thereby they influence the timing behavior of the entire system. Thus, every single subsystem takes part in fulfilling the overall function-triggered timing constraints of the system. As the suppliers of the subsystems do not collaborate with each other, but only with the system designer, the system designer must control the timing behavior of the subsystems by coordinated subsystem timing requirements. These subsystem timing requirements must be derived from the given function-triggered timing constraints of the system.

To tackle this problem, we define a special timing model called TIMEX and an according methodology for distributed development of automotive realtime systems based on function-triggered timing constraints. Furthermore we develop algorithms to iteratively generate timing requirements for the different development teams according to the function-triggered timing constraints.

### 1.3 Solution Outline and Thesis Contributions

To solve the above-mentioned system integration problem for large automotive systems that are developed by several different teams we first propose a new timing model called TIMEX. TIMEX basically serves for two purposes. First, it is used to capture function-triggered timing constraints in a formal way by a so-called *function timing* model. Function timing models are an implementation-independent formalization of function-triggered timing constraints. When it comes to a system implementation, TIMEX provides a formalism to abstract from low-level timing properties of subsystems to a more abstract level to specify subsystem timing requirements. This is called the *system timing* model. Each timing requirement is accompanied by an according timing guarantee, which is provided by the subsystem developer to the system designer (OEM) as a response to the timing requirement. The main goal of the TIMEX model is that the fulfillment of the system-wide function-triggered timing constraints shall be ensured on subsystem level. That means the subsystem timing requirements must be fulfilled by their according timing guarantees. Therefore it is important that the timing requirements have been derived from the function-triggered timing constraints such that the later validation can be performed on subsystem level. To enable this, we formalize timing requirement derivation and modification rules by predicate logic, based on constraint logic programming (CLP) techniques.

The timing requirement derivation rules and the rules for iterative timing budget redistribution for unfulfilled requirements differ for the two main system types of today's automobiles, which are event-triggered and time-triggered systems. Therefore we developed two different formalization approaches, which we also formalized using predicate logic. For event-triggered systems, we developed the *shifting approach*. It basically works by redistributing time budgets iteratively in a TIMEX system timing model by shifting unused time budget either along a data path from one subsystem to another (we call it horizontal shifting), or by shifting unused time budgets on one resource, i.e. an ECU or a communication bus (we call it vertical or diagonal shifting). For time-triggered systems, we developed the *windowing approach*. It is used to define time budgets as time windows according to a TIMEX function timing and move and resize these windows iteratively until all function-triggered timing constraints are fulfilled, according to the fulfillment of subsystem timing requirements by their guarantees. Shifting and window moving are precisely defined reactions to local timing problems that occur when timing requirements of subsystems are not fulfilled by their timing guarantees.

The TIMEX model and its according methodology proposed in this thesis are beneficial for automotive system development due to the following reasons. The model is suited as exchange format between OEMs and suppliers in distributed development. Its abstraction technique enables the sharing of timing constraint and behavior information, without revealing implementation details, which are considered as intellectual property of the suppliers. The reasoning about the fulfillment of function-triggered timing constraints can be performed on this abstraction level by explicitly considering subsystem boarders. The iterative subsystem timing requirement – or time budget – derivation, which we formalized by the shifting and windowing approach, allows for a systematic solving of local timing problems of subsystems.

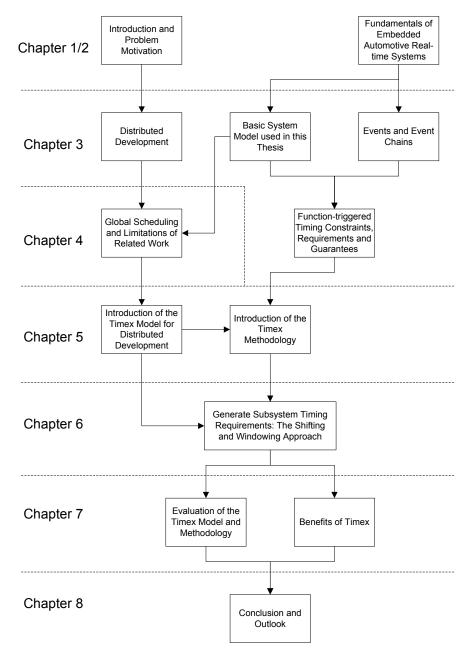

### 1.4 Structure of this Thesis

Figure 1.2 shows the organization of this thesis as a flow chart. The main topics and contributions are displayed as rectangles that are grouped by the thesis chapters in which they are discussed or presented. Arrows indicate dependencies between these topics.

In Chapter 2 we describe the fundamentals for this thesis that are necessary to understand our work, such as an introduction to the automotive domain and real-time systems. We introduce our main thesis concepts and definitions (e.g. function-triggered timing constraints, our system model) in Chapter 3.

### 6 1 Introduction

In Chapter 4 we describe related work in the area of embedded real-time systems and analyze its limitations. Our TIMEX model and methodology, which we use to overcome these limitations, are introduced in Chapter 5. We provide an informal description as well as a predicate logic formalization for both the shifting and the windowing approach in Chapter 6. An evaluation of the TIMEX model and methodology is provided in Chapter 7. Finally, we conclude this thesis in Chapter 8.

Fig. 1.2. Structure of this thesis.

# Fundamentals

This chapter provides the fundamentals of real-time systems theory and practice. Further we introduce the reader to the automotive systems domain and some techniques that we use in our work, such as model-based development and constraint logic programming.

### 2.1 Real-time Systems

In this section we provide an overview of real-time system theory. We make some basic assumptions and definitions for our thesis and explain the general concepts of such systems.

Throughout this section we make some references to other publications to confirm our statements. However, the reader finds surveys of related work also in other chapters. We give an overview of related work regarding types of timing constraints in Section 3.5.1. Our survey of scheduling and timing analysis approaches can be found in Chapter 4, where we explain the so-called *global scheduling problem*.

### 2.1.1 Introduction and Definitions

### Real-time Systems

The correctness of usual computer systems basically is defined by the correctness of the calculations, or operations that these systems perform. In real-time systems additionally the timeliness of such operations is important for the overall correctness.

**Definition 2.1.** A system is called a real-time system if the overall correctness of an operation provided by the system depends not only upon the logical correctness of its operations by providing the correct output values, but also it depends upon the time in which the output is provided. 8 2 Fundamentals

Real-time systems can be found in many different areas of our everyday life. The focus of this thesis however is on real-time systems in automobiles. The concepts though are the same for other real-time system domains as well. Examples for other domains are avionics, industrial automation, medical engineering, consumer electronics, and many more. The magnitude of time that is relevant in a real-time system, i. e. the time duration after which some action or reaction is expected, varies and depends on the domain. In vehicle electrical systems the magnitude typically is milliseconds or even microseconds. Other domains could also have seconds, minutes or even days as their temporal magnitude.

### **Timing Constraints**

According to Definition 2.1 real-time systems have to provide correct output values for given input values within certain time bounds. This time bounds can be manifold. We call such time bounds timing constraints.

**Definition 2.2.** A timing constraint is a time bound that has to be fulfilled by a real-time system to function correctly.

To evaluate the correctness of a real-time system, a clear specification of its timing constraints is mandatory.

Many different semantics and levels of abstraction to express timing constraints exist in practice. We provide a comprehensive survey of timing constraints in real-time systems literature in Section 3.5.1.

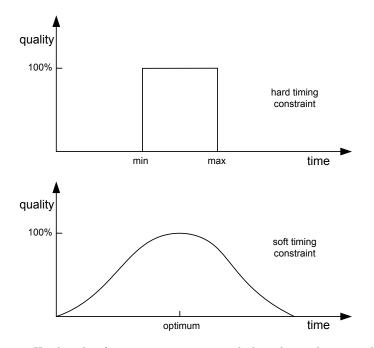

In literature timing constraints are often divided into two classes, called *hard* and *soft* timing constraints. Again, many definitions of hard and soft timing constraints exist in literature. However, they basically have the same meaning. Liu [60] defines hard and soft timing constraints as follows.

**Definition 2.3.** A timing constraint is called hard if it must always be fulfilled by the real-time system. A timing constraint is called soft if it must not necessarily be fulfilled by the real-time system, but its fulfillment increases the system's quality.

The relation of hard and soft timing constraints and the quality of the system is depicted in Figure 2.1. A hard timing constraint must necessarily fulfill its time bounds within a certain tolerance, indicated by the *min* and *max* values on the time line. When a hard timing constraint is not fulfilled the system's quality drops to null. A soft timing constraint can have a specific influence on the quality, depending on the fulfillment of the time bound.

Hard timing constraints can typically be found in safety-relevant systems, where non-fulfillment can cause severe damage to the system itself, its users or its environment. In a car for example the chassis control can be classified as such kind of system. Soft timing constraints can be found in systems, where non-fulfillment "only" leads to a reduced quality, but no severe consequences. Often, body electronics have soft timing constraints in a car.

Fig. 2.1. Hard and soft timing constraints and the relation between their time bounds and the system quality (based on Mächtel [63, page 30]).

**Assumption 2.1** In this work we assume that all timing constraints are hard timing constraints. The real-time system, in our case the vehicle electrical system, must always fulfill all timing constraints.

### Tasks and Frames

So far we defined real-time systems rather abstract as systems, which perform operations under certain timing constraints. In the automotive context (as well as other contexts) the system can be divided in two types of subsystems, namely processors and busses. The subsystems share similar concepts but have a different terminology. Basically, in both kinds of subsystems there is a shared resource. The shared resource either is a processor or a communication bus. In both cases special *entities* concurrently compete for the resource.

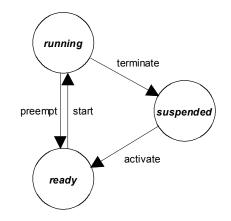

On a processor these entities are typically called tasks. The processor executes tasks. Thereby they probably have to fulfill timing constraints. A single processor can always only execute just one task at the same time. The automotive real-time operating system standard OSEK [70] defines a standard state model for tasks, which is depicted in Figure 2.2. We will refer to task states in this thesis according to OSEK's standard state model. A task is *suspended* when its execution has finished and no subsequent execution is currently required. When a task is activated it changes its state to *ready*. When it is started, i. e. during its actual execution on the processor, its state is *running*. While a task is preempted as described in Section 2.1.2 its state changes from *running* back to *ready* in the meantime. After termination the task state again is *suspended*.

10 2 Fundamentals

Fig. 2.2. The basic task state model according to OSEK [70].

On a communication bus the entities that concurrently compete for the resource are typically called frames. Frames are transmitted over the communication bus and have one sender and one or more receivers. Again, the transmission probably has to fulfill timing constraints. A communication bus can only transmit one frame at the same time. Basically, the task state model of Figure 2.2 also fits for frames, except that frames cannot be interrupted, or preempted, once they are currently transmitted, i. e. *running* according to OSEK's terminology for task states.

### Scheduling

The concept of task scheduling and frame scheduling in general is not only applied in real-time systems. Rather, scheduling is performed in every computer system, in which several processes compete with each other for a common resource. For example, every personal computer performs scheduling to handle several concurrent applications. In real-time systems though scheduling exceedingly attracts the researcher's attention, because it highly influences the fulfillment of the system's timing constraints.

**Definition 2.4.** Scheduling is performed by an operating system to sequence the execution of several concurrently activated tasks that are ready to be executed. The processor can execute only one of these tasks. In the context of communication, scheduling is the sequencing of several concurrently active frame transmissions, where just one frame can actually be transmitted at once.

In a real-time operating system, scheduling is actually carried out by a scheduler, which is part of the operating system. In the case of a real-time communication network, the scheduler is part of the communication controller. The dispatcher is also a part of an operating system. The dispatcher starts and stops tasks that have been chosen by the scheduler to be started or preempted.

### 2.1.2 Scheduling Concepts and Strategies

In general there exist several concepts and strategies that a scheduler can be based on in its decision algorithm. Some of the described concepts and strategies can be applied to processor scheduling as well as bus scheduling. To emphasize this, we explain each strategy for both resource types, if possible. The list we provide here is not complete but contains the concepts that are important for this thesis.

### Time-triggering and Event-triggering

For embedded systems (see Definition 2.2.1), which are discussed in this thesis, there exist two main scheduling strategies. The first one is time-triggering, which we explain in Section 2.1.4. The second and very different strategy is event-triggering, which we explain in Section 2.1.5. Event-triggering and timetriggering are concepts that affect the whole real-time system development, analysis and runtime behavior. All these aspects are investigated in the following sections. For this thesis both strategies are important. Today's automotive functions still rely on both strategies. Some functions fit for event-triggering, others for time-triggering. This leads to heterogeneous systems in cars.

All techniques we investigate for both of these strategies assume that all scheduling entities like tasks and frames are known in advance and static. This assumption is appropriate for vehicle electrical systems as well as other embedded system domains. Other strategies of course also can deal with arbitrary task sets. These so-called online scheduling strategies are typical for PC systems. In Section 2.1.2 we explain an example of such an online scheduling strategy.

So-called hybrid systems combine time-triggered and event-triggered scheduling concepts. For practical applications this is a very convenient way to benefit from the advantages of both system types. Hybrid systems are not considered in this thesis. Our work concentrates on either purely time-triggered or purely event-triggered systems.

### Preemption

Scheduling strategies can be divided into preemptive and non-preemptive strategies. In a preemptive scheduling strategy a running task can be interrupted during its execution. This happens, if another task wants to run and thereby would occupy the same resource at the same time and that task is – for whatever reason, mostly due to a higher priority – selected to run by the scheduler. In the non-preemptive case a task finishes its execution once it is running. It can usually not be interrupted by another task.

The reason why the above explanation explicitly focuses on tasks is that the preemption concept only fits for scheduling of tasks on processors. In a communication network usually a frame transmission cannot be interrupted once it was started. That is, frame scheduling by default is non-preemptive.

### 12 2 Fundamentals

### First in first out

A very simple scheduling strategy for processes is scheduling by the order of the activation of the tasks. In this case the scheduler maintains a simple queue of currently activated tasks that are in the ready state (see Figure 2.2). A newly activated task is added to the end of that queue. When the currently running task finished its execution and terminates, the task on top of the queue is selected to run. This strategy is often referred to as *first in first out* strategy, or short FIFO.

In a communication network the above-mentioned queue usually can only be maintained locally on one connected communication controller. The queue then contains all frames to be sent by this single local controller. A FIFO strategy is only applied to a local frame set by one controller.

### Priorities

Priority-based scheduling is a widely used scheduling strategy for both processors and communication networks that follow the event-triggered paradigm. In this strategy, the scheduled entities are characterized by a *priority* attribute. Based on the priorities of all currently activated scheduled entities, the scheduler selects the one with the highest priority and allows it to access the resource. Eventually, an entity with lower priority is displaced, or preempted as described above. If more than one entities with the same priority are active, additionally a FIFO strategy (or any other, for example also random selection) can be applied by the scheduler.

An additional differentiation can be made for priority-based scheduling strategies. The priorities can either be assigned before or during system runtime. In the former case the strategy is referred to as *fixed priority scheduling*. Priority assignment then is engineering work and part of the system development phase. Researchers have studied many priority assignment strategies. We look into some important strategies of that kind in Section 4.5. The latter case is called *dynamic priority assignment* and is performed by the scheduler itself. The scheduler therefore needs some kind of priority assignment algorithm that is executed at runtime. Those are also called *online scheduling algorithms*. This causes additional runtime scheduling overhead compared to fixed priority scheduling.

An example for such an online scheduling algorithm is the *Earliest Deadline First* scheduling (short EDF, see for example [20, 18, 25, 96]). The scheduler in this case always selects the task with the closest completion deadline for execution. The selection is performed every time a task is activated or finishes its execution. As online scheduling is not common in the automotive domain, such strategies are not further mentioned or investigated in this thesis. At this point EDF is solely mentioned as one online scheduling example.

### Time Slots

All scheduling concepts and strategies mentioned above are only needed if several scheduling entities want to claim the shared resource at the same time. Time slot scheduling however is a strategy that is used to avoid concurrent execution of tasks or concurrent transmission of communication frames. In this case, all scheduling entities are actually scheduled before runtime, i. e. they are scheduled *statically* instead of *dynamically*. Therefore, so-called time slots are defined for their execution or transmission, which must not be exceeded. In a pure time slot scheduling requires an absolute time base on the resource to activate and terminate tasks or frames at the right time. The remaining job of the actual scheduler is to monitor that time slots are not exceeded. The task activation or frame transmission in time slot scheduling is done by the dispatcher according to a so-called *schedule table*.

**Definition 2.5.** In a time-triggered system a schedule table is used to precisely describe at which point in time according to the absolute time base which action is performed. Actions to be performed are the activation and termination of tasks and the transmission of frames on a bus.

In practice often additionally priority based scheduling must be performed for entities, which have no assigned time slot. This concept is used for example in hybrid systems, which we already mentioned in Section 2.1.2.

### 2.1.3 Timing Analysis

### **Timing Behavior**

A real-time system has a specific dynamic behavior that depends on its implementation. The dynamic behavior can be observed at system runtime or predicted using an appropriate model of the system (see Section 2.3).

The entire system implementation in our understanding consists of the following parts:

- the system's concrete software implementation, basically consisting of application software

- the hardware topology that executes the software, consisting of ECUs and busses

- a mapping of the software to the hardware (which processor executes which part of the software organized as tasks)

- and especially the system's timing properties, i. e. all configuration parameters like task schedules and bus schedules

### 14 2 Fundamentals

Timing properties are all configuration parameters that influence the scheduling effects of a real-time system. The available timing properties depend on the real-time system type and its scheduling strategy, i. e. event-triggering or time-triggering. During runtime, these timing properties influence the system's so-called *timing behavior*. The timing behavior can be observed at runtime. However, if the real-time system is represented by an appropriate model, its timing behavior can even be determined before runtime based on that model. Timing properties are then captured and collected in a model, usually along with the other system implementation parts listed above. We define such a model as a *timing-augmented system model* in Section 2.3.3.

Besides the functional behavior, especially a system's timing behavior is part of the above-mentioned dynamic behavior. The timing behavior is the most important part in the context of our work.

As mentioned before, a system model can be used to analyze the timing behavior before runtime, i. e. without an actual system implementation. This is done using so-called timing analysis methods.

**Definition 2.6.** Timing analysis is the method of determining the expected runtime timing behavior of a real-time system. Timing analysis can be performed using an appropriate model of the system.

Especially in the context of event-triggered real-time systems timing analysis is often also called *schedulability analysis*.

Note that timing analysis is typically carried out using an appropriate model of the real-time system. The model is analyzed statically, i. e. without actually running the system. The principles of model-based development are discussed in Section 2.3. In this thesis we assume model-based timing analysis methods to be used to determine the timing behavior. As we show in Chapter 4, many such model-based analysis approaches exist in literature.

Other methods to gather and analyze a system's timing behavior are:

- simulation, i.e. actually executing the model of a system and observing the behavior

- runtime testing and monitoring, i.e. executing the real system itself (not a model) and observing the behavior

Both simulation and runtime testing are not considered in this thesis.

According to Definition 2.1, real-time systems usually have to meet timing constraints additionally to other functional requirements. The correctness of the functional behavior is verified using well-established methods known from software engineering, such as software tests. However, for real-time systems especially the fulfillment of its timing constraints is important and must be verified. Timing analysis is a means to timing constraint verification. Usually timing analysis is performed to verify the fulfillment of its timing constraints. Besides that, timing analysis can also be used to determine intermediate timing properties. An example for such an intermediate timing property is the so-called *worst* case response time (WCRT) of a task or frame (see Section 4.5.2). Another example is the latency – or WCRT – of a data path through the system, like the path from a sensor that produces some data to an actuator.

# **Timing Analysis Areas**

In this section we further refine the term timing analysis to several subareas. According to Montag et al. [65] timing analysis consists of the following subareas:

- Worst case execution time analysis

- ECU schedulability analysis

- System schedulability analysis

The worst case execution time (short WCET) of a task is the time it takes on a specific processor to execute the task without interruption. The determination of a task's WCET can be performed using different methods of *worst case execution time analysis*. In contrast to simple runtime measuring methods, static WCET analysis promises safe upper bounds. These methods analyze the WCET based on two main factors, namely the task's internal control flow and the hardware it is executed on. A lot of work exists in this area. For example, Montag et al. [65] present a tool for static analysis based on hardware models of the processors. Tavares et al. [91] present a method to express a WCET independently from a certain hardware and to map it onto a concrete hardware with a concrete WCET later. The WCET is the most basic timing property of a task and the basis of all other timing analysis methods.

Assumption 2.2 In this work we assume that all worst case execution times are given input and do not change. Worst case execution times are a timing property of tasks or of runnables (runnables are software containers that are mapped to tasks, see Section 3.3).

The other two areas of timing analysis mentioned above correspond to the classification made by Richter [73]. In his work, these two analysis areas are called component scheduling analysis and system scheduling analysis. They basically have the same meaning as in the definition of Montag et al. [65].

Component analysis focuses on one individually scheduled component, which is either a processor or a communication bus. Montag et al. neglect timing analysis for a communication bus as single component. In the work of Montag et al. , communication-related timing analysis is considered as part of the system timing analysis. According to Richter and other researchers however, component analysis concepts often match for both types of components. The models in use are very similar and just depend on the specific scheduling strategy as discussed in Section 2.1.2.

One basic property of a set of periodic tasks or frames is the *resource utiliza*tion. Liu and Layland [59] define resource utilization as follows. Given a set of n strict periodic tasks, let  $C_i$  be the constant WCET of task i and  $P_i$  the period of task i. Accordingly, if applied for a set of frames,  $C_i$  is the transmission time for frame i and  $P_i$  is its period. The resource utilization is defined by Equation (2.1).

$$U = \sum_{i=1}^{n} C_i / P_i \tag{2.1}$$

The utilization of a component must be lower or equal than 1. Otherwise no schedule can exist that guarantees a successful execution of the task set, because the processor is overloaded, regardless of the execution order of the tasks.

System timing analysis is used to analyze the timing behavior of a complete system that consists of single components, such as processors and busses. System timing analysis introduces some additional challenges. Systems often perform distributed functionality. This leads to complex interferences and dependencies of the timing behavior of the single components. Different approaches to system timing analysis exist. We will look into some approaches in Chapter 4.

# 2.1.4 Time-triggered Systems

One of the two main paradigms for real-time systems is time-triggering. Comprehensive studies of such systems have been provided by Kopetz et al. [54, 28]. The concepts can be applied to both processors and communication busses. In a pure time-triggered system all actions are triggered solely by the progression of time. Therefore the complete execution and transmission schedules are defined before runtime to perform a time slot scheduling as explained in Section 2.1.2. The resulting schedule table is cyclically processed and used to trigger transmission or execution based on an absolute time line. Triggering cannot be influenced at runtime by the system itself or by any dynamic application behavior.

In a pure time-triggered operating system each task has a pre-defined absolute time window and a period. It is executed strictly cyclic with that period in that time window. The task is guaranteed not to be interrupted during its execution, at least within its assigned time window.

In a time-triggered communication schedule, each frame on the bus also has a fixed period and a transmission time and can only be transmitted by the sending component at these predefined time instances cyclically. All receiving components share the same schedule table and can catch the transmitted data at the correct time.

#### Scheduling of Time-triggered Systems

As already indicated in Section 2.1.2, scheduling of a time-triggered system as defined in Definition 2.4 is rather trivial. In the case of time-triggering there is no runtime scheduler responsible to make the right decisions. Instead it just has to follow a pre-defined schedule table (see Definition 2.5) that indicates when which task must be activated or terminated. In fact, the work to establish and maintain such a schedule table has to be done before runtime by engineering work. Because of that, the term *scheduling* in the context of time-triggered systems often actually is used to describe the process of creating such a schedule table. This understanding of scheduling differs from the one of Definition 2.4.

Creating a schedule table can be performed manually by an engineer or by using algorithms that compute schedule tables. The process of setting up a schedule table is often called scheduling as described above. Furthermore, *schedule generation* denotes time-triggered scheduling if it is realized by algorithms.

**Definition 2.7.** The creation of a schedule table for a time-triggered system using algorithms instead of manual engineering work is called schedule generation.

A schedule table is often also just called schedule. Such a schedule is a set of tasks in case of a processor schedule, or a set of frames in case of a bus schedule. In both cases each of these entities virtually has an individual *window* for its execution. Each window has the following timing properties that completely describe a time-triggered schedule:

- Each window has a certain **window size**. In case of a processor schedule the window size should be at least the task's WCET to prevent the task from exceeding its execution window even in the worst case. In case of a bus schedule the window size is the maximum frame length. In typical time-triggered communication networks the maximum frame length is a constant. This means all transmission windows have the same size.

- The **period** defines the exact cycle time of every window. A task is executed cyclically with that period. A frame is transmitted cyclically with that period.

- Additionally, each window has an **offset**. This timing property determines the absolute position in time of the execution window. To apply offsets, the already mentioned absolute time base is mandatory for time-triggered systems.

Note that we make the following Assumption 2.3 for the relation of period and offset values.

Assumption 2.3 We assume that in a time-triggered system the offset of a task, frame, event, or any other timing entity cannot be greater than the entity's period. The offset refers to a time instance within the entity's period.

A schedule as defined above only lists the timing properties for each window. At runtime a time-triggered system repeats that schedule again and again. Therefore a repetition period must be defined per system. We call this period the overall *system cycle*.

**Definition 2.8.** The system cycle is the overall repetition period of a timetriggered system after which the entire schedule is repeated.

In fact, setting up such a static schedule table before runtime for a time-triggered system -i.e. defining the above-mentioned three timing properties for each window -is not trivial.

There are usually many boundary conditions that must be met by a valid schedule. In the following we list some of the most important conditions for time-triggered schedules:

- Each reserved schedule window appears periodically in any case, because of the system cycle. So, each task must be executed periodically and each frame must be transmitted periodically. The period of a task or frame must be an integer divisor of the system cycle. For example, if the system cycle is 300 milliseconds, a correct task or frame period is 100 ms, which conforms to a divisor of 3.

- Often time-triggered systems have a *base cycle*, which narrows the possible periods for tasks and frames by defining the base cycle as their minimum period. The periods must be an integer multiple of the base cycle.

- Only one task can be executed by a processor and only one frame can be transmitted by the bus at once. That means the schedule must ensure that there are no overlaps of tasks on a processor and no concurrent frame transmissions on the bus. This means that the offsets of all tasks or frames must be chosen correctly.

- The no-overlap-condition also imposes additional limitations on the periods used in a schedule. To have a valid schedule it is not only sufficient that the periods are integer divisors and multiples as already described. Additionally all periods of a schedule must be in a way, that they do not inevitably cause overlaps regardless of the according offsets. For example consider a system cycle of 35 and a base cycle of 1. The periods 5 and 7 that might be used for two tasks are both integer multiple of 1 and integer divisor of 35. Though there exists no offset combination without a clash of two particular instances of two tasks. The periods of all tasks or frames of a schedule must be what we call *harmonic* (see Definition 2.9).

- Static schedules are not really flexible with respect to changes of any schedule properties. That especially means that all task WCETs and frame sizes must already be known and must not vary. Variation can cause the schedule to become invalid, because for example a WCET increase can lead to an overlap with another task. This would imply a redesign of the schedule. The same applies for changed to offsets and periods, as such changes automatically also affect other tasks or frames.

- The processor and bus utilization according to Equation (2.1) must be lower or equal than 1 for every set of periodic tasks and frames on a processor or bus. The higher the utilization is, the more difficult it is to find a valid schedule for the task or frame set.

- Depending on the application, the system and thus the schedules must ensure the fulfillment of timing constraints additionally to all basic conditions mentioned so far. This is the most challenging condition that must be met by a schedule table. How this can be achieved is part of our work and intensively discussed later.

**Definition 2.9.** A task or frame set has harmonic periods, if all periods are an integer multiple of the smallest period.

Despite, or even because of its determinism, time-triggered scheduling has some disadvantages. First, static schedules can cause a waste of processor or bus resource capacities. This can happen due to an oversize execution window for tasks or frames already at design time. The cause for this can be an initially overestimated WCET of tasks, for example. The waste can also happen when a task or frame does not need the complete assigned time window in a specific execution instance at runtime. The wasted resource time cannot be used dynamically, at least in a pure time-triggered system. The second major drawback of time-triggered scheduling is its inflexibility with respect to changes as already indicated in the list above. If a schedule table gets corrupted because it contains overlaps of execution or transmission windows due to a change of a WCET or an offset, the schedule table often requires a complete redesign.